TPS389C03-Q1 SNVSCC2E - NOVEMBER 2022 - REVISED MAY 2024

# TPS389C03-Q1 Multichannel Overvoltage and Undervoltage I<sup>2</sup>C Programmable Voltage Supervisor and Monitor with Q&A Watchdog

#### 1 Features

- ASIL-D functional safety-compliant

- Documentation to aid ISO 26262 system design

- Systematic capability up to ASIL D

- Hardware capability up to ASIL D

- AEC-Q100 qualified with the following results:

- Device temperature grade 1: –40°C to +125°C

- Device HBM ESD classification level 2

- Device CDM ESD classification level C7B

- Q&A Watchdog to monitor SoC software operation

- Programmable OPEN/CLOSE watchdog timing through I<sup>2</sup>C (1ms to 864ms)

- Start-up delay for SoC boot up initialization (2ms to 3.46s)

- Programmable maximum violation count (up to 7) before WDO assertion

- Watchdog disable pin (WDE)

- Monitor state-of-the art SOCs

- Three channels with three remote sense (TPS389C03-Q1)

- Input voltage range: 2.6V to 5.5V

- Undervoltage lockout (UVLO): 2.6V

- High threshold accuracy:

- ± 5mV (-40°C to +125°C)

- Built-in ADC for voltage readouts

- Fixed window threshold levels

- 5mV steps from 0.2V to 1.475V

- 20mV steps in other ranges

- Miniature solution and minimal component cost

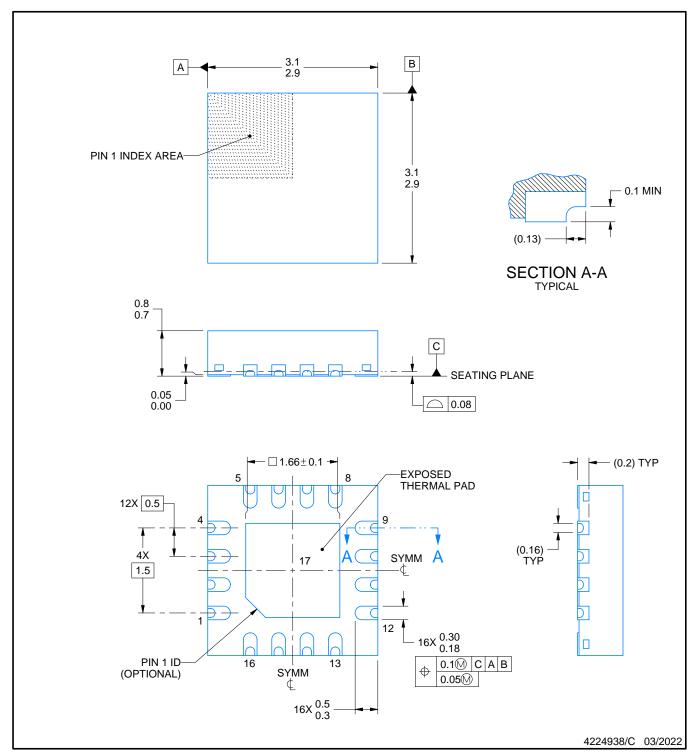

- 3mm × 3mm QFN package

- User adjustable voltage threshold levels via I<sup>2</sup>C

- User adjustable glitch immunity and hysteresis levels via I<sup>2</sup>C

- Designed for safety applications

- Error Signal Monitoring (ESM)

- Programmable ESM delay via I<sup>2</sup>C (1ms to 864ms)

- Cyclic Redundancy Checking (CRC)

- Packet Error Checking (PEC)

- Active-low open-drain NIRQ, NRST, and WDO outputs

### 2 Applications

- Advanced driver assistance system (ADAS)

- Sensor fusion

- Level 3 to Level 5 Autonomous Platforms

### 3 Description

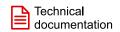

The TPS389C03-Q1 device integrated is an multichannel window monitor reset IC with three remote sense pins available in a 16-pin 3mm × 3mm QFN package.

This highly accurate multichannel voltage supervisor is designed for systems that operate on lowvoltage supply rails and have narrow margin supply tolerances. Internal glitch immunity and noise filters further eliminate false resets resulting from erroneous signals. This TPS389C03-Q1 device does not require any external resistors for setting overvoltage and undervoltage reset thresholds, which further optimizes overall accuracy, cost, solution size, and improves reliability for safety systems. I2C functionality gives flexibility in selecting thresholds, reset delays, glitch filters, and pin functionality. This device offers CRC error checking and a built-in ADC for voltage readouts to provide redundant error checking. The device has a built in Q&A watchdog and Error Signal monitor with independent watchdog enable and watchdog output.

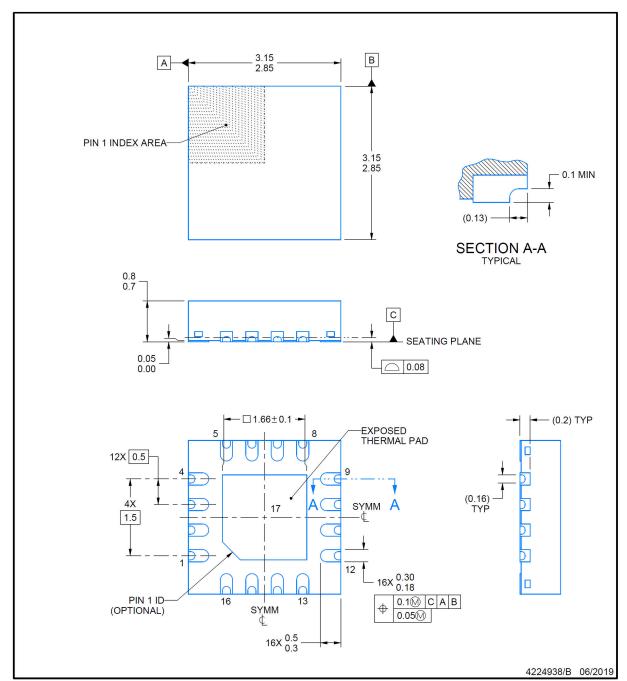

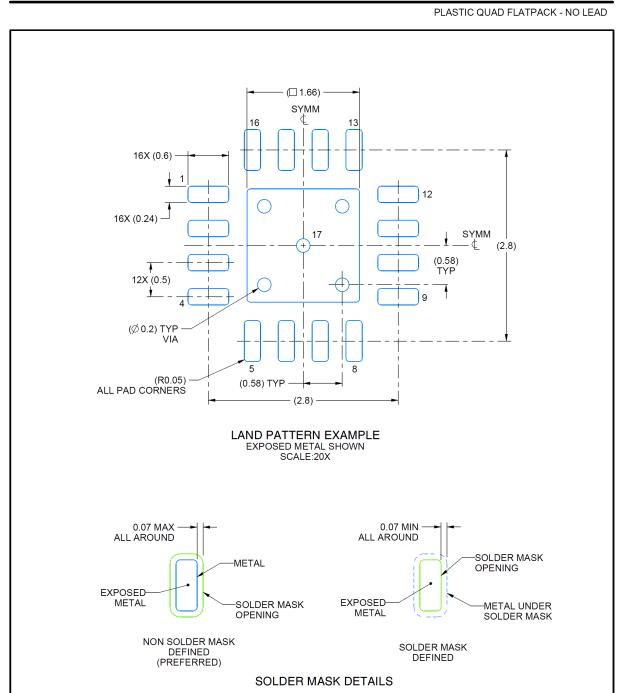

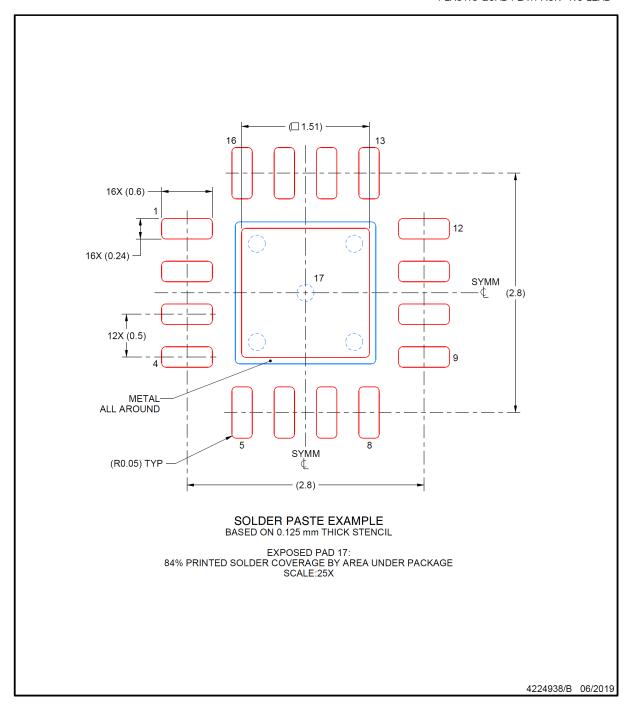

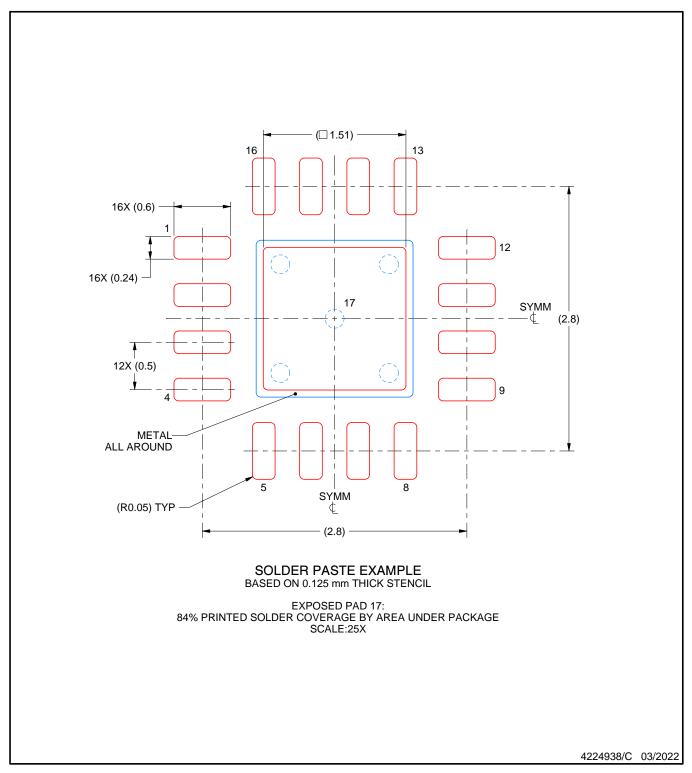

#### **Package Information**

| PART NUMBER  | PACKAGE (1)    | PACKAGE SIZE(2) |

|--------------|----------------|-----------------|

| TPS389C03-Q1 | RTE (WQFN, 16) | 3mm × 3mm       |

- For all available packages, see Section 12.

- The package size (length × width) is a nominal value and includes pins, where applicable.

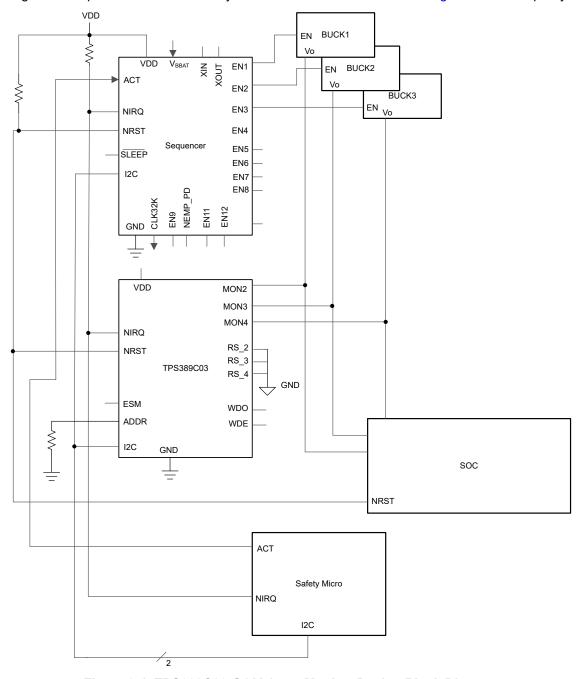

TPS389C03-Q1 Typical Circuit

## **Table of Contents**

| 1 Features1                           |   |

|---------------------------------------|---|

| 2 Applications                        | 9 |

| 3 Description1                        |   |

| 4 Device Comparison                   |   |

| 5 Pin Configuration and Functions5    |   |

| 6 Specifications6                     |   |

| 6.1 Absolute Maximum Ratings6         | 1 |

| 6.2 ESD Ratings6                      |   |

| 6.3 Recommended Operating Conditions6 |   |

| 6.4 Thermal Information7              |   |

| 6.5 Electrical Characteristics7       |   |

| 6.6 Timing Requirements9              |   |

| 7 Detailed Description12              |   |

| 7.1 Overview12                        |   |

| 7.2 Functional Block Diagram12        | • |

| 7.3 Feature Description13             | • |

| 7.4 Device Functional Modes43         |   |

| 8 Register Maps 45                    |   |

|    | 8.1 Registers Overview                               | 45 |

|----|------------------------------------------------------|----|

| 9  | Application and Implementation                       | 78 |

|    | 9.1 Application Information                          |    |

|    | 9.2 Typical Application                              | 79 |

|    | 9.3 Power Supply Recommendations                     | 91 |

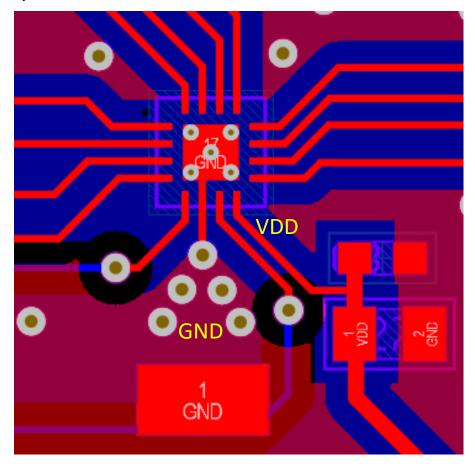

|    | 9.4 Layout                                           | 91 |

| 1  | 0 Device and Documentation Support                   | 93 |

|    | 10.1 Device Nomenclature                             | 93 |

|    | 10.2 Documentation Support                           | 95 |

|    | 10.3 Receiving Notification of Documentation Updates |    |

|    | 10.4 Support Resources                               | 95 |

|    | 10.5 Trademarks                                      |    |

|    | 10.6 Electrostatic Discharge Caution                 | 95 |

|    | 10.7 Glossary                                        | 95 |

| 1  | 1 Revision History                                   | 95 |

| 1: | 2 Mechanical, Packaging, and Orderable               |    |

|    | Information                                          | 96 |

|    |                                                      |    |

### **4 Device Comparison**

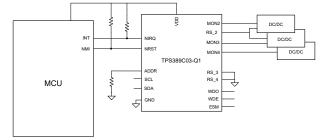

Figure 4-1 illustrates the device nomenclature. See Table 4-1 and Table 4-2 for more detailed information regarding the configuration of currently released variants. Table 10-1 provides a more in depth description of register configuration and data value stored.

Table 4-3 provides a summary of available device functions and corresponding part number. Contact TI sales representatives or go online to TI's E2E forum for details and availability of other options; minimum order quantities apply.

Figure 4-1. TPS389C03-Q1 Device Nomenclature

Table 4-1. TPS389C0x-Q1 Device Threshold Table

| Ordering Code      | Monitor Channel<br>Count | Thresholds  | VMON2 (V) | VMON3 (V) | VMON4 (V) |

|--------------------|--------------------------|-------------|-----------|-----------|-----------|

| TPS389C0300CRTERQ1 | 3                        | UV_HF/OV_HF | 4.56/5.44 | 3.02/3.6  | 0.2/1.475 |

|                    |                          | UV_LF/OV_LF | 4.56/5.44 | 3.02/3.6  | 0.2/1.475 |

Table 4-2. TPS389C0x-Q1 Device Configuration Table

| Ordering Code          | Functions        | Scaling | OV/UV<br>DEBOUNCE | LF<br>CUTOFF | BIST   | PEC      | WD Open<br>( ms ) | WD Close<br>( ms ) | Max WD violation count | I2c pull-<br>up<br>voltage<br>(v) |

|------------------------|------------------|---------|-------------------|--------------|--------|----------|-------------------|--------------------|------------------------|-----------------------------------|

| TPS389C0300CR<br>TERQ1 | Monitor<br>LF/HF | 4/4/1   | 102.4 us          | 1kHz         | At POR | Disabled | 30                | 30                 | 2                      | 3.3V                              |

**Table 4-3. Multichannel Supervisor Summary Table**

| Table 4-5: Mattichanner Supervisor Sammary Table |              |                  |                  |                  |              |                  |  |

|--------------------------------------------------|--------------|------------------|------------------|------------------|--------------|------------------|--|

| Specification                                    | TPS38900x-Q1 | TPS389R0x-Q1 (1) | TPS38800x-Q1 (1) | TPS388R0x-Q1 (1) | TPS389C0x-Q1 | TPS388C0x-Q1 (1) |  |

| Hardware ASIL<br>Rating                          | D            | D                | В                | В                | D            | В                |  |

| Monitoring<br>Channel Count                      | 4 to 8       | 4 to 7           | 4 to 8           | 4 to 7           | 3 to 6       | 3 to 6           |  |

| Monitoring Range                                 | 0.2 to 5.5V  | 0.2 to 5.5V      | 0.2 to 5.5V      | 0.2 to 5.5V      | 0.2 to 5.5V  | 0.2 to 5.5V      |  |

| Comparator<br>Monitoring (HF<br>Faults)          | ✓            | ✓                | ✓                | <b>√</b>         | ✓            | ✓                |  |

| ADC Monitoring (LF Faults)                       | ✓            | ✓                | х                | х                | ✓            | х                |  |

| Watchdog                                         | х            | х                | х                | х                | Q&A          | Window           |  |

| Voltage Telemetry                                | ✓            | ✓                | х                | х                | ✓            | х                |  |

| Monitor Glitch<br>Filtering                      | ✓            | ✓                | ✓                | ✓                | ✓            | ✓                |  |

| Sequence Logging                                 | ✓            | х                | ✓                | х                | ✓            | ✓                |  |

| NIRQ PIN                                         | ✓            | ✓                | ✓                | ✓                | ✓            | ✓                |  |

| NRST PIN                                         | х            | ✓                | х                | ✓                | ✓            | ✓                |  |

| SYNC PIN                                         | ✓            | х                | х                | х                | х            | х                |  |

| WDO PIN                                          | х            | х                | x                | х                | ✓            | ✓                |  |

### **Table 4-3. Multichannel Supervisor Summary Table (continued)**

|               |              |                  |                  | <u> </u>         |              |                  |

|---------------|--------------|------------------|------------------|------------------|--------------|------------------|

| Specification | TPS38900x-Q1 | TPS389R0x-Q1 (1) | TPS38800x-Q1 (1) | TPS388R0x-Q1 (1) | TPS389C0x-Q1 | TPS388C0x-Q1 (1) |

| WDI PIN       | x            | x                | x                | x                | X            | ✓                |

| ESM PIN       | x            | x                | х                | x                | ✓            | x                |

(1) Preview, contact TI sales representatives or on TI's E2E forum for details and availability of other options

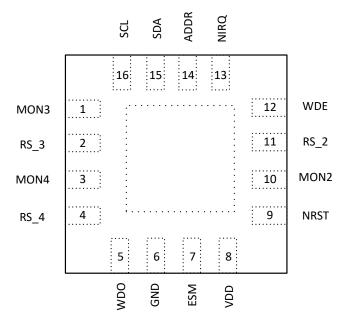

# **5 Pin Configuration and Functions**

Figure 5-1. RTE Package 16-Pin WQFN TPS389C03-Q1 Top View

**Table 5-1. Pin Functions**

| PIN |              |     |                                        |

|-----|--------------|-----|----------------------------------------|

| NO. | TPS389C03-Q1 | I/O | DESCRIPTION                            |

| NO. | NAME         |     |                                        |

| 1   | MON3         | I   | Voltage monitor channel 3              |

| 2   | RS_3         | I   | Remote sense for channel 3             |

| 3   | MON4         | I   | Voltage monitor channel 4              |

| 4   | RS_4         | ı   | Remote sense for channel 4             |

| 5   | WDO          | 0   | Open drain pin for Watch Dog errors    |

| 6   | GND          | -   | Power ground                           |

| 7   | ESM          | ı   | Error signal monitor                   |

| 8   | VDD          | -   | Power supply rail                      |

| 9   | NRST         | 0   | Open drain Reset pin                   |

| 10  | MON2         | ı   | Voltage monitor channel 2              |

| 11  | RS_2         | ı   | Remote sense for channel 2             |

| 12  | WDE          | ı   | Watch dog enable                       |

| 13  | NIRQ         | 0   | Active-low open-drain interrupt output |

| 14  | ADDR         | ı   | I <sup>2</sup> C address select pin    |

| 15  | SDA          | I/O | I <sup>2</sup> C data pin              |

| 16  | SCL          | I   | I <sup>2</sup> C clock pin             |

| 17  | GND          | -   | Exposed power ground pad               |

### **6 Specifications**

### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                 |                                                | MIN                         | MAX     | UNIT |

|-----------------|------------------------------------------------|-----------------------------|---------|------|

| Voltage         | VDD                                            | -0.3                        | 6       | V    |

| Voltage         | NIRQ,NRST,WDO,ESM,WDE                          | -0.3                        | 6       | V    |

| Voltage         | SCL,SDA                                        | -0.3                        | VDD+0.3 | V    |

| Voltage         | ADDR                                           | -0.3                        | 2       | V    |

| Voltage         | MONx                                           | -0.3                        | 6       | V    |

| Current         | NIRQ,NRST,WDO                                  |                             | ±10     | mA   |

|                 | Continuous total power dissipation             | See the Thermal Information |         |      |

| Temperature (2) | Operating junction temperature, T <sub>J</sub> | -40                         | 150     | °C   |

| remperature (=) | Operating free-air temperature, T <sub>A</sub> | -40                         | 125     | °C   |

|                 | Storage temperature, T <sub>stg</sub>          | -65                         | 150     | °C   |

<sup>(1)</sup> Stresses beyond values listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 6.2 ESD Ratings

|          |                         |                                            |                         | VALUE | UNIT |

|----------|-------------------------|--------------------------------------------|-------------------------|-------|------|

|          |                         | Human-body model (HBM), per ANSI/ESDA/JEDE | C JS-001 <sup>(1)</sup> | ±2000 |      |

| V/ECD)   | Electrostatic discharge | Charged-device model (CDM), per AEC        | All pins                | ±500  | V    |

| discriai | g                       | Q100-011                                   | Corner pins             | ±750  |      |

<sup>(1)</sup> AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification

### **6.3 Recommended Operating Conditions**

|                            |                                             | MIN | NOM MAX | UNIT |

|----------------------------|---------------------------------------------|-----|---------|------|

| VDD                        | Supply pin voltage                          | 2.6 | 5.5     | V    |

| NIRQ,NRST,W<br>DO,ESM,WDE  | Pin voltage                                 | 0   | 5.5     | V    |

| I <sub>NIRQ,NRST,WDO</sub> | Pin Currents                                | 0   | ±5      | mA   |

| ADDR                       | Address pin voltage                         | 0   | 1.8     | V    |

| MONx                       | Monitor Pins                                | 0   | 5.5     | V    |

| SCL,SDA                    | Pin Voltage                                 | 0   | VDD     | V    |

| R <sub>UP</sub> (1)        | Pull-up resistor (Open Drain config)        | 1   | 100     | kΩ   |

| T <sub>J</sub>             | Junction temperature (free-air temperature) | -40 | 125     | °C   |

<sup>(2)</sup> As a result of the low dissipated power in this device, it is assumed that  $T_J = T_A$ .

### **6.4 Thermal Information**

|                       |                                              | TPS389C03-Q1 |      |

|-----------------------|----------------------------------------------|--------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | RTE (WQFN)   | UNIT |

|                       |                                              | PINS         |      |

| R <sub>θJA</sub>      | Junction-to-ambient thermal resistance       | 53.4         | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 51.4         | °C/W |

| R <sub>0JB</sub>      | Junction-to-board thermal resistance         | 17.2         | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 0.3          | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 20.7         | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 3.9          | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

### 6.5 Electrical Characteristics

At  $2.6V \le VDD \le 5.5V$ , NIRQ Voltage =  $10k\Omega$  to  $V_{DD}$ , NIRQ load = 10pF, and over the operating free-air temperature range of  $-40^{\circ}C$  to  $125^{\circ}C$ , unless otherwise noted. Typical values are at  $T_{J} = 25^{\circ}C$ , typical conditions at VDD= 3.3V.

|                                 | PARAMETER                                | TEST CONDITIONS                            | MIN  | TYP  | MAX   | UNIT |

|---------------------------------|------------------------------------------|--------------------------------------------|------|------|-------|------|

| COMMON PA                       | RAMETERS                                 |                                            |      |      |       |      |

| VDD                             | Input supply voltage                     |                                            | 2.6  |      | 5.5   | V    |

| VDD                             | Rising Threshold                         |                                            | 2.67 |      | 2.81  | V    |

| VDD <sub>UVLO</sub>             | Falling Threshold                        |                                            | 2.48 |      | 2.6   | V    |

| V <sub>POR</sub>                | Power on Reset Voltage (2)               |                                            |      |      | 1.65  | V    |

| I <sub>DD_Active</sub>          | Supply current into VDD pin              | VDD≤5.5V                                   |      | 1550 | 2000  | μΑ   |

| V <sub>MONX</sub>               | MON voltage range                        |                                            | 0.2  |      | 5.5   | V    |

| I <sub>MONX</sub>               | Input current MONx pins                  | V <sub>MON</sub> =5V                       |      |      | 20    | μA   |

| VMONLLE                         | 1x mode (No scaling)                     |                                            | 0.2  |      | 1.475 | V    |

| VMON_LF                         | 4x mode                                  |                                            | 0.8  |      | 5.5   | V    |

| VMON UE                         | 1x mode (No scaling)                     |                                            | 0.2  |      | 1.475 | V    |

| VMON_HF                         | 4x mode                                  |                                            | 0.8  |      | 5.5   | V    |

| Threshold                       | 1x mode (No scaling)                     |                                            |      | 5    |       | mV   |

| Granularity_L<br>F              | 4x mode                                  |                                            |      | 20   |       | mV   |

| Threshold<br>Granularity_<br>HF | 1x mode (No scaling)                     |                                            |      | 5    |       | mV   |

| Threshold<br>Granularity_<br>HF | 4x mode                                  |                                            |      | 20   |       | mV   |

|                                 |                                          | 0.2V≤V <sub>MONX</sub> ≤1.0V               | -6   |      | 6     | mV   |

| Accuracy HF                     | VMON                                     | 1.0V <v<sub>MONX≤1.475V</v<sub>            | -7.5 |      | 7.5   | mV   |

| Accuracy_FF                     | VIVIOIN                                  | 1.475V <v<sub>MONX≤2.95V</v<sub>           | -0.6 |      | 0.6   | %    |

|                                 |                                          | V <sub>MONX</sub> >2.95V                   | -0.7 |      | 0.7   | %    |

|                                 | Hysteresis on UV,OV pin(Hysteresis is    | 0.2V≤V <sub>MONX</sub> ≤1.475V             |      | 5    | 11    | mV   |

| V <sub>HYS_HF</sub>             | with respect of the tripoint ((UV),(OV)) | 1.475V <v<sub>MONX≤2.95V</v<sub>           |      | 9    | 16    | 111V |

|                                 | (1)                                      | VMONX>2.95V                                |      | 17   | 28    | mV   |

| MON_OFF                         | OFF Voltage threshold                    | Monitored falling edge of V <sub>MON</sub> | 140  |      | 215   | mV   |

| NIRQ                            | On resistance- when asserted Low         | Open Drain                                 |      | 12   | 17    | Ω    |

| V <sub>OL</sub>                 | Low level output voltage-NIRQ            | NIRQ, 5.5V/5mA                             |      |      | 100   | mV   |

### 6.5 Electrical Characteristics (continued)

At  $2.6V \le VDD \le 5.5V$ , NIRQ Voltage =  $10k\Omega$  to  $V_{DD}$ , NIRQ load = 10pF, and over the operating free-air temperature range of  $-40^{\circ}C$  to  $125^{\circ}C$ , unless otherwise noted. Typical values are at  $T_{J} = 25^{\circ}C$ , typical conditions at VDD= 3.3V.

|                      | PARAMETER                                  | TEST CONDITIONS                                     | MIN           | TYP  | MAX           | UNIT |

|----------------------|--------------------------------------------|-----------------------------------------------------|---------------|------|---------------|------|

| I <sub>lkg(OD)</sub> | Open-Drain output leakage current-<br>NIRQ | NIRQ pin in High Impedance,VNIRQ= 5.5, Not asserted |               |      | 90            | nA   |

| NRST                 | On resistance- when asserted Low           | Open Drain                                          |               | 10   | 15            | Ω    |

| V <sub>OL</sub>      | Low level output voltage-NRST              | NRST , 5.5V/5mA                                     |               |      | 100           | mV   |

| I <sub>lkg(OD)</sub> | Open-Drain output leakage current-NRST     | NRST pin in High Impedance,VNRST= 5.5, Not asserted |               |      | 600           | nA   |

| WDO                  | On resistance- when asserted Low           | Open Drain                                          |               | 12   | 17            | Ω    |

| V <sub>OL</sub>      | Low level output voltage-WDO               | WDO , 5.5V/5mA                                      |               |      | 100           | mV   |

| I <sub>lkg(OD)</sub> | Open-Drain output leakage current-<br>WDO  | WDO pin in High Impedance,VNRST= 5.5, Not asserted  |               |      | 500           | nA   |

| ESM_L                | Logic Low Input                            |                                                     |               |      | 0.24 x<br>VDD | V    |

| ECM LI               | Logic High Input                           | VDD>4.5                                             | 0.55 x<br>VDD |      |               | V    |

| ESM_H                | Logic right input                          | VDD<4.5                                             | 0.6 x<br>VDD  |      |               | V    |

| Ilkg(ESM)            | Leakage current                            | ESM=5.5V                                            |               |      | 75            | μΑ   |

| WDE_L                | Logic Low Input                            |                                                     |               |      | 0.36          | V    |

| WDE_H                | Logic High Input                           |                                                     | 1.26          |      |               | V    |

| Ilkg(WDE)            | Leakage current                            | WDE=5.5V                                            |               |      | 5             | μA   |

| I <sub>ADDR</sub>    | ADDR pin current                           |                                                     |               | 20   |               | μA   |

|                      |                                            | R=5.36k                                             |               | 0x30 |               |      |

|                      |                                            | R=16.2k                                             |               | 0x31 |               |      |

|                      |                                            | R=26.7k                                             |               | 0x32 |               |      |

| 100 4000             |                                            | R=37.4k                                             |               | 0x33 |               |      |

| I2C ADDR             | (Hex format)                               | R=47.5k                                             |               | 0x34 |               |      |

|                      |                                            | R=59.0k                                             |               | 0x35 |               |      |

|                      |                                            | R=69.8k                                             |               | 0x36 |               |      |

|                      |                                            | R=80.6k                                             |               | 0x37 |               |      |

| TSD                  | Thermal Shutdown                           |                                                     |               | 155  |               | °C   |

| TSD Hys              | Thernal Shutdown Hysterisis                |                                                     |               | 25   |               | °C   |

| RS                   | Remote sense range                         |                                                     | -100          |      | 100           | mV   |

| ADC SPECIF           | CATION                                     |                                                     |               |      |               |      |

| Vin                  | Input Range                                |                                                     | 0.2           |      | 5.5           | V    |

|                      | 1x mode                                    | 0.2V≤VMON≤1.475V                                    |               | 5    |               | mV   |

| Resolution           | 4x mode                                    | VMON>1.475V                                         | ,             | 20   |               | mV   |

| f <sub>S</sub>       | Sample Rate                                |                                                     |               | 125  |               | ksps |

|                      | VMON,1x mode                               | 0.2V≤VMON≤1.475V                                    | -12           |      | +12           | mV   |

| Accuracy_LF          | VMON, 4x mode                              | VMON>1.475V                                         | -40           |      | +40           | mV   |

| I2C ELECTRI          | CAL SPECIFICATIONS                         |                                                     |               |      | -             |      |

|                      | Hysteresis LF Faults, 1x mode              | 0.2V≤VMON≤1.475V                                    |               | 10   | 15            | mV   |

| $V_{HYS\_LF}$        | Hysteresis LF Faults, 4x mode              | VMON>1.475V                                         |               | 40   | 55            | mV   |

| C <sub>B</sub>       | Capacitive load for SDA and SCL            | 211 111 21                                          |               |      | 400           | pF   |

| SDA,SCL              | Low Threshold                              | DEV_CONFIG.SOC_IF=0                                 |               |      | 0.84          | V    |

| 33/ 1,33L            | Lott Hillouriold                           | 5-1_00141 10.000_II =0                              |               |      | 0.04          | v    |

### 6.5 Electrical Characteristics (continued)

At  $2.6V \le VDD \le 5.5V$ , NIRQ Voltage =  $10k\Omega$  to  $V_{DD}$ , NIRQ load = 10pF, and over the operating free-air temperature range of  $-40^{\circ}C$  to  $125^{\circ}C$ , unless otherwise noted. Typical values are at  $T_{J} = 25^{\circ}C$ , typical conditions at VDD= 3.3V.

| PARAMETER |                | TEST CONDITIONS     | MIN  | TYP | MAX | UNIT |

|-----------|----------------|---------------------|------|-----|-----|------|

| SDA,SCL   | High Threshold | DEV_CONFIG.SOC_IF=0 | 2.31 |     |     | V    |

### 6.6 Timing Requirements

At 2.6V ≤ VDD ≤ 5.5V, NIRQ Voltage = 10kΩ to VDD, NIRQ load = 10pF, and over the operating free-air temperature range of  $-40^{\circ}$ C to 125°C, unless otherwise noted. Typical values are at T<sub>1</sub> = 25°C, typical conditions at VDD = 3.3V.

|                         |                                                                                     |                              | MIN | NOM | MAX | UNIT |

|-------------------------|-------------------------------------------------------------------------------------|------------------------------|-----|-----|-----|------|

| COMMON F                | PARAMETERS                                                                          |                              |     |     | ·   |      |

| t <sub>BIST</sub>       | POR to ready with BIST, TEST_CFG.AT_POR=1                                           | includes OTP load            |     |     | 12  | ms   |

| tNBIST                  | POR to ready without BIST, TEST_CFG.AT_POR=0                                        | includes OTP load            |     |     | 2   | ms   |

| BIST                    | BIST time,TEST_CFG.AT_POR=1 or<br>TEST_CFG.AT_SHDN=1                                |                              |     |     | 10  | ms   |

| t <sub>I2C_ACT</sub>    | I2C active from BIST complete                                                       |                              |     |     | 0   | μs   |

| t <sub>NRST</sub>       | Fault detection to NRST assertion latency                                           |                              |     |     | 25  | μs   |

| t <sub>WDO</sub>        | Fault detection to WDO assertion latency                                            |                              |     |     | 25  | μs   |

| t <sub>NIRQ</sub>       | Fault detection to NIRQ assertion latency (except OV/UV faults)                     |                              |     |     | 25  | μs   |

| t <sub>PD_NIRQ_1X</sub> | HF fault Propagation detect delay (default deglitch filter) includes digitial delay | VIT_OV/UV +/-<br>100mV       |     |     | 650 | ns   |

| t <sub>PD_NIRQ_4X</sub> | HF fault Propagation detect delay (default deglitch filter) includes digitial delay | VIT_OV/UV +/-<br>400mV       |     |     | 750 | ns   |

|                         |                                                                                     | I2C Register time delay =000 |     | 200 |     | μs   |

|                         |                                                                                     | I2C Register time delay =001 |     | 1   |     | ms   |

|                         |                                                                                     | I2C Register time delay =010 |     | 10  |     | ms   |

|                         | DECET the delay                                                                     | I2C Register time delay =011 |     | 16  |     | ms   |

| t <sub>D</sub>          | RESET time delay                                                                    | I2C Register time delay =100 |     | 20  |     | ms   |

|                         |                                                                                     | I2C Register time delay =101 |     | 70  |     | ms   |

|                         |                                                                                     | I2C Register time delay =110 |     | 100 |     | ms   |

|                         |                                                                                     | I2C Register time delay =111 |     | 200 |     | ms   |

Copyright © 2024 Texas Instruments Incorporated

Submit Document Feedback

Hysteresis is with respect of the tripoint  $(V_{\text{IT-(UV)}}, V_{\text{IT+(OV)}})$ .  $V_{\text{POR}}$  is the minimum  $V_{\text{DDX}}$  voltage level for a controlled output state.

### 6.6 Timing Requirements (continued)

At  $2.6\text{V} \le \text{VDD} \le 5.5\text{V}$ , NIRQ Voltage =  $10\text{k}\Omega$  to VDD, NIRQ load = 10pF, and over the operating free-air temperature range of  $-40^{\circ}\text{C}$  to  $125^{\circ}\text{C}$ , unless otherwise noted. Typical values are at  $T_J = 25^{\circ}\text{C}$ , typical conditions at VDD = 3.3V.

|                                |                                | 20 G, typical col            | MIN | NOM | MAX   | UNIT |

|--------------------------------|--------------------------------|------------------------------|-----|-----|-------|------|

|                                |                                | I2C Register time delay =000 |     | 200 |       | μs   |

|                                |                                | I2C Register time delay =001 |     | 1   |       | ms   |

|                                |                                | I2C Register time delay =010 |     | 10  |       | ms   |

| <b>+</b>                       | WDO delay                      | I2C Register time delay =011 |     | 16  |       | ms   |

| t <sub>D_WD</sub>              |                                | I2C Register time delay =100 |     | 20  |       | ms   |

|                                |                                | I2C Register time delay =101 |     | 70  |       | ms   |

|                                |                                | I2C Register time delay =110 |     | 100 |       | ms   |

|                                |                                | I2C Register time delay =111 |     | 200 |       | ms   |

|                                | Debounce time                  | I2C Register time delay =00  |     | 10  |       |      |

| t <sub>debounce_</sub> ES<br>M |                                | I2C Register time delay =01  |     | 25  |       |      |

|                                |                                | I2C Register time delay =10  |     | 50  |       | μs   |

|                                |                                | I2C Register time delay =11  |     | 100 |       |      |

| t <sub>GI_R</sub>              | UV & OV debounce range via I2C | FLT_HF(N)                    | 0.1 |     | 102.4 | μs   |

Copyright © 2024 Texas Instruments Incorporated Product Folder Links: *TPS389C03-Q1*

### 6.6 Timing Requirements (continued)

At  $2.6V \le VDD \le 5.5V$ , NIRQ Voltage =  $10k\Omega$  to VDD, NIRQ load = 10pF, and over the operating free-air temperature range of  $-40^{\circ}C$  to  $125^{\circ}C$ , unless otherwise noted. Typical values are at  $T_1 = 25^{\circ}C$ , typical conditions at VDD = 3.3V.

|                  | · ·                                                   |                                                | MIN  | NOM | MAX  | UNIT |

|------------------|-------------------------------------------------------|------------------------------------------------|------|-----|------|------|

| I2C TIMIN        | NG CHARACTERISTICS                                    |                                                |      |     |      |      |

| f <sub>SCL</sub> | Serial clock frequency                                | Standard mode                                  |      |     | 100  | kHz  |

| f <sub>SCL</sub> | Serial clock frequency                                | Fast mode                                      |      |     | 400  | kHz  |

| f <sub>SCL</sub> | Serial clock frequency                                | Fast mode +                                    |      |     | 1    | MHz  |

| t <sub>LOW</sub> | SCL low time                                          | Standard mode                                  | 4.7  |     |      | μs   |

| t <sub>LOW</sub> | SCL low time                                          | Fast mode                                      | 1.3  |     |      | μs   |

| t <sub>LOW</sub> | SCL low time                                          | Fast mode +                                    | 0.5  | ,   |      | μs   |

| HIGH             | SCL high time                                         | Standard mode                                  | 4    |     |      | μs   |

| HIGH             | SCL high time                                         | Fast mode +                                    | 0.26 |     |      | μs   |

| SU;DAT           | Data setup time                                       | Standard mode                                  | 250  |     |      | ns   |

| SU;DAT           | Data setup time                                       | Fast mode                                      | 100  |     |      | ns   |

| SU;DAT           | Data setup time                                       | Fast mode +                                    | 50   | ,   |      | ns   |

| HD;DAT           | Data hold time                                        | Standard mode                                  | 10   | ,   | 3450 | ns   |

| HD;DAT           | Data hold time                                        | Fast mode                                      | 10   |     | 900  | ns   |

| HD;DAT           | Data hold time                                        | Fast mode +                                    | 10   |     |      | ns   |

| SU;STA           | Setup time for a Start or Repeated Start condition    | Standard mode                                  | 4.7  |     |      | μs   |

| SU;STA           | Setup time for a Start or Repeated Start condition    | Fast mode                                      | 0.6  |     |      | μs   |

| SU;STA           | Setup time for a Start or Repeated Start condition    | Fast mode +                                    | 0.26 |     |      | μs   |

| HD:STA           | Hold time for a Start or Repeated Start condition     | Standard mode                                  | 4    |     |      | μs   |

| HD:STA           | Hold time for a Start or Repeated Start condition     | Fast mode                                      | 0.6  |     |      | μs   |

| HD:STA           | Hold time for a Start or Repeated Start condition     | Fast mode +                                    | 0.26 |     |      | μs   |

| BUF              | Bus free time between a STOP and START condition      | Standard mode                                  | 4.7  |     |      | μs   |

| BUF              | Bus free time between a STOP and START condition      | Fast mode                                      | 1.3  |     |      | μs   |

| BUF              | Bus free time between a STOP and START condition      | Fast mode +                                    | 0.5  |     |      | μs   |

| SU;STO           | Setup time for a Stop condition                       | Standard mode                                  | 4    |     |      | μs   |

| SU;STO           | Setup time for a Stop condition                       | Fast mode                                      | 0.6  |     |      | μs   |

| SU;STO           | Setup time for a Stop condition                       | Fast mode +                                    | 0.26 |     |      | μs   |

| rDA              | Rise time of SDA signal                               | Standard mode                                  |      |     | 1000 |      |

| rDA              | Rise time of SDA signal                               | Fast mode                                      | 20   |     | 300  | ns   |

| rDA              | Rise time of SDA signal                               | Fast mode +                                    |      |     | 120  | ns   |

| fDA              | Fall time of SDA signal                               | Standard mode                                  |      |     | 300  | ns   |

| fDA              | Fall time of SDA signal                               | Fast mode                                      | 1.4  |     | 300  | ns   |

| fDA              | Fall time of SDA signal                               | Fast mode +                                    | 6.5  |     | 120  | ns   |

| rCL              | Rise time of SCL signal                               | Standard mode                                  |      |     | 1000 | ns   |

| rCL              | Rise time of SCL signal                               | Fast mode                                      | 20   |     | 300  | ns   |

| rCL              | Rise time of SCL signal                               | Fast mode +                                    |      |     | 120  | ns   |

| fCL              | Fall time of SCL signal                               | Standard mode                                  |      |     | 300  | ns   |

| fCL              | Fall time of SCL signal                               | Fast mode                                      | 6.5  |     | 300  | ns   |

| fCL              | Fall time of SCL signal                               | Fast mode +                                    | 6.5  |     | 120  | ns   |

| tSP              | Pulse width of SCL and SDA spikes that are suppressed | Standard mode,<br>Fast mode and Fast<br>mode + |      |     | 50   | ns   |

### 7 Detailed Description

### 7.1 Overview

The TPS389C03-Q1 family of devices has three channels that can be configured for over voltage, under voltage or both in a window configuration. The TPS389C03-Q1 features a highly accurate window threshold voltages (up to ±5mV) and a variety voltage thresholds which can be factory configured or set on boot up by I2C commands.

The TPS389C03-Q1 includes the resistors used to set the overvoltage and undervoltage thresholds internal to the device. These internal resistors allow for lower component counts and greatly simplifies the design because no additional margins are needed to account for the accuracy of external resistors.

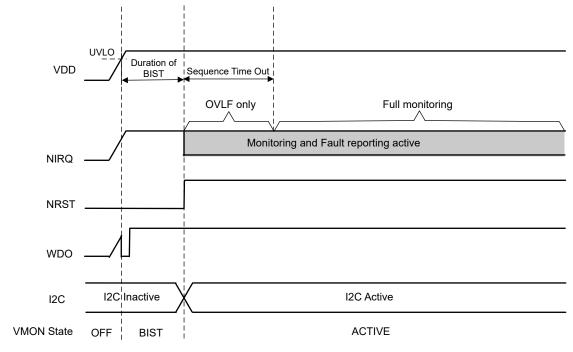

The TPS389C03-Q1 is designed to assert active low output signals (NIRQ and/or NRST) when the monitored voltage is outside the safe window. The default configuration has the interrupts enabled for over voltage and under voltage faults, sequence timeout set for 1ms, BIST enabled at POR, and over voltage and under voltage debounce set for 102.4µs.

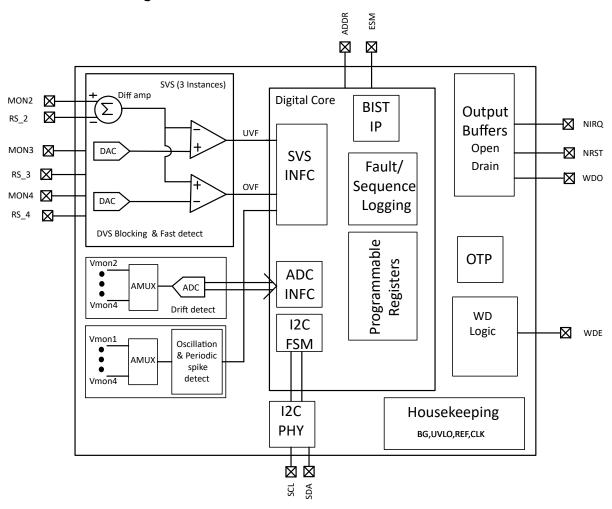

### 7.2 Functional Block Diagram

Figure 7-1. TPS389C03-Q1 Block Diagram

### 7.3 Feature Description

### 7.3.1 I<sup>2</sup>C

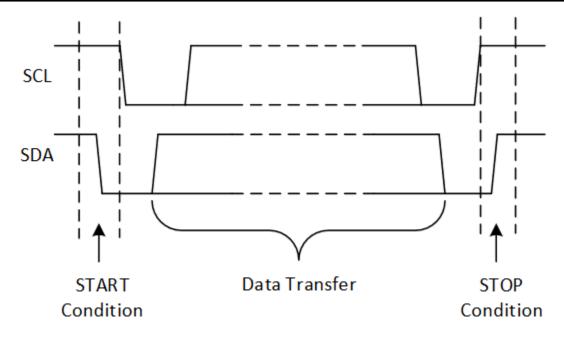

The TPS389C03-Q1 device follows the  $I^2C$  protocol (up to 1MHz) to manage communication with host devices such as an MCU or System on Chip (SoC).  $I^2C$  is a two wire communication protocol implemented using two signals, clock (SCL) and data (SDA). The host device is primary controller of communication. TPS389C03-Q1 device responds over the data line during read or write operation as defined by  $I^2C$  protocol. Both SCL and SDA signals are open drain topology and can be used in a wired-OR configuration with other devices to share the communication bus. Both SCL and SDA pins need an external pull up resistance to supply voltage ( $10k\Omega$  recommended).

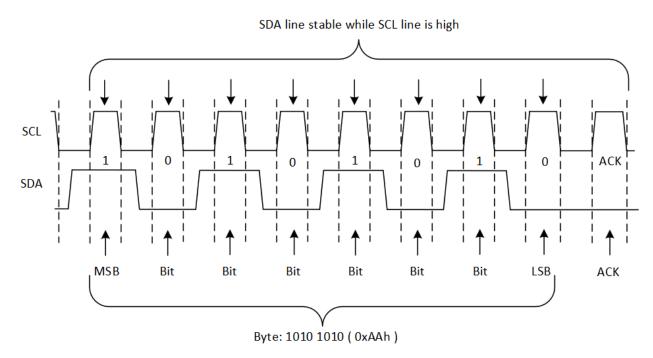

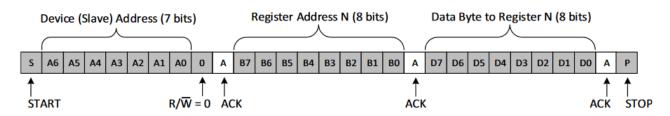

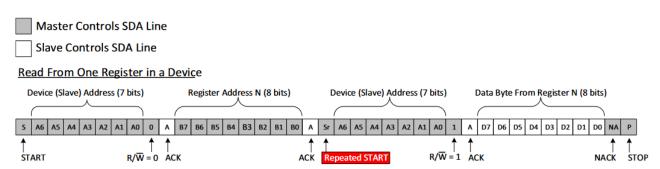

Figure 7-2 shows the timing relationship between SCL and SDA lines to transfer 1 byte of data. SCL line is always controlled by host. To transfer 1 byte data, host needs to send 9 clocks on SCL. 8 clocks for data and 1 clock for ACK or NACK. SDA line will be controlled by either host or TPS389C03-Q1 device based on the read or write operation. Figure 7-3 and Figure 7-4 highlight the communication protocol flow and which device controls SDA line at various instances during active communication.

Figure 7-2. SCL to SDA timing for 1 byte data transfer

Master Controls SDA Line

Slave Controls SDA Line

### Write to One Register in a Device

Figure 7-3. I<sup>2</sup>C write protocol

Figure 7-4. I<sup>2</sup>C read protocol

Before initiating communication over  $I^2C$  protocol, host needs to confirm the  $I^2C$  bus is available for communication. Monitor the SCL and SDA lines, if any line is pulled low, the  $I^2C$  bus is occupied. Host needs to wait until the bus is available for communication. Once the bus is available for communication, the host can initiate read or write operation by issuing a START condition. Once the  $I^2C$  communication is complete, release the bus by issuing STOP command. Figure 7-5 shows how to implement START and STOP condition.

Figure 7-5. I<sup>2</sup>C START and STOP condition

The SDA line may get stuck in logic low level if required number of clocks are not provided by the host. In this scenario, host should provide multiple clocks on SCL line until the SDA line goes high. After this event, host should issue I<sup>2</sup>C stop command. This will release the I<sup>2</sup>C bus and other devices can use the I<sup>2</sup>C bus.

Table 7-1 shows the different functionality available when programming with I<sup>2</sup>C.

Table 7-1. User Programmable I<sup>2</sup>C Functions

| FUNCTIONS                                  | DESCRIPTION                                                                  |

|--------------------------------------------|------------------------------------------------------------------------------|

| Thresholds for OV/UV- HF                   | Adjustable in 5mV steps from 0.2V to 1.475V and 20mV steps from 0.8V to 5.5V |

| Thresholds for OV/UV - LF                  | Adjustable in 5mV steps from 0.2V to 1.475V and 20mV steps from 0.8V to 5.5V |

| Voltage Monitoring scaling                 | 1 or 4                                                                       |

| Glitch immunity for OV/UV- HF              | 0.1 us to 102.4 us                                                           |

| Low Frequency Cutoff filter                | 250Hz to 4kHz                                                                |

| Enable sequence timeout                    | 1ms to 4s                                                                    |

| Packet error checking for I <sup>2</sup> C | Enabling or Disabling                                                        |

| Force NIRQ/NRST/WDO assertion              | Controlled by I <sup>2</sup> C register                                      |

| Individual channel MON                     | Enable or Disable                                                            |

| Interrupt disable functions                | BIST, PEC, TSD, CRC                                                          |

| ESM Threshold                              | 1ms to 864ms                                                                 |

| ESM Debounce                               | 10us to 100us                                                                |

| Reset Delay                                | 200us to 200ms                                                               |

| MAX Violation Count                        | 0 to 7                                                                       |

| Watchdog Startup Delay Multiplier          | 0 to 7                                                                       |

| Watchdog Open and Close Window Times       | 1ms to 864ms                                                                 |

| Watchdog Output Delay                      | 200us to 200ms (only applicable for non-latched WDO)                         |

| OV/UV/ESM/WDT                              | Mappable individually to NIRQ, NRST, and WDO                                 |

#### 7.3.2 Maskable Interrupt (AMSK)

In the case of power up, AMSK\_ON register applies. AMSK\_ON masks interrupts until the MON voltage crosses the UVLF threshold or sequence timeout expires whichever is sooner. In the case of power down AMSK\_OFF register applies. AMSK\_ON masks interrupts until the MON voltage is below the OFF threshold and then the OVLF interrupts are active.

Table 7-2 summarizes the auto-mask operation for power up and power down.

Table 7-2. Auto-Mask Operation for the Power Up and Power Down

| TRANSITION | AUTO-MASK APPLIED | AUTO-MASK APPLIES<br>TO | AUTO-MASK INACTIVE                                    | INTERRUPTS ACTIVE<br>FOR MON CHANNELS<br>NOT IN AUTO-MASK |

|------------|-------------------|-------------------------|-------------------------------------------------------|-----------------------------------------------------------|

| Power Up   | AMSK_ON           | IEN UVLF, IEN UVHF,     | SEQ_TOUT expires or rail crosses UVLF                 | At Power Up                                               |

| Power Down | AMSK_OFF          | IEN OVHE                | Auto-mask active in transition until SEQ_TOUT expires | Until SEQ_TOUT expires                                    |

#### 7.3.3 VDD

The TPS389C03-Q1 is designed to operate from an input voltage supply range between 2.6V to 5.5V. An input supply capacitor is not required for this device; however, if the input supply is noisy good analog practice is to place a  $1\mu$ F capacitor between the VDD pin and the GND pin.

$V_{DD}$  needs to be at or above  $V_{DD(MIN)}$  for at least the start-up delay  $(t_{SD} + t_D)$  for the device to be fully functional.

#### 7.3.4 MON

The TPS389C03-Q1 combines two comparators with a precision reference voltage and a trimmed resistor divider per monitor (MON) channel. This configuration optimizes device accuracy because all resistor tolerances are accounted for in the accuracy and performance specifications. Both comparators also include built-in hysteresis that provides noise immunity and provides stable operation.

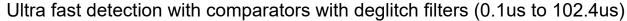

Each MON channel can be configured for Low Frequency (LF) and High Frequency (HF) fault detection. HF fault detection uses a comparator for UV and OV measurements referenced to the threshold voltage. A debounce filter for glitch immunity can be configured for HF faults using the FLT\_HF registers in BANK1 associated with each MON channel.

LF fault detection measures the voltage through an ADC that can be used to monitor voltage drift. The LF detection thresholds can be configured for various purposes. For example, the OVLF threshold can be set lower than the OVHF threshold for drift monitoring. Alternatively, the OVLF threshold can be set to overlap with the OVHF threshold for redundancy. LF and HF faults are configured using the UV\_HF, OV\_HF, UV\_LF, and OV\_LF registers in BANK1. Each MON channel has unique UV\_HF, OV\_HF, UV\_LF, and OV\_LF registers. The diagram shown in Figure 7-6 illustrates an example of how the LF and HF faults can be configured.

Figure 7-6. MON Channel State Diagram

Although not required in most cases, for noisy applications good analog design practice is to place a 1nF to 10nF bypass capacitor at the MON input to reduce sensitivity to transient voltages on the monitored signal. Specific debounce times or deglitch times can also be set independently for each MON via I<sup>2</sup>C registers

When monitoring VDD supply voltage, the MON pin can be connected directly to VDD. The outputs NIRQ and NRST are high impedance when voltage at the MON pin is between upper and lower boundary of threshold.

The MON channel settings can be adjusted by using the associated registers listed in the register maps found in Section 8. Using the register maps, the code example in Figure 7-7 demonstrates how MON2 can be reconfigured.

```

ADDR 30

11

Go to Bank 1

WR F0 01

11

Check UVHF, OVHF thresholds for MON2 and MON3

RD 30 //MON2 UVHF

RD 31 //MON2 OVHF

RD 40 //MON3 UVHF

RD 41 //MON3 OVHF

Check UVLF, OVLF thresholds for MON2 and MON3

RD 32 //MON2 UVHF

RD 33 //MON2 OVHF

RD 42 //MON3 UVHF

RD 43 //MON3 OVHF

Example change OVHF threshold MON2 to 5.5V

11

WR 31 EB

11

Example change OVHF threshold MON2 to 5.48V

WR 31 EA

11

Example change OVHF threshold MON2 to 5.44V

WR 31 E8

11

Telemetry read the voltages being monitored

11

Go to Bank 0

WR F0 00

RD 41 // MON2 Voltage

RD 42 // MON3 Voltage

11

Simulate an OV fault on MON2

11

Go to Bank 1

WR F0 01

WR 31 C8 // Change OVHF threshold to 4.8V

NIRQ, NRST asserts (depends on mapping)

11

Clearing OVHF fault MON2

11

11

Go to Bank 0

WR F0 00

RD 16 // 02 READ SINCE OVHF on MON2

WR 16 02 // WRITE 1(bit 2) to clear

```

Figure 7-7. MON2 Setting Software Example

#### 7.3.5 NRST

The NRST pin features a programmable reset delay time that can be adjusted from 0.2ms to 200ms when using TI\_CONTROL register. NRST is an open-drain output that should be pulled up through a  $1k\Omega$  to  $100k\Omega$  pullup resistor. When the device is powered up and POR is complete, NRST is asserted low until the BIST is complete. After the BIST, NRST remains high (not asserted) until it is triggered by a mappable fault condition. An NRST\_MISMATCH fault will be asserted if the NRST pin is pulled to an unexpected state. For example, if the NRST pin is in a high-impedance state (logic high) and is externally pulled low, then an NRST\_MISMATCH fault will assert. During an NRST toggle NRST mismatch will be active after  $2\mu s$ , NRST must exceed 0.6\*VDD to be considered in a logic high state.

NRST is mappable to the watchdog fault, and the ESM fault when using the IEN\_VENDOR register. If NRST is mapped to the ESM fault, the NRST pin will be asserted following the ESM delay and will be de-asserted after the reset delay ( $t_D$ ). If NRST is mapped to the watchdog fault, the NRST pin will be asserted during a watchdog fault and de-assert following the reset delay ( $t_D$ ).

NRST is also mappable to the OVHF and UVHF faults using the FC\_LF[n] registers. If a monitored voltage falls or rises outside of the programmed OVHF and UVHF thresholds, then NRST is asserted, driving the NRST pin

Submit Document Feedback

Copyright © 2024 Texas Instruments Incorporated

low. When the monitored voltage comes back into the valid window, a reset delay circuit is enabled that holds NRST low for a specified reset delay period (t<sub>D</sub>). Note if NRST is un-mapped from OVHF and UVHF faults while NRST is asserted then NRST will deassert, NRST will reassert when re-mapped assuming the voltage is still outside the valid window

The  $t_D$  period is determined by the RST\_DLY[2:0] value found in the TI\_CONTROL register. When the reset delay has elapsed, the NRST pin goes to a high-impedance state and uses a pullup resistor to hold NRST high. The pullup resistor must be connected to the proper voltage rail to allow other devices to be connected at the correct interface voltage. To ensure proper voltage levels, give some consideration when choosing the pullup resistor values. The pullup resistor value is determined by output logic low voltage (VOL), capacitive loading, and leakage current.

#### 7.3.6 NIRQ

NIRQ is a interrupt error ouput with latched behavior, if a monitored voltage falls or rises outside of the programmed OVHF and UVHF thresholds NIRQ is asserted. NIRQ will remain in its low state until the action causing the fault is no longer present and a 1-to-clear is written to the bit signaling the fault. Un-mapping NIRQ from a fault reporting register will not de-assert the NIRQ signal. NIRQ is In a typical TPS389C03-Q1 application, the NIRQ output is connected to a reset or enable input of a processor [such as a digital signal processor (DSP) or application-specific integrated circuit (ASIC), or other processor type].

The TPS389C03-Q1 has an open drain active low output that requires a pull-up resistor to hold these lines high to the required voltage logic. Connect the pull-up resistor to the proper voltage rail to enable the output to be connected to other devices at the correct interface voltage levels. To ensure proper voltage levels, give some consideration when choosing the pull-up resistor values. The pull-up resistor value is determined by  $V_{OL}$ , output capacitive loading, and output leakage current. These values are specified in Section 6. The open drain output can be connected as a wired-OR logic with other open drain signals such as another TPS389C03-Q1 NIRQ pin.

#### 7.3.7 ADC

The ADC used in the TPS389C03Q-1 runs on a 1MHz clock with an effective sampling rate of 1/8MHz (= 125kHz). Initially, the ADC records with a resolution of 12 bits (1LSB = 0.41667mV) which is later round off to 8-bit data for I<sup>2</sup>C transaction. (1LSB = 5mV) The ADC uses ping-pong architecture in which it requires 2us for both sampling and conversion per channel with a total of 2 sampling channels. While CH0 performs coarse conversion, CH1 does fine conversion and vice verse.

Digitized 8-bit data is updated once the fine conversion is completed, which occurs once every 8µs. Each I<sup>2</sup>C transaction initiated for reading 8-bit MON\_LVL data (the ADC data of a particular channel), 8-bit data is paused from updating until the I<sup>2</sup>C transaction completes.

Voltage scaling is done using a resistor ladder, but for differential mode channels, a chopping circuit is used to get the average of both of the voltages (VMON + VMON\_RS)/2 since VMON\_RS can be negative and can't be converted into an ADC code. VMON – VMON\_RS is calculated digitally by subtracting ((VMON + VMON\_RS) /2) from VMON and then multiplying by 2.

The MONX channels can be configured in 1x (0.2V to 1.475V) or 4x mode (0.8V to 5.5V). For differential mode channels configured in 1x mode, (MON1 and MON2) the ADC range is limited up to 1.7V. To configure an ADC channel above 1.7V, please use 4x mode.

Real time voltage measurements use.

$$V_{|V|} = ((ADC[7:0] * 5mV) + 0.2) * (VRANGE_MULT)$$

(1)

- 1. ADC[7:0] is translated to a corresponding decimal value. The value of ADC[7:0] corresponding to MON2-MON4 can be read from BANK0, registers 0x41 to 0x43 found in Section 8.1.1.

- 2. VRANGE\_MULT corresponds to the selected monitor voltage multiplier set in BANK1, register 0x1F of Section 8.1.2

- 3. VRANGE MULT is set to a decimal 1 or 4 value depending on monitored value.

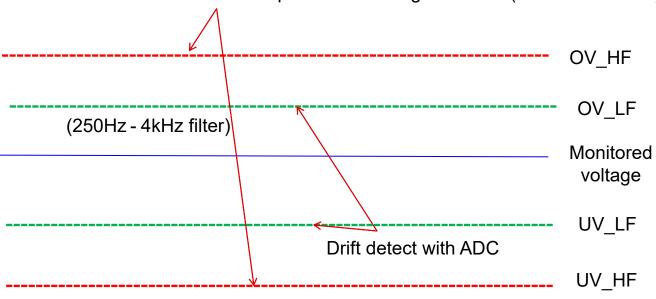

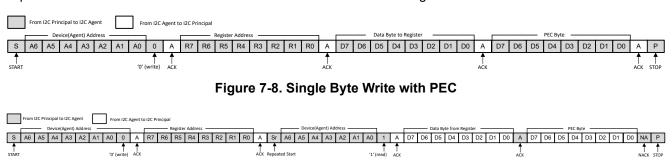

#### 7.3.8 Packet Error Checking (PEC)

TPS389C03-Q1 supports Packet Error Checking (PEC) as a way to implement Cyclic Redundancy Checking (CRC). PEC is a dynamic CRC that happens only during read or write transactions if enabled. With the initial value of CRC set to 0x00, the PEC uses a CRC-8 represented by the polynomial:

$$C(x) = x^8 + x^2 + x + 1 \tag{2}$$

The polynomial is meant to catch any bit flips or noise in I2C communication which cause data and PEC byte to have a mismatch. The PEC calculation includes all bytes in the transmission, including address, command and data. The PEC calculation does not include ACK or NACK bits or START, STOP or REPEATED START conditions. If PEC is enabled, and the TPS389C03-Q1 is transmitting data, then the TPS389C03-Q1 is responsible for sending the PEC byte. If PEC is enabled, and the TPS389C03-Q1 is reveiving data from the MCU, then the MCU is responsible for sending the PEC byte. In case of faster communications needs like servicing the watchdog the required PEC feature can be effectively used to handle missing PEC information and to avoid triggering faults. Figure 7-8 and Figure 7-9 highlight the communication protocol flow when PEC is required and which device controls SDA line at various instances during active communication.

Figure 7-9. Single Byte Read with PEC

Table 7-3 summarises the registers associated with a PEC Write command and resulting device behavior. Table 7-4 summarises the registers associated with a PEC Read command and resulting device behavior.

Copyright © 2024 Texas Instruments Incorporated Product Folder Links: *TPS389C03-Q1*

### Table 7-3. PEC Write Summary

| EN_PEC | REQ_PEC | PEC_INT | Interrupt Status                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------|---------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0      | х       | х       | PEC byte is not required in write operation, NO NIRQ assertion.                                                                                                                                                                                                                                                                                                                                                           |

| 1      | 0       | х       | A write command missing a PEC byte is treated as OK, the write command will execute and result in a I2C ACT. A write command with an incorrect PEC is treated as an error, the write command will not execute and result in a I2C NACK. NO NIRQ assertion.                                                                                                                                                                |

| 1      | 1       | 0       | A missing PEC is treated as an error, a write command will only execute if the correct PEC byte is provided. I2C communication will still respond with an ACT although write command did not execute. A write command with an incorrect PEC is treated as an error, the write command will not execute and result in a I2C NACK. NO NIRQ assertion.                                                                       |

| 1      | 1       | 1       | A missing PEC is treated as an error, a write command will only execute if the correct PEC byte is provided. I2C communication will still respond with an ACT although write command did not execute. A write command with an incorrect PEC is treated as an error, the write command will not execute and result in a I2C NACK. NIRQ is asserted when a write command with a incorrect or missing PEC byte is attempted. |

#### Table 7-4. PEC Read Summary

| EN_PEC | REQ_PEC | PEC_INT | Interrupt Status                                                                                                                      |

|--------|---------|---------|---------------------------------------------------------------------------------------------------------------------------------------|

| 0      | х       | х       | I2C read operation will repond with data stored in register, I2C read command will not respond with registers corresponding PEC byte. |

| 1      | х       | х       | I2C read operation will repond with data stored in register and corresponding PEC byte.                                               |

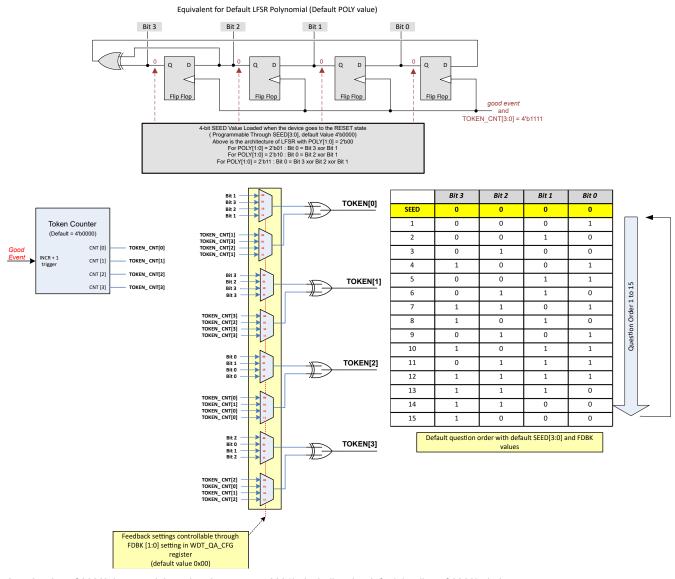

#### 7.3.9 Q&A Watchdog

The Question and Answer Watchdog requires specific data to be sent from the MCU to the TPS389C03-Q1 within a specific time interval.

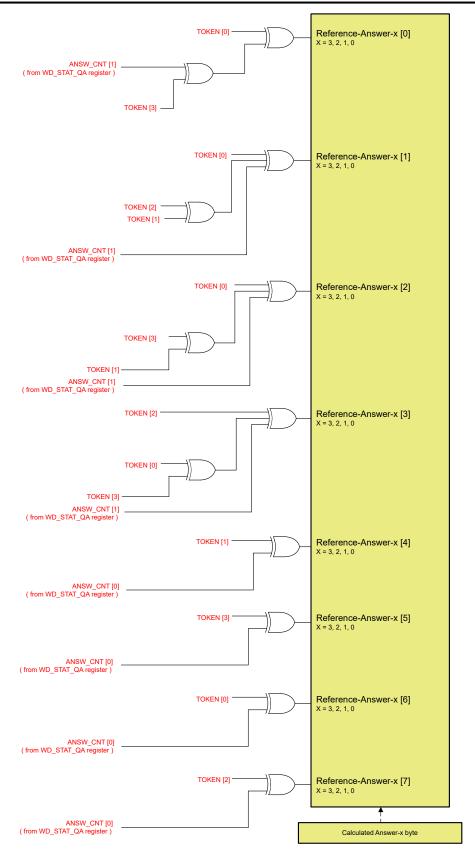

The TPS389C03-Q1 generates questions for the MCU to read during the OPEN and CLOSE windows. Questions are read as the combination of ANSW\_CNT[1:0] and TOKEN[3:0] status bits found in the WD\_STAT\_QA register in BANK0. After reading a question, the MCU calculates the Reference Answer using the logic equations shown in Figure 7-10 and responds by writing the 8-bit answer into the WDT\_ANSWER register in BANK1. A code example for Reference Answer calculation is shown in Figure 7-13. For a typical application, changing the value of FDBK[1:0], found in the WDT\_QA\_CFG register in BANK1, from the default value of FDBK[1:0] = 00b is not required. However, FDBK[1:0] can be changed if a different Reference Answer calculation is needed. Question generation and answer calculations are explained in more detail in Section 7.3.9.1.

Figure 7-10. Watchdog Answer Calculation for FDBK[1:0] = 00b

During one "event," the TPS389C03-Q1 generates three questions within the CLOSE window and one question within the OPEN window. The MCU must correctly read and answer all three questions within the specified CLOSE window and the question within the specified OPEN window for a "good event" to occur. At the start of an event, ANSW\_CNT[1:0] = 11b. A correctly answered question decrements ANSW\_CNT[1:0] to generate the next question. Once a good event occurs, ANSW\_CNT[1:0] is reset to ANSW\_CNT[1:0] = 11b, and the value of TOKEN[3:0] changes to generate a new set of questions for the next event.

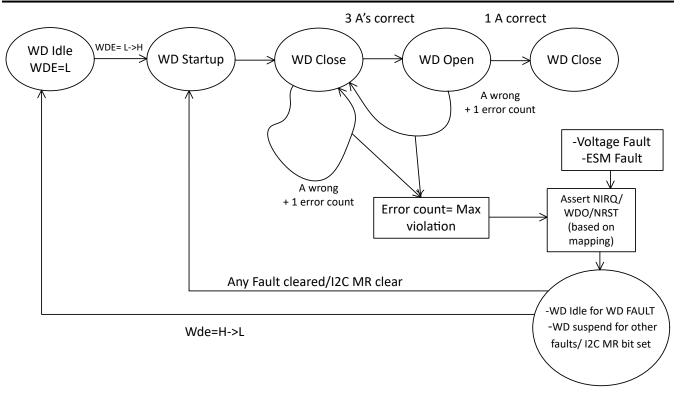

An incorrectly answered question increments the violation count, resets the ANSW\_CNT[1:0] to ANSW\_CNT[1:0] = 11b, and restarts the CLOSE window. The maxmimum violation count, MAX\_VIOLATION\_COUNT[2:0], is programmed using the WDT\_CFG register in BANK1. When the violation count reaches its maximum value, the TPS389C03-Q1 WDO (latched) low, and may assert NIRQ and NRST low depending on the fault mapping. Note if NIRQ is un-mapped from watchdog fault reporting while NIRQ is asserted then NIRQ will deassert, NIRQ will reassert when re-mapped assuming the fault has not been cleared. A good event decrements the violation count if the violation count is not already equal to zero. When the watchdog enters the Idle state, the violation count is reset. When the the watchdog enters the suspend state, the violation count remains unchanged. The watchdog state diagram is illustrated in Figure 7-22.

Within an event, the CLOSE window time is a fixed value, and does not change if all three questions are answered faster than the set time. For example, if the CLOSE window time is set to 10ms, and the three questions are correctly answered in 5 ms, then the TPS389C03-Q1 will wait the remaining 5 ms before transitioning to the OPEN window. During the OPEN window, if the question is answered faster than the selected OPEN window time, then the TPS389C03-Q1 automatically transitions on to the next event's CLOSE window. An incorrectly answered question within either the CLOSE or OPEN windows results in the TPS389C03-Q1 restarting the CLOSE window.

#### 7.3.9.1 Question and Token Generation

A question is presented to the MCU as a combination of the TOKEN[3:0] and the ANSW\_CNT[1:0] status bits found in the WD\_STAT\_WA register. ANSW\_CNT[1:0] has a default value of ANSW\_CNT[1:0] = 11b and is decremented when a question is answered correctly. The value of ANSW\_CNT[1:0] is reset to ANSW\_CNT[1:0] = 11b when a question is answered incorrectly or a good event is completed.

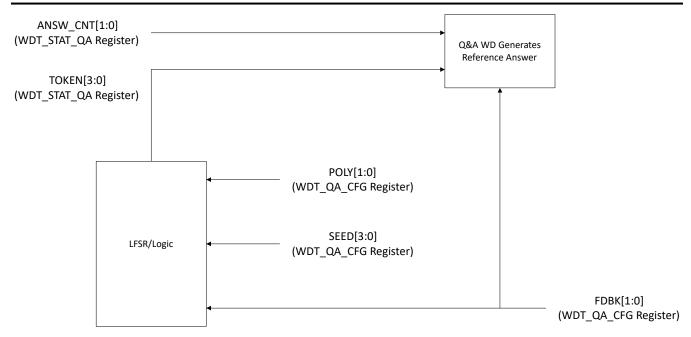

The watchdog uses the Token Counter (TOKEN\_CNT[3:0] bits Figure 7-12) and a Linear Feedback Shift Register (LFSR) to generate the 4-bit TOKEN[3:0]. The LFSR architecture can be configured using POLY[1:0] in the WDT\_QA\_CFG register in BANK1 as shown in Figure 7-12. In a typical application, it is not necessary to change the value of POLY[1:0] from the default 00b. However, POLY[1:0] can be configured if a different LFSR architecture is required. The diagram illustrated in Figure 7-11 represents how questions are generated by the watchdog.

During the watchdog startup state, the LFSR is set with the initial value SEED[3:0], which is located in the WDT QA CFG register in BANK1. SEED[3:0] has a default value of 0000b.

Figure 7-11. Watchdog Question Generation

At the end of a good event, the Token Counter is incremented, and the value of TOKEN[3:0] will change as a result of the mux and logic combinations shown in Figure 7-12.

A. A value of 0000b is a special seed and equates to 0001b, including the default loading of 0000b during power up.

Figure 7-12. Watchdog Question and Token Generation

Once the Token Counter has reached the maximum value of 1111b, the counter will reset and provide a clock pulse to the LFSR. The clock pulse will left shift the value stored in the LFSR, which changes the value of the TOKEN[3:0]. During the special case of SEED[3:0] = 0000b, Bit 0 of the LFSR will be incremented the first time the Token Counter resets. Subsequent Token Counter resets will provide the typical clock pulse that left-shifts the LFSR. While left shifting, the value of seed will cycle through values 1 to 15 as listed in Figure 7-12.

The mux devices that generate TOKEN[3:0] are configured using FDBK[1:0] (WDT\_QA\_CFG register in BANK1). It is not necessary to change the value of FDBK[1:0] from the default value of 00b, and it is important to note that changing FDBK[1:0] also changes the logic equations required to calculate the reference answer. The different reference answer logic equations are listed below:

For FDBK[1:0] = 00b:

- Reference-Answer[0] = TOKEN[0] XOR (TOKEN[3] XOR ANSW CNT[1])

- Reference-Answer[1] = TOKEN[0] XOR (TOKEN[1] XOR TOKEN[2]) XOR ANSW CNT[1]

- Reference-Answer[2] = TOKEN[0] XOR (TOKEN[3] XOR TOKEN[1]) XOR ANSW CNT[1]

- Reference-Answer[3] = TOKEN[2] XOR (TOKEN[0] XOR TOKEN[3]) XOR ANSW\_CNT[1]

- Reference-Answer[4] = TOKEN[1] XOR ANSW\_CNT[0]

- Reference-Answer[5] = TOKEN[3] XOR ANSW CNT[0]

- Reference-Answer[6] = TOKEN[0] XOR ANSW CNT[0]

- Reference-Answer[7] = TOKEN[2] XOR ANSW\_CNT[0]

#### For FDBK[1:0] = 01b:

- Reference-Answer[0] = TOKEN[1] XOR (TOKEN[2] XOR ANSW CNT[1])

- Reference-Answer[1] = TOKEN[1] XOR (TOKEN[1] XOR TOKEN[1]) XOR ANSW CNT[1]

- Reference-Answer[2] = TOKEN[3] XOR (TOKEN[2] XOR TOKEN[1]) XOR ANSW CNT[1]

- Reference-Answer[3] = TOKEN[1] XOR (TOKEN[3] XOR TOKEN[3]) XOR ANSW\_CNT[1]

- Reference-Answer[4] = TOKEN[0] XOR ANSW CNT[0]

- Reference-Answer[5] = TOKEN[2] XOR ANSW CNT[0]

- Reference-Answer[6] = TOKEN[3] XOR ANSW\_CNT[0]

- Reference-Answer[7] = TOKEN[1] XOR ANSW\_CNT[0]

### For FDBK[1:0] = 10b:

- Reference-Answer[0] = TOKEN[2] XOR (TOKEN[1] XOR ANSW\_CNT[1])

- Reference-Answer[1] = TOKEN[2] XOR (TOKEN[0] XOR TOKEN[1]) XOR ANSW\_CNT[1]

- Reference-Answer[2] = TOKEN[1] XOR (TOKEN[1] XOR TOKEN[1]) XOR ANSW\_CNT[1]

- Reference-Answer[3] = TOKEN[0] XOR (TOKEN[2] XOR TOKEN[3]) XOR ANSW CNT[1]

- Reference-Answer[4] = TOKEN[2] XOR ANSW\_CNT[0]

- Reference-Answer[5] = TOKEN[1] XOR ANSW CNT[0]

- Reference-Answer[6] = TOKEN[2] XOR ANSW\_CNT[0]

- Reference-Answer[7] = TOKEN[0] XOR ANSW CNT[0]

#### For FDBK[1:0] = 11b

- Reference-Answer[0] = TOKEN[3] XOR (TOKEN[0] XOR ANSW\_CNT[1])

- Reference-Answer[1] = TOKEN[3] XOR (TOKEN[3] XOR TOKEN[1]) XOR ANSW\_CNT[1]

- Reference-Answer[2] = TOKEN[1] XOR (TOKEN[0] XOR TOKEN[1]) XOR ANSW CNT[1]

- Reference-Answer[3] = TOKEN[3] XOR (TOKEN[1] XOR TOKEN[3]) XOR ANSW\_CNT[1]

- Reference-Answer[4] = TOKEN[3] XOR ANSW CNT[0]

- Reference-Answer[5] = TOKEN[0] XOR ANSW\_CNT[0]

- Reference-Answer[6] = TOKEN[1] XOR ANSW CNT[0]

- Reference-Answer[7] = TOKEN[3] XOR ANSW\_CNT[0]

Example code for answer calcultion when FDBK[1:0] = 00b is included in Figure 7-13.

#### Expression

```

[Locals Answer[7] = Locals WDT_status_Bin[2] ^ Locals WDT_status_Bin[4],

Locals Answer[6] = Locals WDT_status_Bin[0] ^ Locals WDT_status_Bin[4],

Locals Answer[5] = Locals WDT_status_Bin[3] ^ Locals WDT_status_Bin[4],

Locals Answer[4] = Locals WDT_status_Bin[1] ^ Locals WDT_status_Bin[4],

Locals Answer[4] = Locals WDT_status_Bin[1] ^ Locals WDT_status_Bin[0] ^ Locals WDT

```

Figure 7-13. Watchdog Answer Calculation Code for FDBK[1:0] = 00b

#### 7.3.9.2 Q&A Watchdog Open and Close Window Delay

TPS389C03-Q1 offers a Open and Close window delay accuracy of ±5%, window delay can be adjusted through register 0xAC and 0xAB respectively. During a reset event, the Open and Close window delays do not change

from the programmed value (default OTP or user changes). Table 7-5 lists delay time and associated register value.

Table 7-5. Open and Close Window Delay

| Reg Value | Time       | Notes     |

|-----------|------------|-----------|

| 0-31      | 1-32ms     | 1ms steps |

| 32-63     | 34-96 ms   | 2ms steps |

| 64-255    | 100-864 ms | 4ms steps |

The startup delay is calculated using the WDT\_Startup\_DLY\_MULTIPLIER[2:0] (register 0xAA), Close window delay, and the Open window delay. It is important to note that changing either the Close window delay or the Open window delay changes the resulting startup delay. Use Equation 3 to calculate total startup delay.

$$t_{Startup} = (WDT_Startup_DLY_MULTIPLIER+1)*(WDT_OPEN+WDT_CLOSE)$$

(3)

#### 7.3.9.3 Q&A Watchdog Status Register

Read status register 0x37 to determine watchdog state of operation. Table 7-6 provides the operating state with its associated value. Bits ST\_WDUV and ST\_WDEXP of register 0x37 are cleared when read.

Table 7-6. Q&A Watchdog Operating State

| OPERATING STATE | STATE<br>DESCRIPTION                                                                                                                                   | VALUE |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| IDLE            | WD is wating for a fault to be cleared or WDE is low. The violation count is reset.                                                                    | 0x00  |

| OPEN            | WD open window.                                                                                                                                        | 0x01  |

| CLOSE           | WD close window.                                                                                                                                       | 0x02  |

| START UP        | WD startup window.                                                                                                                                     | 0x03  |

| SUSPEND         | WDE is high and another fault has asserted output pins unrelated to the WD, or I <sup>2</sup> C MR bit is set to 1. Violation count remains unchanged. | 0x04  |

Copyright © 2024 Texas Instruments Incorporated

Submit Document Feedback

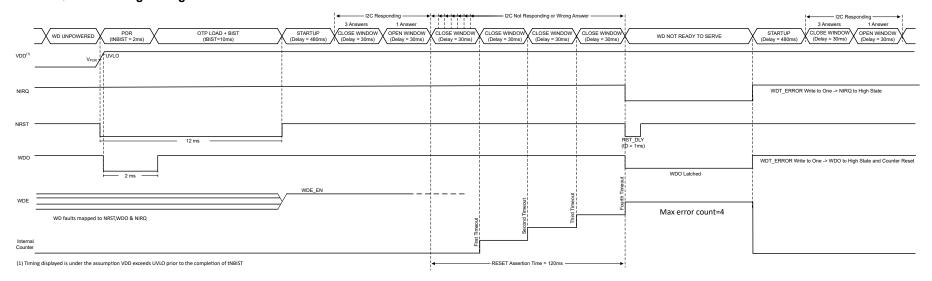

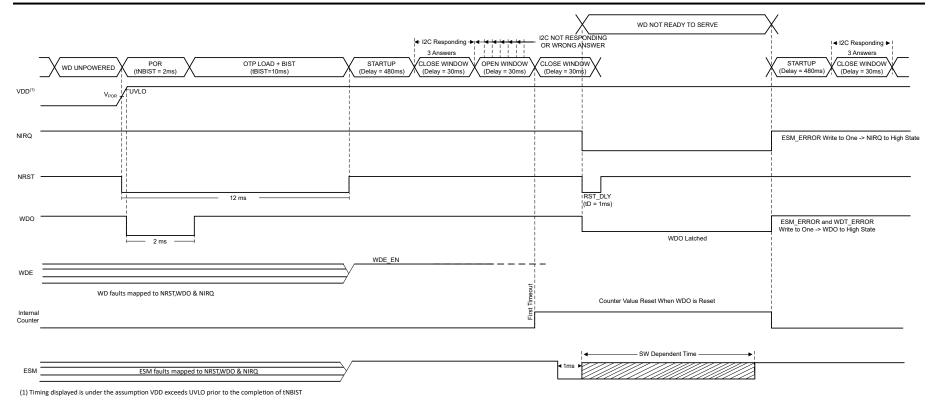

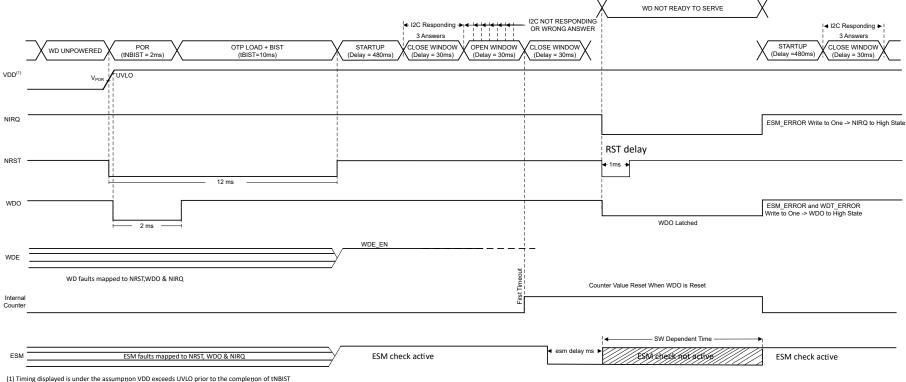

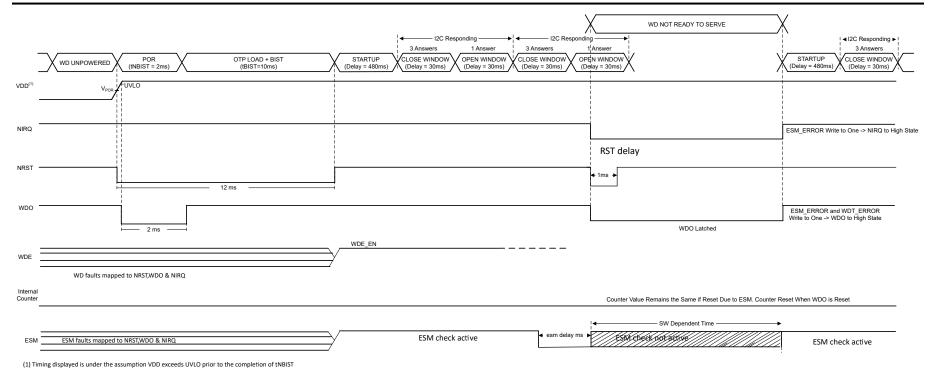

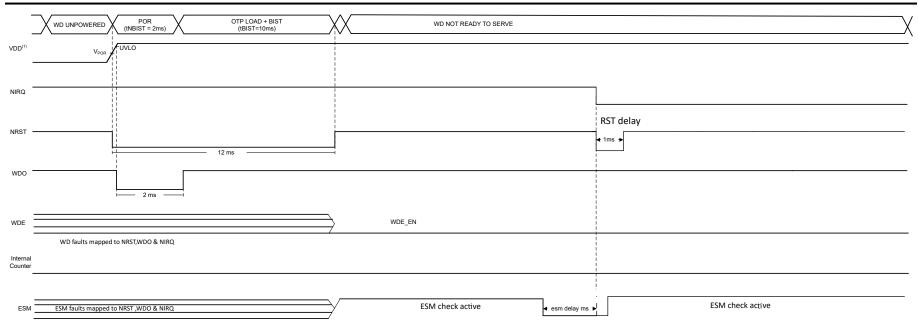

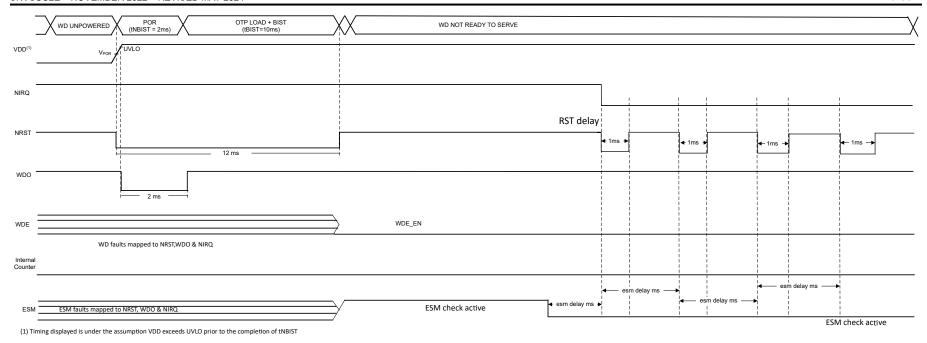

#### 7.3.9.4 Q&A Watchdog Timing

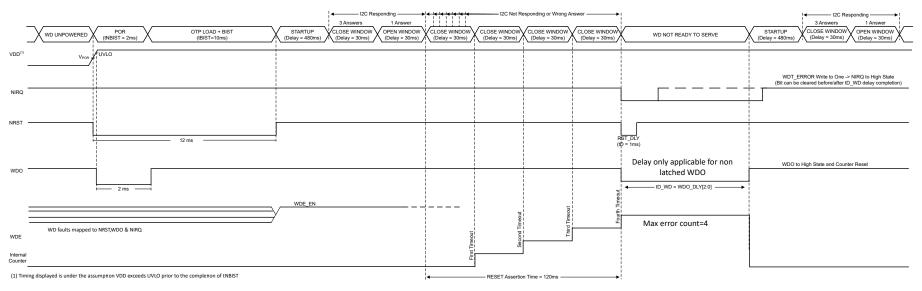

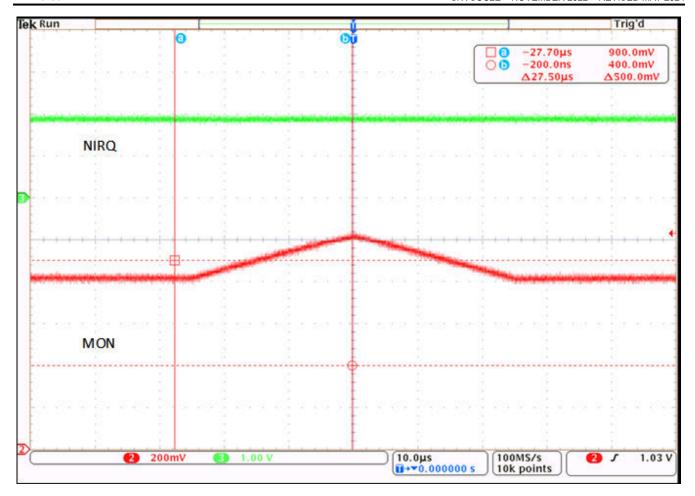

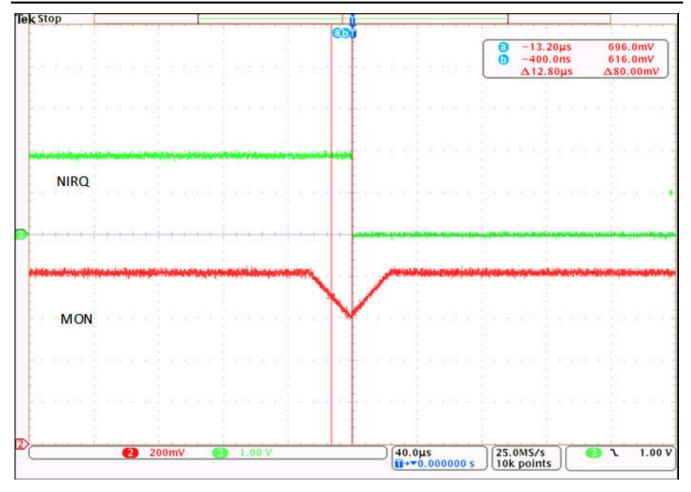

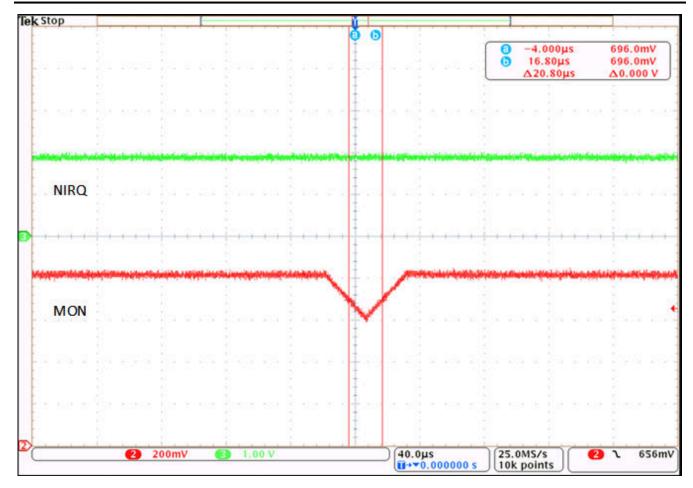

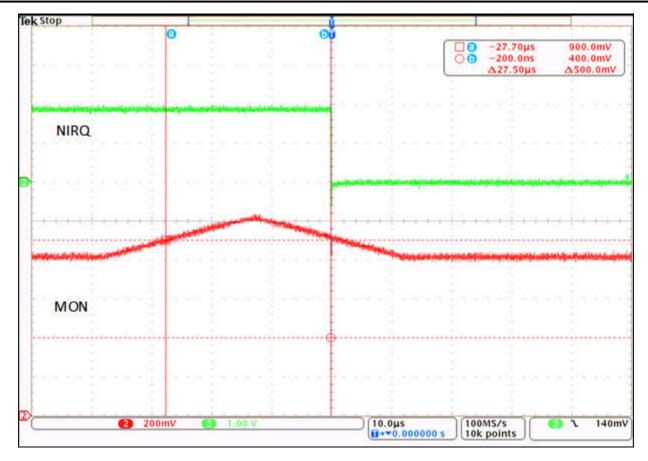

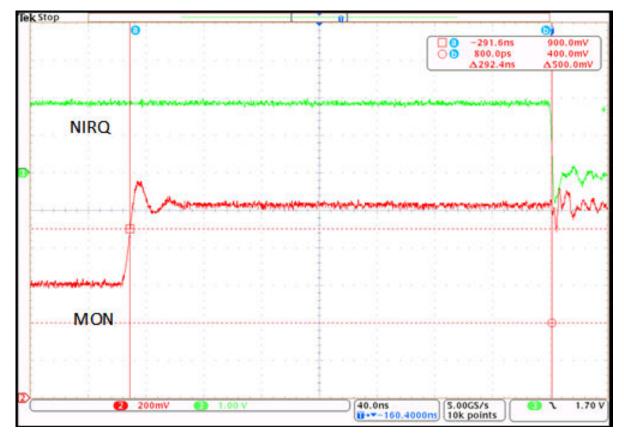

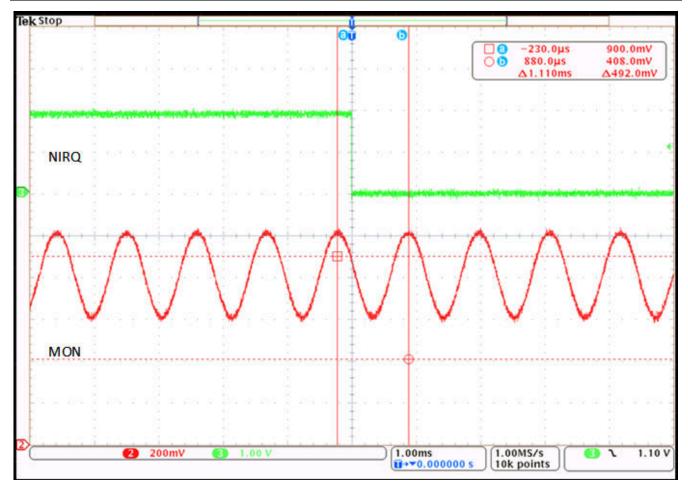

Figure 7-14. TPS389C03 CLOSE Window Error WDO Latched

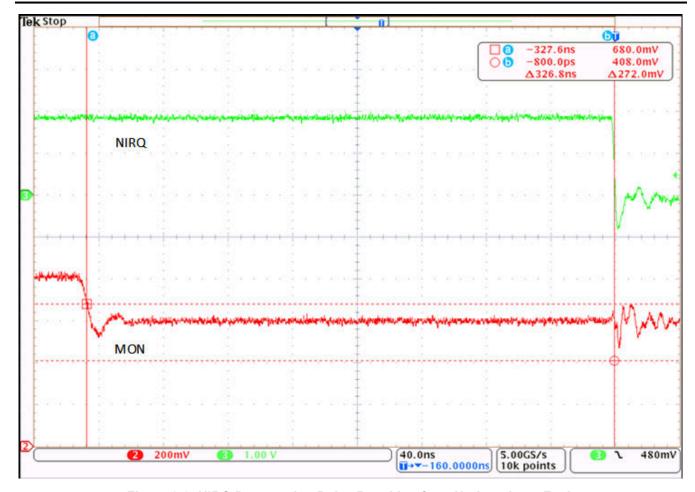

Figure 7-15. TPS389C03 CLOSE Window Error WDO Delay

Figure 7-16. TPS389C03 CLOSE Window Error WDO Delay with Max Violation Count Reached

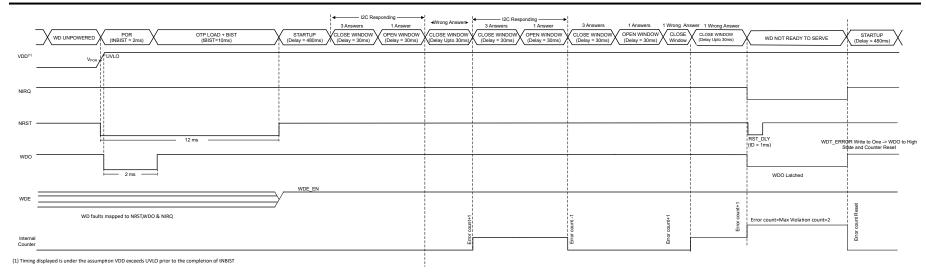

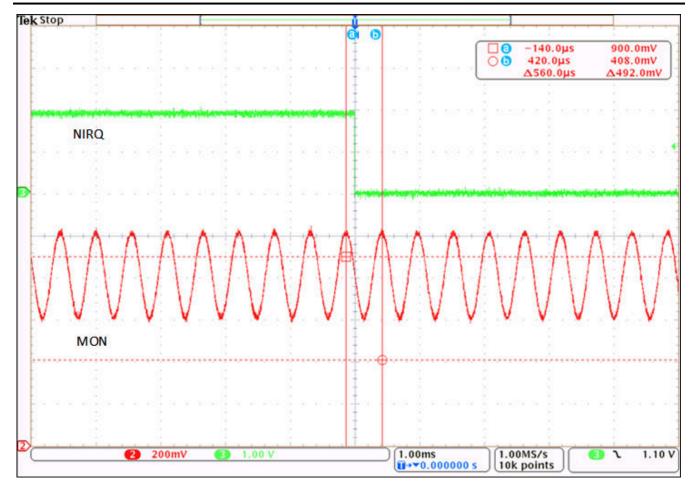

Figure 7-17. TPS389C03 OPEN Window Error WDO Latched

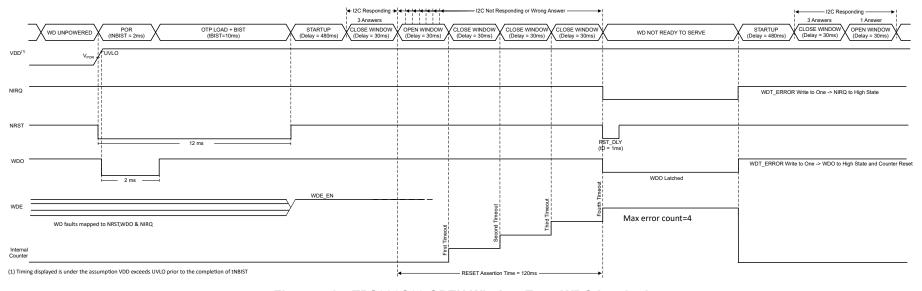

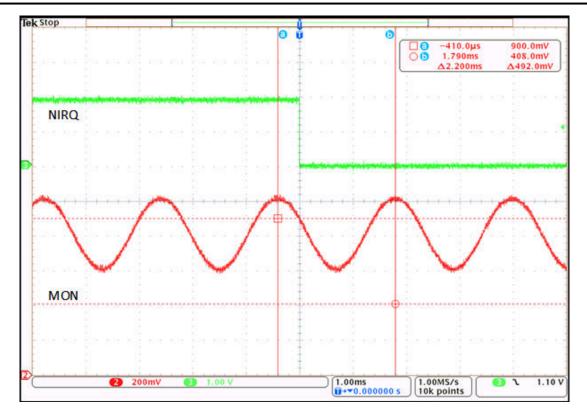

Figure 7-18. TPS389C03 ESM Error with No WD Faults

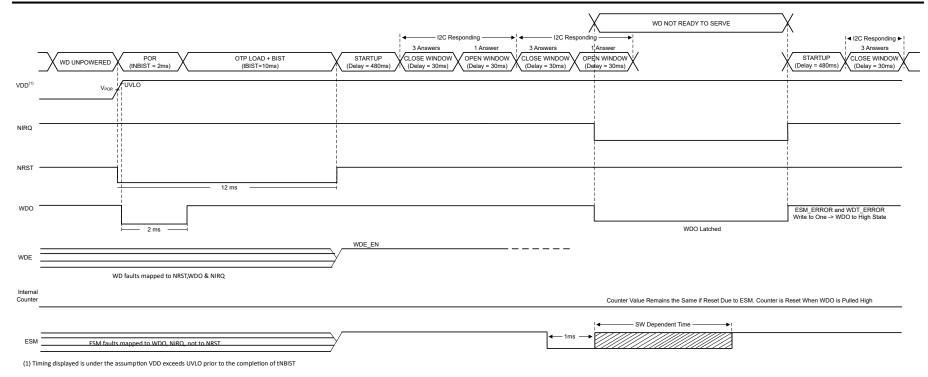

Figure 7-19. TPS389C03 ESM Error After WD Time-out

Copyright © 2024 Texas Instruments Incorporated

Submit Document Feedback

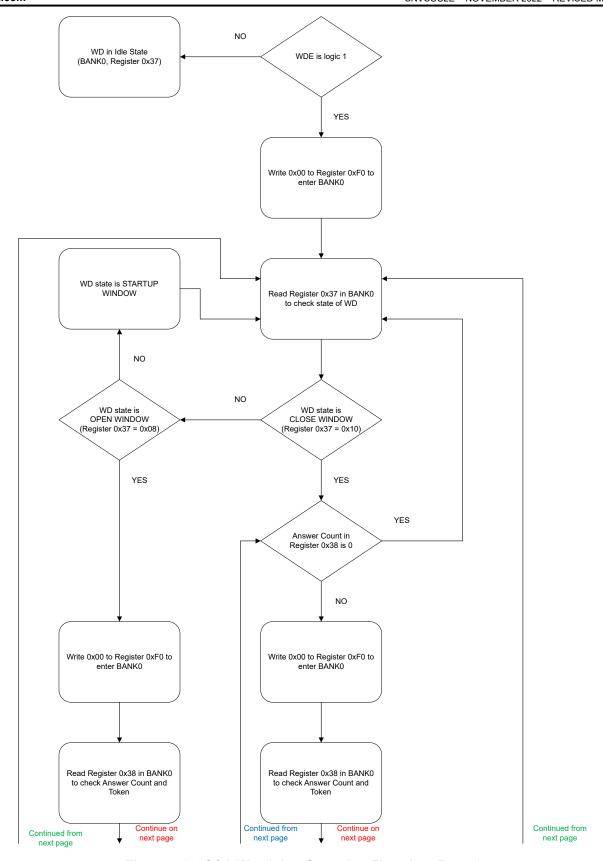

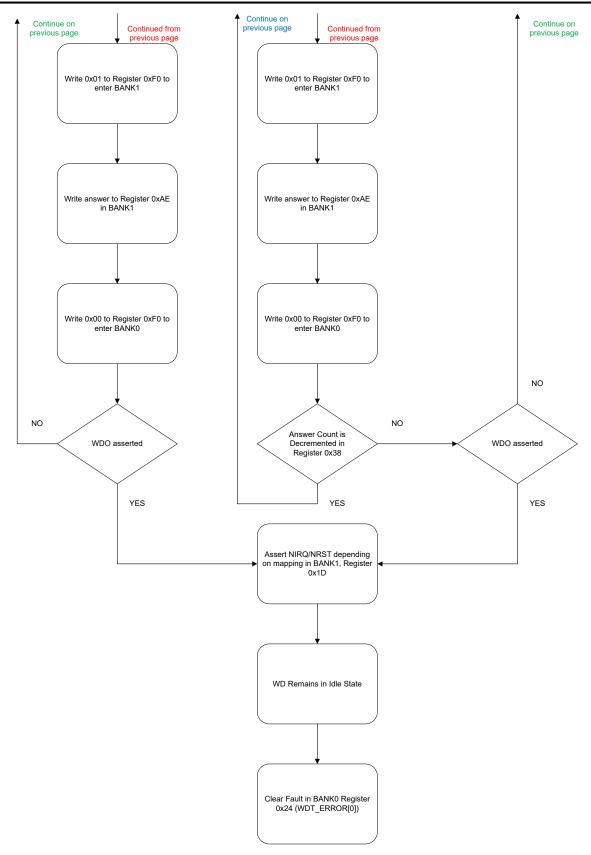

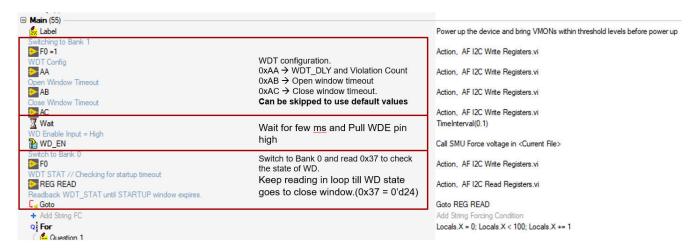

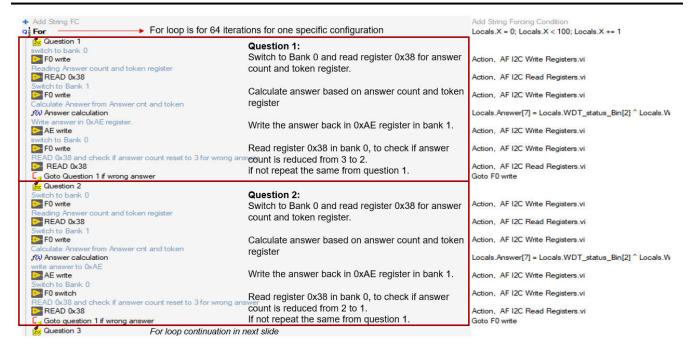

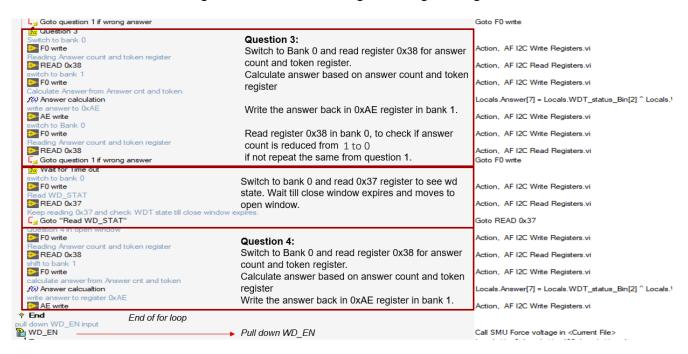

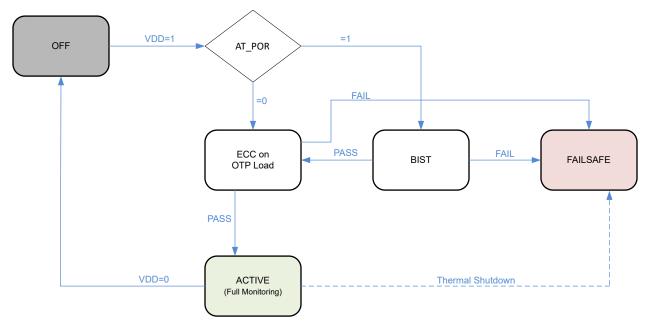

### 7.3.9.5 Q&A Watchdog State Machine and Test Program

The flowchart shown in Figure 7-20 and Figure 7-21 describes the operation of the Q&A watchdog with an MCU. The associated state machine diagram drawn in Figure 7-22 is referenced to Table 7-6 and describes the transition between states for the Q&A watchdog.

The single test program in Figure 7-23 to Figure 7-25 demonstrates how the watchdog can be tested.

Figure 7-20. Q&A Watchdog Operation Flowchart Page 1

Figure 7-21. Q&A Watchdog Operation Flowchart Page 2

Figure 7-22. Q&A Watchdog State Diagram

Figure 7-23. Q&A Watchdog Test Program Page 1

Figure 7-24. Q&A Watchdog Test Program Page 2

Figure 7-25. Q&A Watchdog Test Program Page 3

#### 7.3.10 Error Signal Monitoring (ESM)