# STM706T/S/R, STM706P, STM708T/S/R

3 V supervisor

#### Datasheet - production data

- RST and RST outputs

- 200 ms (typ.) t<sub>rec</sub>

- Watchdog timer 1.6 s (typ.)

- Manual reset input (MR)

- Power-fail comparator (PFI/PFO)

- Low supply current 40 μA (typ.)

- Guaranteed RST (RST) assertion down to V<sub>CC</sub> = 1.0 V

- Operating temperature: -40 °C to 85 °C (industrial grade)

- RoHS compliance

- Lead-free components are compliant with the RoHS directive

## **Application**

- Computers

- Controllers

- · Intelligent instruments

#### **Features**

- Precision V<sub>CC</sub> monitor

- T: 3.00 V  $\leq$  V<sub>RST</sub>  $\leq$  3.15 V

- S: 2.88 V  $\,\leq\,$  V  $_{RST}$   $\,\leq\,$  3.00 V

- R: STM706P: 2.59 V  $\leq$  V<sub>RST</sub>  $\leq$  2.70 V

Table 1. Device summary

|             | Watchdog<br>input | Watchdog<br>output <sup>(1)</sup> | Active-low<br>RST (1) | Active-high<br>RST <sup>(1)</sup> | Manual reset input | Power-fail comparator |

|-------------|-------------------|-----------------------------------|-----------------------|-----------------------------------|--------------------|-----------------------|

| STM706T/S/R | $\sqrt{}$         | V                                 | $\sqrt{}$             |                                   | $\sqrt{}$          | $\sqrt{}$             |

| STM706P (2) | V                 | V                                 |                       | V                                 | V                  | V                     |

| STM708T/S/R |                   |                                   | V                     | V                                 | V                  | V                     |

- 1. Push-pull output

- 2. The STM706P device is identical to the STM706R device, except its reset output is active high.

# **Contents**

| 1 | Desc  | cription                                                      | 6  |

|---|-------|---------------------------------------------------------------|----|

| 2 | Pin o | descriptions                                                  | 9  |

|   | 2.1   | MR                                                            | 9  |

|   | 2.2   | WDI                                                           | 9  |

|   | 2.3   | WDO                                                           | 9  |

|   | 2.4   | RST                                                           | 9  |

|   | 2.5   | RST                                                           | 9  |

|   | 2.6   | PFI                                                           | 9  |

|   | 2.7   | PFO                                                           | 10 |

| 3 | Ope   | ration                                                        | 12 |

|   | 3.1   | Reset output                                                  | 12 |

|   | 3.2   | Push-button reset input                                       | 12 |

|   | 3.3   | Watchdog input (STM706T/S/R and STM706P)                      | 12 |

|   | 3.4   | Watchdog output (STM706T/S/R and STM706P)                     | 12 |

|   | 3.5   | Power-fail input/output                                       | 13 |

|   | 3.6   | Ensuring a valid reset output down to V <sub>CC</sub> = 0 V   | 13 |

|   | 3.7   | Interfacing to microprocessors with bi-directional reset pins | 14 |

| 4 | Турі  | cal operating characteristics                                 | 15 |

| 5 | Max   | imum ratings                                                  | 22 |

| 6 | DC a  | and AC parameters                                             | 23 |

| 7 | Pack  | kage information                                              | 27 |

|   | 7.1   | SO8 package information                                       | 28 |

|   | 7.2   | TSSOP8 3x3 (DS) package information                           | 29 |

| 8 | Part  | numbering                                                     | 30 |

| 9 | Revi  | ision history                                                 | 32 |

# List of tables

| Table 1.  | Device summary                                                           | 1    |

|-----------|--------------------------------------------------------------------------|------|

| Table 2.  | Signal names                                                             | 6    |

| Table 3.  | Pin description                                                          | 9    |

| Table 4.  | Absolute maximum ratings                                                 | . 21 |

| Table 5.  | Operating and AC measurement conditions                                  | . 22 |

| Table 6.  | DC and AC characteristics                                                | . 24 |

| Table 7.  | SO8 - 8-lead plastic small outline, 150 mils body width, mechanical data | . 27 |

| Table 8.  | TSSOP8 - 8-lead, thin shrink small outline, 3 x 3 mm body size,          |      |

|           | mechanical data                                                          | . 28 |

| Table 9.  | Ordering information scheme                                              | . 29 |

| Table 10. | Marking description                                                      | . 30 |

| Table 11. | Document revision history                                                | . 31 |

# **List of figures**

| Figure 1.  | Logic diagram (STM706T/S/R and STM706P)                                         | 5  |

|------------|---------------------------------------------------------------------------------|----|

| Figure 2.  | Logic diagram (STM708T/S/R)                                                     | 5  |

| Figure 3.  | STM706T/S/R and STM706P SO8 connections                                         | 6  |

| Figure 4.  | STM706T/S/R and STM706P TSSOP8 connections                                      | 6  |

| Figure 5.  | STM708T/S/R SO8 connections                                                     | 6  |

| Figure 6.  | STM708T/S/R TSSOP8 connections                                                  | 7  |

| Figure 7.  | Block diagram (STM706T/S/R and STM706P)                                         | 9  |

| Figure 8.  | Block diagram (STM708T/S/R)                                                     | 10 |

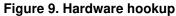

| Figure 9.  | Hardware hookup                                                                 | 10 |

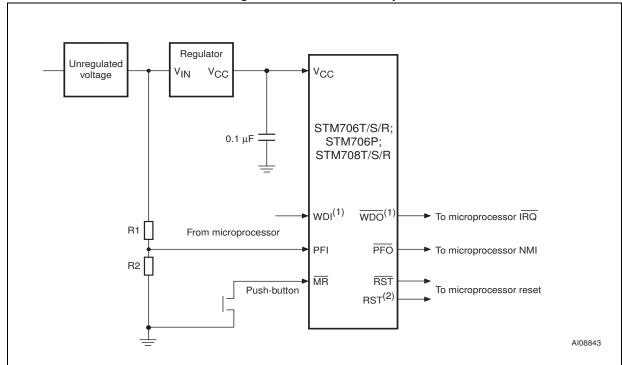

| Figure 10. | Reset output valid to ground circuit                                            | 12 |

| Figure 11. | Interfacing to microprocessors with bi-directional reset I/O                    | 13 |

| Figure 12. | Supply current vs. temperature (no load)                                        | 14 |

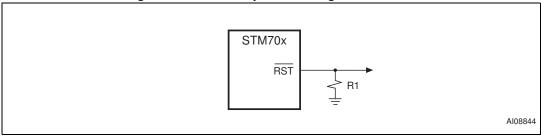

| Figure 13. | V <sub>PFI</sub> threshold vs. temperature                                      | 14 |

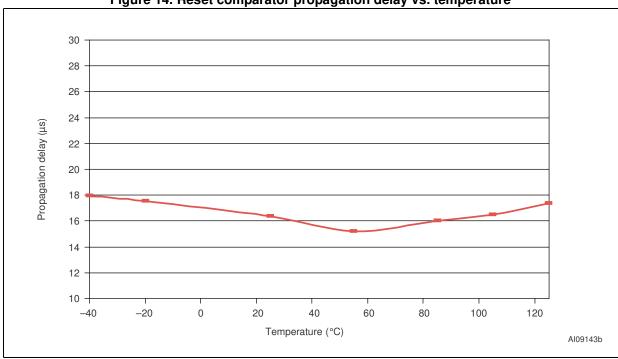

| Figure 14. | Reset comparator propagation delay vs. temperature                              | 15 |

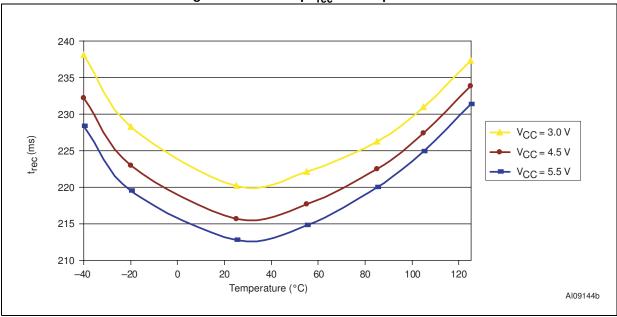

| Figure 15. | Power-up t <sub>rec</sub> vs. temperature                                       | 15 |

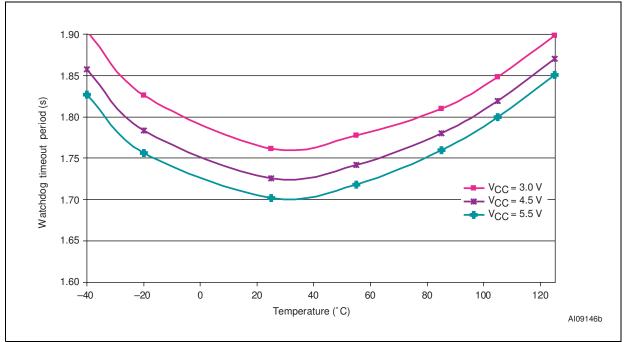

| Figure 16. | Normalized reset threshold vs. temperature                                      | 16 |

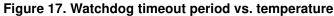

| Figure 17. | Watchdog timeout period vs. temperature                                         | 16 |

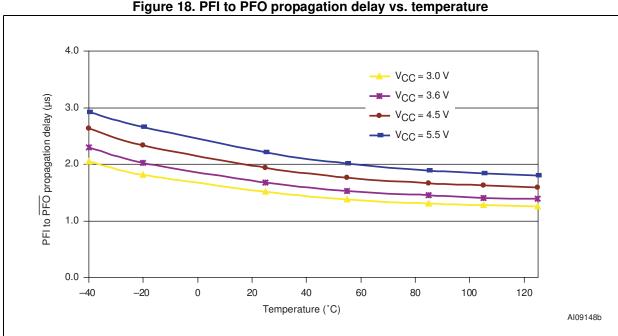

| Figure 18. | PFI to PFO propagation delay vs. temperature                                    | 17 |

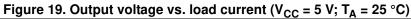

| Figure 19. | Output voltage vs. load current (V <sub>CC</sub> = 5 V; T <sub>A</sub> = 25 °C) | 17 |

| Figure 20. | RST output voltage vs. supply voltage                                           | 18 |

| Figure 21. | RST output voltage vs. supply voltage                                           | 18 |

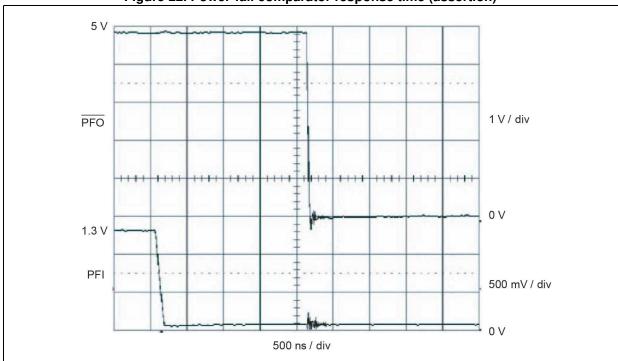

| Figure 22. | Power-fail comparator response time (assertion)                                 |    |

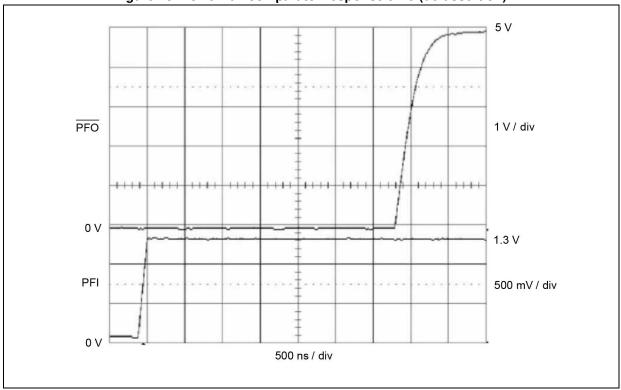

| Figure 23. | Power-fail comparator response time (de-assertion)                              |    |

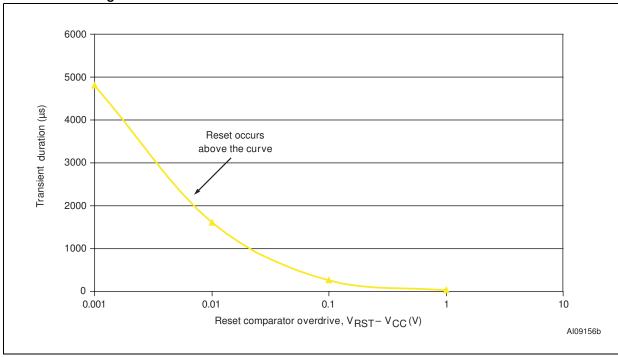

| Figure 24. | Maximum transient duration vs. reset threshold overdrive                        | 20 |

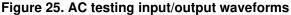

| Figure 25. | AC testing input/output waveforms                                               | 22 |

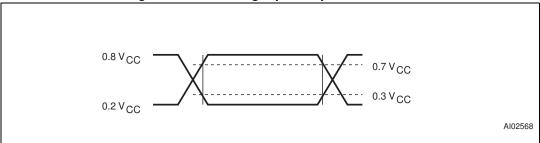

| Figure 26. | Power-fail comparator waveform                                                  |    |

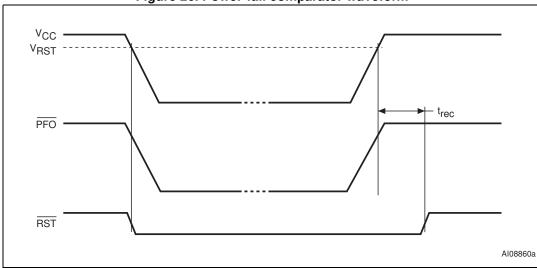

| Figure 27. | MR timing waveform                                                              | 23 |

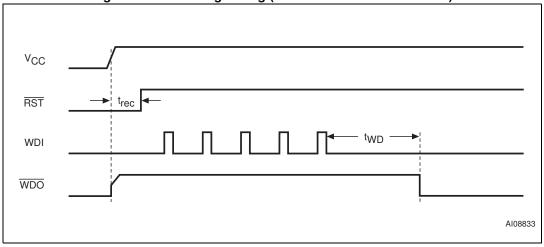

| Figure 28. | Watchdog timing (STM706T/S/R and STM706P)                                       | 23 |

| Figure 29. | SO8 - 8-lead plastic small outline, 150 mils body width, package outline        | 27 |

| Figure 30. | TSSOP8 - 8-lead, thin shrink small outline, 3 x 3 mm body size,                 |    |

|            | nackage outline                                                                 | 28 |

577

# 1 Description

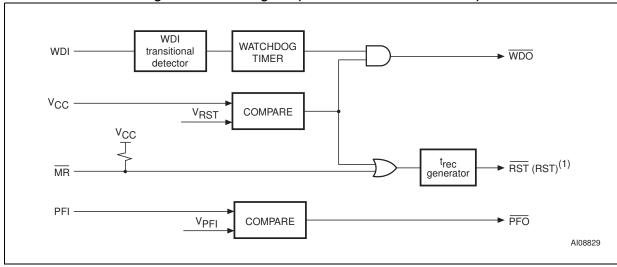

The STM70x supervisors are self-contained devices which provide microprocessor supervisory functions. A precision voltage reference and comparator monitors the  $V_{CC}$  input for an out-of-tolerance condition. When an invalid  $V_{CC}$  condition occurs, the reset output (RST) is forced low (or high in the case of RST).

These devices also offer a watchdog timer (except for STM708T/S/R) as well as a power-fail comparator to provide the system with an early warning of impending power failure.

The STM706P device is identical to the STM706R device, except its reset output is active high. These devices are available in a standard 8-pin SOIC package or a space-saving 8-pin TSSOP package.

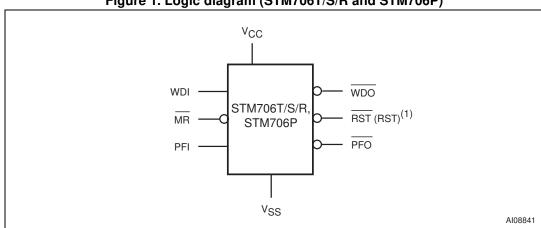

Figure 1. Logic diagram (STM706T/S/R and STM706P)

1. For STM706P only.

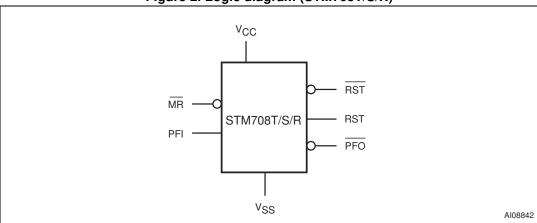

Figure 2. Logic diagram (STM708T/S/R)

Table 2. Signal names

| Symbol             | Name                     |

|--------------------|--------------------------|

| MR                 | Push-button reset input  |

| WDI                | Watchdog input           |

| WDO                | Watchdog output          |

| RST                | Active low reset output  |

| RST <sup>(1)</sup> | Active high reset output |

| V <sub>CC</sub>    | Supply voltage           |

| PFI                | Power-fail input         |

| PFO                | Power-fail output        |

| V <sub>SS</sub>    | Ground                   |

| NC                 | No connect               |

1. For STM706P and STM708T/S/R only.

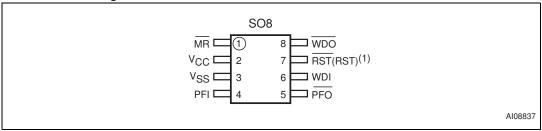

Figure 3. STM706T/S/R and STM706P SO8 connections

1. For STM706P reset output is active high.

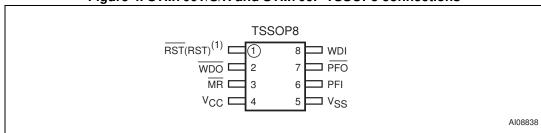

Figure 4. STM706T/S/R and STM706P TSSOP8 connections

1. For STM706P reset output is active high.

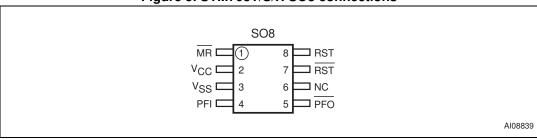

Figure 5. STM708T/S/R SO8 connections

577

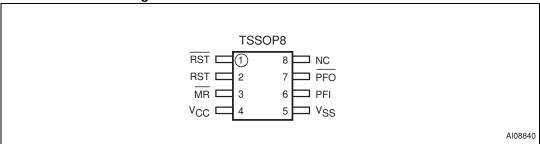

Figure 6. STM708T/S/R TSSOP8 connections

# 2 Pin descriptions

### 2.1 MR

A logic low on MR asserts the reset output. Reset remains asserted as long as MR is low and for  $t_{rec}$  after MR returns high. This active low input has an internal pull-up. It can be driven from a TTL or CMOS logic line, or shorted to ground with a switch. Leave open if unused.

#### 2.2 WDI

If WDI remains high or low for 1.6 s, the internal watchdog timer runs out and reset (or WDO) is triggered. The internal watchdog timer clears while reset is asserted or when WDI sees a rising or falling edge.

The watchdog function can be disabled by allowing the WDI pin to float. This feature is available for the "D" version only (see *Section 8: Part numbering*).

#### 2.3 WDO

WDO goes low when a transition does not occur on WDI within 1.6 s, and remains low until a transition occurs on WDI (indicating the watchdog interrupt has been serviced) or  $\overline{\text{MR}}$  input is asserted (goes low).  $\overline{\text{WDO}}$  also goes low when  $V_{CC}$  falls below the reset threshold; however, unlike the reset output,  $\overline{\text{WDO}}$  goes high as soon as  $V_{CC}$  exceeds the reset threshold. Output type is push-pull.

Note:

For those devices with a WDO output, a watchdog timeout will not trigger reset unless WDO is connected to MR.

### 2.4 RST

Pulses low for  $t_{rec}$  when triggered, and stays low whenever  $V_{CC}$  is below the reset threshold or when MR is a logic low. It remains  $lo\underline{w}$  for  $t_{rec}$  after either  $V_{CC}$  rises above the reset threshold, the watchdog triggers a reset, or MR goes from low to high.

#### 2.5 RST

Pulses high for  $t_{rec}$  when triggered, and stays high whenever  $V_{CC}$  is above the reset threshold or when  $\overline{MR}$  is a logic high. It remains high for  $t_{rec}$  after either  $V_{CC}$  falls below the reset threshold, the watchdog triggers a reset, or  $\overline{MR}$  goes from high to low.

#### 2.6 PFI

When PFI is less than  $V_{PFI}$ ,  $\overline{PFO}$  goes low; otherwise,  $\overline{PFO}$  remains high. Connect to ground if unused.

#### 2.7 PFO

When PFI is less than  $V_{PFI}$ ,  $\overline{PFO}$  goes low; otherwise,  $\overline{PFO}$  remains <u>high</u>. Output type is push-pull.  $\overline{PFO}$  pin is not supposed to be forced low by a processor.  $\overline{MR}$  input is gated off during the period  $\overline{PFO}$  is forced low. Leave open if unused.

Pin STM706P STM706T/S/R STM708T/S/R Name **Function SO8** TSSOP8 **SO8** TSSOP8 **SO8** TSSOP8 MR 1 3 1 3 1 3 Push-button reset input 6 8 WDI 6 8 Watchdog input WDO 2 8 2 8 Watchdog output (push-pull) 7 1 7 **RST** 1 Active low reset output 7 1 8 2 **RST** Active high reset output 2 4 2 4 2 4  $V_{CC}$ Supply voltage 4 6 4 6 4 6 PFI Power-fail input **PFO** 5 7 5 7 5 7 Power-fail output (push-pull) 3 5 3 5 3 5 Ground  $V_{SS}$ 6 8 NC No connect

Table 3. Pin description

1. For STM706P only

V<sub>CC</sub>

V<sub>RST</sub>

COMPARE

V<sub>CC</sub>

V<sub>RST</sub>

RST

V<sub>CC</sub>

FFO

AI08830

Figure 8. Block diagram (STM708T/S/R)

- 1. For STM706T/S/R and STM706P devices

- 2. For STM706P and STM708T/S/R devices

5/

## 3 Operation

### 3.1 Reset output

The STM70x supervisor asserts a reset signal to the  $\underline{MCU}$  whenever  $V_{CC}$  goes below the reset threshold ( $V_{RST}$ ), a watchdog timeout occurs (if WDO is connected to MR), or when the push-button reset input (MR) is taken low. RST is guaranteed to be a logic low (logic high for STM706P and STM708T/S/R) for  $V_{CC} < V_{RST}$  down to  $V_{CC} = 1$  V for  $T_A = 0$  °C to 85 °C.

During power-up, once  $V_{CC}$  exceeds the reset threshold an internal timer keeps  $\overline{RST}$  low for the reset timeout period,  $t_{rec}$ . After this interval  $\overline{RST}$  returns high.

If  $V_{CC}$  drops below the reset threshold, RST goes low. Each time RST is asserted, it stays low for at least the reset timeout period ( $t_{rec}$ ). Any time  $V_{CC}$  goes below the reset threshold the internal timer clears. The reset timer starts when  $V_{CC}$  returns above the reset threshold.

### 3.2 Push-button reset input

A logic low on  $\overline{MR}$  asserts reset. Reset remains asserted while  $\overline{MR}$  is low, and for  $t_{rec}$  (see Figure 27) after it returns high. The  $\overline{MR}$  input has an internal 40 k $\Omega$  pull-up resistor, allowing it to be left open if not used. This input can be driven with TTL/CMOS-logic levels or with open-drain / collector outputs. Connect a normally open momentary switch from  $\overline{MR}$  to GND to create a manual reset function; external debounce circuitry is not required. If  $\overline{MR}$  is driven from long cables or the device is used in a noisy environment, connect a 0.1  $\mu$ F capacitor from  $\overline{MR}$  to GND to provide additional noise immunity.  $\overline{MR}$  may float, or be tied to  $V_{CC}$  when not used.

### 3.3 Watchdog input (STM706T/S/R and STM706P)

The watchdog timer can be used to detect an out-of-control MCU. If the MCU does not toggle the watchdog input (WDI) within t<sub>WD</sub> (1.6 s), the watchdog output pin (WDO) is asserted. The internal 1.6s timer is cleared by either:

- 1. a reset pulse, or

- by toggling WDI (high-to-low or low-to-high), which can detect pulses as short as 50 ns.

See Figure 28 for STM706T/S/R and STM706P.

The timer remains cleared and does not count for as long as reset is asserted. As soon as reset is released, the timer starts counting.

Note:

The watchdog function may be disabled by floating WDI or tri-stating the driver connected to WDI. When tri-stated or disconnected, the maximum allowable leakage current is 10  $\mu$ A and the maximum allowable load capacitance is 200 pF.

## 3.4 Watchdog output (STM706T/S/R and STM706P)

When  $V_{CC}$  drops below the reset threshold,  $\overline{WDO}$  will go low even if the watchdog timer has not yet timed out. However, unlike the reset output,  $\overline{WDO}$  goes high as soon as  $V_{CC}$

exceeds the reset threshold. WDO may be used to generate a reset pulse by connecting it to the  $\overline{\text{MR}}$  input.

#### 3.5 Power-fail input/output

The power-fail input (PFI) is compared to an internal reference voltage (independent from the  $V_{RST}$  comparator). If PFI is less than the power-fail threshold ( $V_{PFI}$ ), the power-fail output (PFO) will go low. This function is intended for use as an undervoltage detector to signal a failing power supply. Typically PFI is connected through an external voltage divider (see *Figure 9*) to either the unregulated DC input (if it is available) or the regulated output of the  $V_{CC}$  regulator. The voltage divider can be set up such that the voltage at PFI falls below  $V_{PFI}$  several milliseconds before the regulated  $V_{CC}$  input to the STM70x or the microprocessor drops below the minimum operating voltage.

If the comparator is unused,  $\overline{PFI}$  should be connected to  $\overline{V_{SS}}$  and  $\overline{PFO}$  left unconnected.  $\overline{PFO}$  may be connected to  $\overline{MR}$  on the STM70x so that a low voltage on PFI will generate a reset output.

# 3.6 Ensuring a valid reset output down to $V_{CC} = 0 \text{ V}$

When  $V_{CC}$  falls below 1 V, the state of the  $\overline{RST}$  output can no longer be guaranteed, and becomes essentially an open circuit. If a high value pulldown resistor is added to the  $\overline{RST}$  pin, the output will be held low during this condition. A resistor value of approximately 100 k $\Omega$  will be large enough to not load the output under operating conditions, but still sufficient to pull  $\overline{RST}$  to ground during this low voltage condition (see *Figure 10*).

Figure 10. Reset output valid to ground circuit

### 3.7 Interfacing to microprocessors with bi-directional reset pins

Microprocessors with bi-directional reset pins can contend with the STM70x reset output. For example, if the reset output is driven high and the micro wants to pull it low, signal contention will result. To prevent this from occurring, connect a  $4.7k\Omega$  resistor between the reset output and the micro's reset I/O as in *Figure 11*.

Buffered reset to other system components

VCC

STM70x

RST

GND

GND

GND

Al08845

Figure 11. Interfacing to microprocessors with bi-directional reset I/O

#### **Typical operating characteristics** 4

Typical values are at  $T_A = 25$  °C.

Figure 12. Supply current vs. temperature (no load)

Figure 13. V<sub>PFI</sub> threshold vs. temperature

Figure 14. Reset comparator propagation delay vs. temperature

1.004 1.002 Normalized reset threshold 1.000 0.998 0.996 0 20 60 80 100 -40 -20 40 120 Temperature (°C) AI09145b

Figure 16. Normalized reset threshold vs. temperature

Figure 18. PFI to PFO propagation delay vs. temperature

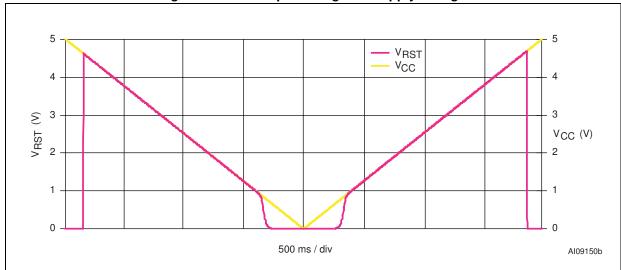

5 V<sub>RST</sub> VCC 3 3 VRST (V)  $V_{CC}(V)$ 2 1 500 ms / div Al09149b

Figure 20. RST output voltage vs. supply voltage

Figure 22. Power-fail comparator response time (assertion)

Figure 24. Maximum transient duration vs. reset threshold overdrive

57

# 5 Maximum ratings

Stressing the device above the rating listed in the *Table 4: Absolute maximum ratings* may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those indicated in *Table 5: Operating and AC measurement conditions* of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Table 4. Absolute maximum ratings

| Symbol                          | Parameter                                 | Value                        | Unit |

|---------------------------------|-------------------------------------------|------------------------------|------|

| T <sub>STG</sub>                | Storage temperature (V <sub>CC</sub> off) | -55 to 150                   | °C   |

| T <sub>SLD</sub> <sup>(1)</sup> | Lead solder temperature for 10 seconds    | 260                          | °C   |

| V <sub>IO</sub> <sup>(2)</sup>  | Input or output voltage                   | -0.3 to V <sub>CC</sub> +0.3 | V    |

| V <sub>CC</sub>                 | Supply voltage                            | -0.3 to 7.0                  | V    |

| I <sub>O</sub>                  | Output current                            | 20                           | mA   |

| P <sub>D</sub>                  | Power dissipation                         | 320                          | mW   |

<sup>1.</sup> Reflow at peak temperature of 260 °C. The time above 255 °C must not exceed 30 seconds.

<sup>2.</sup> Negative undershoot of -1.5 V for up to 10 ns or positive overshoot of  $V_{CC}$  + 1.5 V for up to 10 ns is allowable on the WDI and  $\overline{MR}$  input pins.

# 6 DC and AC parameters

This section summarizes the operating measurement conditions, and the DC and AC characteristics of the device. The parameters in *Table 6: DC and AC characteristics* are derived from tests performed under the measurement conditions summarized in *Table 5: Operating and AC measurement conditions*. Designers should check that the operating conditions in their circuit match the operating conditions when relying on the quoted parameters.

**Parameter** STM70x Unit ٧ V<sub>CC</sub> supply voltage 1.0 to 5.5 °C Ambient operating temperature (T<sub>A</sub>) -40 to 85 ≤ 5 Input rise and fall times ns 0.2 to 0.8  $\ensuremath{V_{CC}}$ ٧ Input pulse voltages Input and output timing ref. voltages 0.3 to 0.7 V<sub>CC</sub> ٧

Table 5. Operating and AC measurement conditions

Figure 26. Power-fail comparator waveform

57

Figure 27. MR timing waveform

1. RST for STM706P and STM708T/S/R.

Figure 28. Watchdog timing (STM706T/S/R and STM706P)

Table 6. DC and AC characteristics

| Symbol           | Description                                                                      | Test condition <sup>(1)</sup>                                                            | Min.                | Тур. | Max.                | Unit |

|------------------|----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|---------------------|------|---------------------|------|

| V <sub>CC</sub>  | Operating voltage                                                                |                                                                                          | 1.2 <sup>(2)</sup>  |      | 5.5                 | ٧    |

| -                | V aupply aurrent                                                                 | V <sub>CC</sub> < 3.6 V                                                                  |                     | 35   | 50                  | μΑ   |

| I <sub>CC</sub>  | V <sub>CC</sub> supply current                                                   | V <sub>CC</sub> < 5.5 V                                                                  |                     | 40   | 60                  | μΑ   |

|                  | Input leakage current (WDI)                                                      | 0 V < V <sub>IN</sub> < V <sub>CC</sub>                                                  | -1                  |      | +1                  | μΑ   |

| I <sub>LI</sub>  | Input leakage current<br>(WDI) with watchdog<br>disable feature ("D"<br>version) | 0 V < V <sub>IN</sub> < V <sub>CC</sub>                                                  | -110                |      | 110                 | μΑ   |

|                  | Input leakage current (PFI)                                                      | 0 V < V <sub>IN</sub> < V <sub>CC</sub>                                                  | -25                 | 2    | +25                 | nA   |

|                  | Input leakage current                                                            | V <sub>RST</sub> (max.) < V <sub>CC</sub> < 3.6 V                                        | 25                  | 80   | 250                 | μΑ   |

|                  | (MR)                                                                             | 4.5 V < V <sub>CC</sub> < 5.5 V                                                          | 75                  | 125  | 300                 | μΑ   |

| \ <u>/</u>       | Input high voltage (MR)                                                          | 4.5 V < V <sub>CC</sub> < 5.5 V                                                          | 2.0                 |      |                     | V    |

| $V_{IH}$         | input night voltage (Mh)                                                         | V <sub>RST</sub> (max.) < V <sub>CC</sub> < 3.6 V                                        | 0.7 V <sub>CC</sub> |      |                     | ٧    |

| V <sub>IH</sub>  | Input high voltage (WDI)                                                         | V <sub>RST</sub> (max.) < V <sub>CC</sub> < 5.5 V                                        | 0.7 V <sub>CC</sub> |      |                     | V    |

| V <sub>IL</sub>  | Input low voltage ( $\overline{MR}$ )                                            | 4.5 V < V <sub>CC</sub> < 5.5 V                                                          |                     |      | 8.0                 | V    |

| VIL.             | imput low voltage (witt)                                                         | V <sub>RST</sub> (max.) < V <sub>CC</sub> < 3.6 V                                        |                     |      | 0.6                 | V    |

| $V_{IL}$         | Input low voltage (WDI)                                                          | V <sub>RST</sub> (max.) < V <sub>CC</sub> < 5.5 V                                        |                     |      | 0.3 V <sub>CC</sub> | V    |

| $V_{OL}$         | Output low voltage (PFO, RST, RST, WDO)                                          | $V_{CC} \ge V_{RST}$ (max.),<br>$I_{SINK} = 3.2 \text{ mA}$                              |                     |      | 0.3                 | V    |

| V                | Output low voltage (RST)                                                         | $I_{SINK} = 50 \mu A, V_{CC} = 1.0 V,$<br>$T_A = 0 ^{\circ}C \text{ to } 85 ^{\circ}C$   |                     |      | 0.3                 | ٧    |

| V <sub>OL</sub>  | Output low voitage (no1)                                                         | $I_{SINK} = 100 \mu A,$<br>$V_{CC} = 1.2 \text{ V}$                                      |                     |      | 0.3                 | V    |

| V <sub>OH</sub>  | Output high voltage (RST, RST, WDO)                                              | I <sub>SOURCE</sub> = 1 mA,<br>V <sub>CC</sub> = V <sub>RST</sub> (max.)                 | 2.4                 |      |                     | ٧    |

|                  | Output high voltage (PFO)                                                        | $I_{SOURCE}$ = 75 $\mu$ A,<br>$V_{CC} \ge V_{RST}$ (max.)                                | 0.8 V <sub>CC</sub> |      |                     | ٧    |

| Power-fai        | l comparator                                                                     |                                                                                          | •                   | •    | •                   |      |

| V <sub>PFI</sub> | PFI input threshold                                                              | PFI falling (STM70xP/R, $V_{CC} = 3.0 \text{ V}$ ; STM70xS/T, $V_{CC} = 3.3 \text{ V}$ ) | 1.20                | 1.25 | 1.30                | V    |

| t <sub>PFD</sub> | PFI to PFO propagation delay                                                     |                                                                                          |                     | 2    |                     | μs   |

|                  | i .                                                                              | 1                                                                                        |                     | •    |                     |      |

Table 6. DC and AC characteristics (continued)

| Symbol                 | Description                      | Test condition <sup>(1)</sup>                     | Min. | Тур. | Max. | Unit |  |

|------------------------|----------------------------------|---------------------------------------------------|------|------|------|------|--|

| Reset thr              | esholds                          |                                                   |      |      |      |      |  |

|                        |                                  | STM706P/70xR                                      | 2.55 | 2.63 | 2.70 | V    |  |

| V <sub>RST</sub>       | Reset threshold <sup>(3)</sup>   | STM70xS                                           |      | 2.93 | 3.00 | V    |  |

|                        |                                  | STM70xT                                           | 3.00 | 3.08 | 3.15 | V    |  |

|                        | Reset threshold hysteresis       |                                                   |      | 20   |      | mV   |  |

| +                      | DCT pulse width                  | Blank (see <i>Table 9</i> )                       | 140  | 200  | 280  | - ms |  |

| t <sub>rec</sub>       | RST pulse width                  | A <sup>(4)</sup> (see <i>Table 9</i> )            | 160  | 200  | 280  |      |  |

| Push-but               | ton reset input                  |                                                   |      |      |      |      |  |

| t <sub>MLMH</sub>      | MD pulso width                   | V <sub>RST</sub> (max.) < V <sub>CC</sub> < 3.6 V | 500  |      |      | ns   |  |

| (or t <sub>MR</sub> )  | MR pulse width                   | 4.5 V < V <sub>CC</sub> < 5.5 V                   | 150  |      |      | ns   |  |

| t <sub>MLRL</sub>      | MR to RST output delay           | V <sub>RST</sub> (max.) < V <sub>CC</sub> < 3.6 V |      |      | 750  | ns   |  |

| (or t <sub>MRD</sub> ) | TWIN to NOT output delay         | 4.5 V < V <sub>CC</sub> < 5.5 V                   |      |      | 250  | ns   |  |

| Watchdo                | g timer (STM706T/S/R and STM706P | )                                                 |      |      |      |      |  |

| +                      | Watchdog timeout period          | STM706P/70xR,<br>V <sub>CC</sub> = 3.0 V          | 1.12 | 1.60 | 2.24 | S    |  |

| t <sub>WD</sub>        | wateridog timeout period         | STM70xS/70XT,<br>$V_{CC} = 3.3 \text{ V}$         |      |      |      |      |  |

|                        | WDI pulse width                  | 4.5 V < V <sub>CC</sub> < 5.5 V                   | 50   |      |      | ns   |  |

|                        | WDI puise wiutii                 | V <sub>RST</sub> (max.) < V <sub>CC</sub> < 3.6 V | 100  |      |      | ns   |  |

<sup>1.</sup> Valid for ambient operating temperature:  $T_A = -40$  to 85 °C;  $V_{CC} = V_{RST}$  (max.) to 5.5 V (except where noted).

<sup>2.</sup>  $V_{CC}$  (min) = 1.0 V for  $T_A$  = 0 °C to +85 °C.

<sup>3.</sup> For  $V_{CC}$  falling.

<sup>4.</sup> STM706P/STM70xR device,  $V_{CC}$  = 3 V; STM706xS/STM70xT device,  $V_{CC}$  = 3.3 V.

# 7 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions and product status are available at: <a href="https://www.st.com">www.st.com</a>. ECOPACK is an ST trademark.

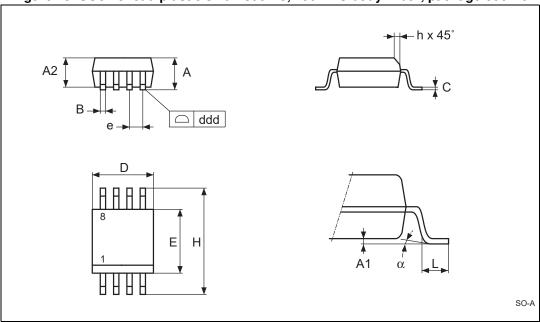

## 7.1 SO8 package information

Figure 29. SO8 - 8-lead plastic small outline, 150 mils body width, package outline

Note: Drawing is not to scale.

Table 7. SO8 - 8-lead plastic small outline, 150 mils body width, mechanical data

|        | Dimensions |      |      |       |        |       |

|--------|------------|------|------|-------|--------|-------|

| Symbol |            | mm   |      |       | inches |       |

|        | Тур.       | Min. | Max. | Тур.  | Min.   | Max.  |

| Α      | _          | 1.35 | 1.75 | _     | 0.053  | 0.069 |

| A1     | _          | 0.10 | 0.25 | _     | 0.004  | 0.010 |

| В      | _          | 0.33 | 0.51 | _     | 0.013  | 0.020 |

| С      | _          | 0.19 | 0.25 | _     | 0.007  | 0.010 |

| D      | _          | 4.80 | 5.00 | _     | 0.189  | 0.197 |

| ddd    | _          | _    | 0.10 | _     | _      | 0.004 |

| Е      | _          | 3.80 | 4.00 | _     | 0.150  | 0.157 |

| е      | 1.27       | _    | _    | 0.050 | _      | _     |

| Н      | _          | 5.80 | 6.20 | _     | 0.228  | 0.244 |

| h      | _          | 0.25 | 0.50 | _     | 0.010  | 0.020 |

| L      | _          | 0.40 | 0.90 | _     | 0.016  | 0.035 |

| а      | _          | 0°   | 8°   | _     | 0°     | 8°    |

| N      | 8          | 8    |      |       |        |       |

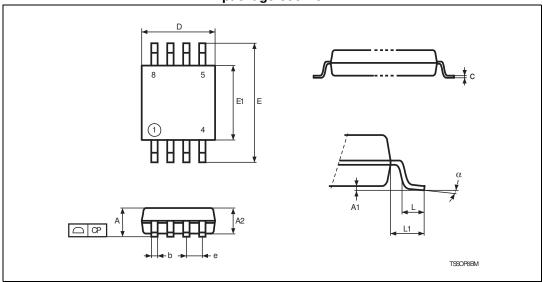

## 7.2 TSSOP8 3x3 (DS) package information

Figure 30. TSSOP8 - 8-lead, thin shrink small outline, 3 x 3 mm body size, package outline

Note: Drawing is not to scale.

Table 8. TSSOP8 - 8-lead, thin shrink small outline, 3 x 3 mm body size, mechanical data

|        |      |      | Dimens | sions |        |       |

|--------|------|------|--------|-------|--------|-------|

| Symbol |      | mm   |        |       | inches |       |

|        | Тур. | Min. | Max.   | Тур.  | Min.   | Max.  |

| Α      | _    | _    | 1.10   | _     | _      | 0.043 |

| A1     | _    | 0.05 | 0.15   | _     | 0.002  | 0.006 |

| A2     | 0.85 | 0.75 | 0.95   | 0.034 | 0.030  | 0.037 |

| b      | _    | 0.25 | 0.40   | _     | 0.010  | 0.016 |

| С      | _    | 0.13 | 0.23   | _     | 0.005  | 0.009 |

| CP     | _    | _    | 0.10   | _     | _      | 0.004 |

| D      | 3.00 | 2.90 | 3.10   | 0.118 | 0.114  | 0.122 |

| е      | 0.65 | _    | _      | 0.026 | _      | _     |

| E      | 4.90 | 4.65 | 5.15   | 0.193 | 0.183  | 0.203 |

| E1     | 3.00 | 2.90 | 3.10   | 0.118 | 0.114  | 0.122 |

| L      | 0.55 | 0.40 | 0.70   | 0.022 | 0.016  | 0.030 |

| L1     | 0.95 | _    | _      | 0.037 | _      | _     |

| а      | _    | 0°   | 6°     | _     | 0°     | 6°    |

| N      | 8    | 8    |        |       |        |       |

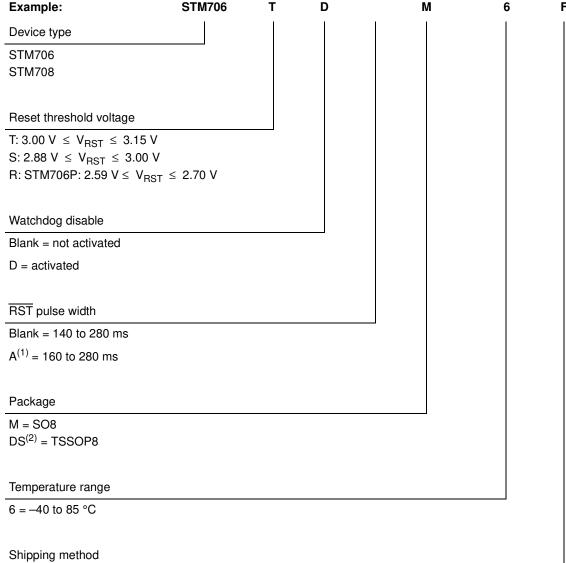

# 8 Part numbering

Table 9. Ordering information scheme STM706 T D M

F = ECOPACK® packages, tape and reel

- 1. Available in SO8 (M) package only

- 2. Contact local ST sales office for availability

For other options, or for more information on any aspect of this device, please contact the ST sales office nearest you.

Table 10. Marking description

| Part number | Reset threshold | Package | Topside marking |

|-------------|-----------------|---------|-----------------|

| STM706P     | 2.63 V          | SO8     | 706P            |

| STW/OOF     | 2.03 V          | TSSOP8  | 700F            |

| STM706T     | 3.08 V          | SO8     | 706T            |

| 311117001   | 3.06 V          | TSSOP8  | 7061            |

| STM706S     | 2.93 V          | SO8     | 706S            |

| 31111/003   | 2.93 V          | TSSOP8  | 7063            |

| STM706R     | 2.63 V          | SO8     | 706R            |

| STW/UOR     | 2.03 V          | TSSOP8  | 706H            |

| STM706RD    | 2.63 V          | SO8     | 706RD           |

| STWITOORD   | 2.03 V          | TSSOP8  | 700ND           |

| STM708T     | 3.08 V          | SO8     | 708T            |

| 31111/001   | 3.06 V          | TSSOP8  | 7081            |

| STM708S     | 2747000         |         | 708S            |

| 311017003   | 2.93 V          | TSSOP8  | 7003            |

| STM708R     | 2.63 V          | SO8     | 708R            |

| GTWI70011   | 2.00 V          | TSSOP8  | 70011           |

# 9 Revision history

Table 11. Document revision history

| Date        | Revision | Changes                                                                                                                                                                                                                                   |

|-------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Oct-2003    | 1        | Initial release.                                                                                                                                                                                                                          |

| 12-Dec-2003 | 2        | Reformatted; update characteristics (Figure 2, 3, 8 to 10, 27 to 29; Table 6 to 9).                                                                                                                                                       |

| 16-Jan-2004 | 2.1      | Add Typical operating characteristics (Figure 13, to 19, 21, to 25).                                                                                                                                                                      |

| 09-Apr-2004 | 3        | Reformatted; update characteristics (Figure 15, 19, 21, 22, 25; Table 8).                                                                                                                                                                 |

| 25-May-2004 | 4        | Update characteristics (Table 3, Table 6).                                                                                                                                                                                                |

| 02-Jul-2004 | 5        | Datasheet promoted; waveform corrected (Table 27).                                                                                                                                                                                        |

| 21-Sep-2004 | 6        | Clarify root part numbers; (Figure 2, to 10, 29; Table 1, 3, 6, 9).                                                                                                                                                                       |

| 25-Feb-2005 | 7        | Update typical characteristics (Figure 13 to 25).                                                                                                                                                                                         |

| 02-Nov-2009 | 8        | Updated Table 1, Table 3, Table 4, Table 6, Table 9, Section 2.3, Section 2.7, text in Section 7; reformatted document.                                                                                                                   |

| 30-Apr-2010 | 9        | Updated Table 4, corrected typo in Table 2, Section 2.3, Section 3, Section 5 and Section 6, Figure 17, Table 7 and Table 8.                                                                                                              |

| 06-Aug-2010 | 10       | Updated Features, Section 4: Typical operating characteristics; Table 9.                                                                                                                                                                  |

| 06-Sep-2011 | 11       | Updated Section 2.7, Section 5 and Disclaimer, minor typo modifications throughout the document.                                                                                                                                          |

| 21-Aug-2012 | 12       | Added <i>Applications</i> , updated <i>Section 2.2</i> and <i>Section 2.3</i> , added note to <i>Section 3.3</i> , added cross-references in <i>Section 5</i> and <i>Section 6</i> , minor text corrections throughout document.          |

| 15-Dec-2015 | 13       | Updated layout of cover page and Section 7: Package information. Added information about the watchdog disable function to Section 2.2: WDI, Table 6, Table 9, and Table 10. Table 9: removed the "E" option (tubes) from shipping method. |

| 17-Jan-2024 | 14       | Updated V <sub>OL</sub> and V <sub>OH</sub> test condition in <i>Table 6</i> .                                                                                                                                                            |

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

32/32

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, please refer to <a href="www.st.com/trademarks">www.st.com/trademarks</a>. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2024 STMicroelectronics - All rights reserved