V54/7482 010002

2-BIT FULL ADDER

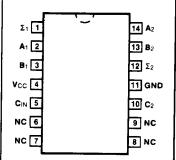

CONNECTION DIAGRAM

PINOUT A

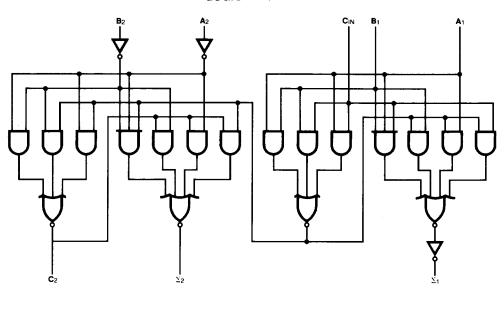

**DESCRIPTION** — The '82 is a full adder which performs the addition of two 2-bit binary numbers. The sum  $(\Sigma)$  outputs are provided for each bit and the resultant carry  $(C_2)$  is obtained from the second bit. Designed for medium to high speed, multiple-bit, parallel-add/serial-carry applications, the circuit utilizes high speed, high fan-out TTL. The implementation of a single-inversion, high speed, Darlington-connected serial-carry circuit within each bit minimizes the necessity for extensive "lookahead" and carry-cascading circuits.

## **ORDERING CODE:** See Section 9

|                    | PIN | COMMERCIAL GRADE                                                                                                                                                                  | MILITARY GRADE | PKG |  |

|--------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----|--|

| PKGS               | ОПТ | $V_{CC} = +5.0 \text{ V} \pm 5\%,$ $V_{CC} = +5.0 \text{ V} \pm 10\%,$ $T_{A} = 0^{\circ}\text{C to } +70^{\circ}\text{C}$ $T_{A} = -55^{\circ}\text{C to } +125^{\circ}\text{C}$ |                |     |  |

| Plastic<br>DIP (P) | A   | 7482PC                                                                                                                                                                            |                | 9A  |  |

| Ceramic<br>DIP (D) | А   | 7482DC                                                                                                                                                                            | 5482DM         | 6A  |  |

| Flatpak<br>(F)     | А   | 7482FC                                                                                                                                                                            | 5482FM         | 31  |  |

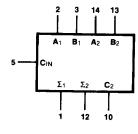

#### LOGIC SYMBOL

V<sub>CC</sub> = Pin 14 GND = Pin 11 NC = Pins 6,7,8,9

## INPUT LOADING/FAN-OUT: See Section 3 for U.L. definitions

| PIN NAMES      | DESCRIPTION          | 54/74 (U.L.)<br>HIGH/LOW<br>4.0/4.0 |  |

|----------------|----------------------|-------------------------------------|--|

| B <sub>1</sub> | Bit 1 Operand Inputs |                                     |  |

| 2, <b>B</b> 2  | Bit 2 Operand Inputs | 1.0/1.0                             |  |

| IN             | Bit 1 Carry Input    | 4.0/4.0                             |  |

| 1              | Bit 1 Sum Output     | 10/10                               |  |

| 2              | Bit 2 Sum Output     | 10/10                               |  |

| 2              | Bit 2 Carry Output   | 5,0/5.0                             |  |

#### **TRUTH TABLE**

| INPUTS           |                |                |                | OUTPUTS |                     |                |                                           |                     |                |  |

|------------------|----------------|----------------|----------------|---------|---------------------|----------------|-------------------------------------------|---------------------|----------------|--|

|                  |                |                |                |         | C <sub>IN</sub> = 0 |                |                                           | C <sub>IN</sub> = 1 |                |  |

| A <sub>1</sub>   | B <sub>1</sub> | A <sub>2</sub> | B <sub>2</sub> | Σ1      | Σ2                  | C <sub>2</sub> | Σ1                                        | Σ2                  | C <sub>2</sub> |  |

| LHLH             | L<br>H<br>H    | L<br>L<br>L    | L<br>L<br>L    | LHHL    | L<br>L<br>H         | L<br>L<br>L    | TLLI                                      | L<br>H<br>H         | L<br>L<br>L    |  |

| L<br>H<br>L<br>H | L<br>H<br>H    | H H H          |                | HHL     | H<br>H<br>L         | LLH            | HLLH                                      | H<br>L<br>L         | L<br>H<br>H    |  |

| L<br>H<br>L      | L<br>H<br>H    | L<br>L<br>L    | 1111           | LHHL    | HHL                 | LLH            | ILLI                                      | HLLL                | L<br>H<br>H    |  |

| L<br>H<br>L      | L<br>H<br>H    | HHHH           | <b>111</b>     | JIIJ    | L<br>L<br>H         | 1111           | $\mathtt{x} \sqcup \mathtt{l} \mathtt{x}$ | L<br>H<br>H         | IIII           |  |

H = HIGH Voltage Level L = LOW Voltage Level

## LOGIC DIAGRAM

# DC CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE (unless otherwise specified)

| SYMBOL | PARAMETER                 |     | 54/74 |     | UNITS      | CONDITIONS                                                        |

|--------|---------------------------|-----|-------|-----|------------|-------------------------------------------------------------------|

|        |                           | Min | Max   |     | CONDITIONS |                                                                   |

| los    | Output Short Circuit      | ХМ  | -20   | -55 | mA         | V <sub>CC</sub> = Max                                             |

|        | Current at Σ <sub>n</sub> | хс  | -18   | -55 | 11110      |                                                                   |

| los    | Output Short Circuit      | ХМ  | -20   | -70 | mA         | V <sub>CC</sub> = Max                                             |

|        | Current at C <sub>2</sub> | хс  | -18   | -70 | ""         |                                                                   |

| lcc    |                           | ХМ  |       | 50  | mA         | V <sub>CC</sub> = Max;                                            |

|        | Power Supply Current      | хс  |       | 58  |            | $A_1$ , $A_2$ , $C_{IN} = 4.5 \text{ V}$ ; $B_1$ , $B_2 = G_{IN}$ |

AC CHARACTERISTICS:  $V_{CC} = +5.0 \text{ V}$ ,  $T_A = +25^{\circ} \text{ C}$  (See Section 3 for waveforms and load configurations)

|              |                                                        | 54  | /74            |       | CONDITIONS                               |  |

|--------------|--------------------------------------------------------|-----|----------------|-------|------------------------------------------|--|

| SYMBOL       | PARAMETER                                              | 1   | 15 pF<br>400 Ω | UNITS |                                          |  |

|              |                                                        | Min | Max            | 1     |                                          |  |

| tPLH<br>tPHL | Propagation Delay<br>C <sub>IN</sub> to Σ <sub>1</sub> |     | 34<br>40       | ns    | Figs. 3-1, 3-20                          |  |

| tplH<br>tpHL | Propagation Delay $B_2$ to $\Sigma_2$                  |     | 40<br>35       | ns    | Figs. 3-1, 3-20                          |  |

| tpLH<br>tpHL | Propagation Delay<br>C <sub>IN</sub> to Σ <sub>2</sub> |     | 38<br>42       | ns    | Figs. 3-1, 3-20                          |  |

| tpLH<br>tpHL | Propagation Delay<br>C <sub>IN</sub> to C <sub>2</sub> |     | 19<br>27       | ns    | Figs. 3-1, 3-5<br>R <sub>L</sub> = 780 Ω |  |