**MAX40109**

# **General Description**

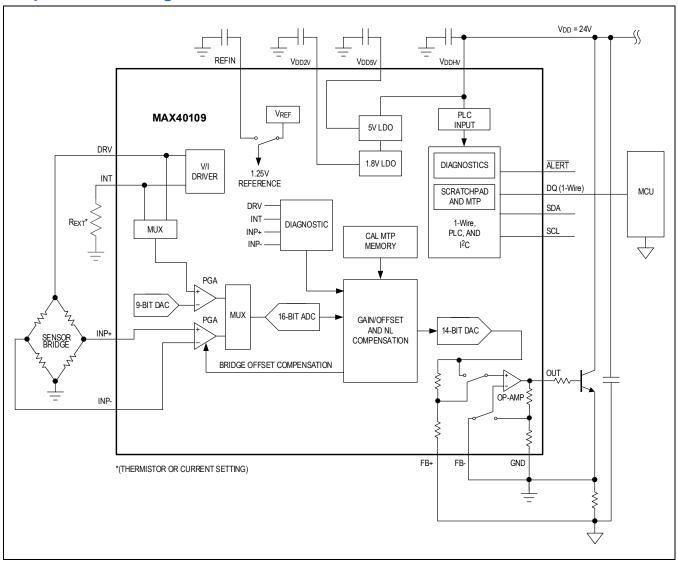

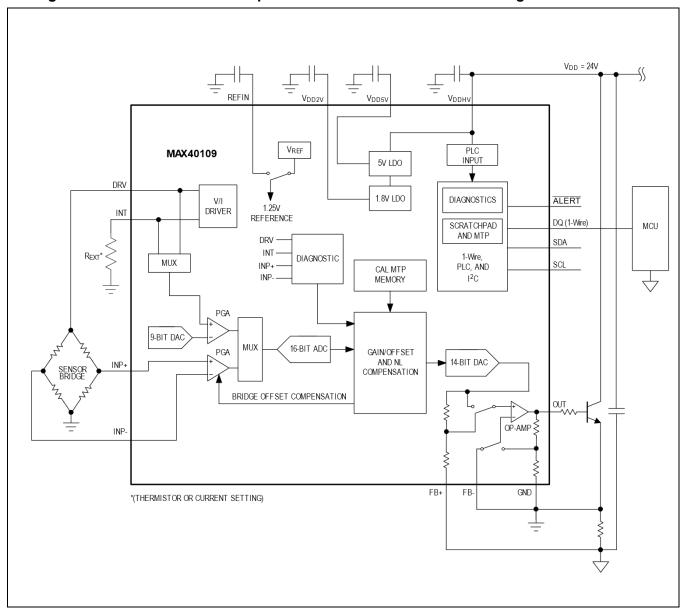

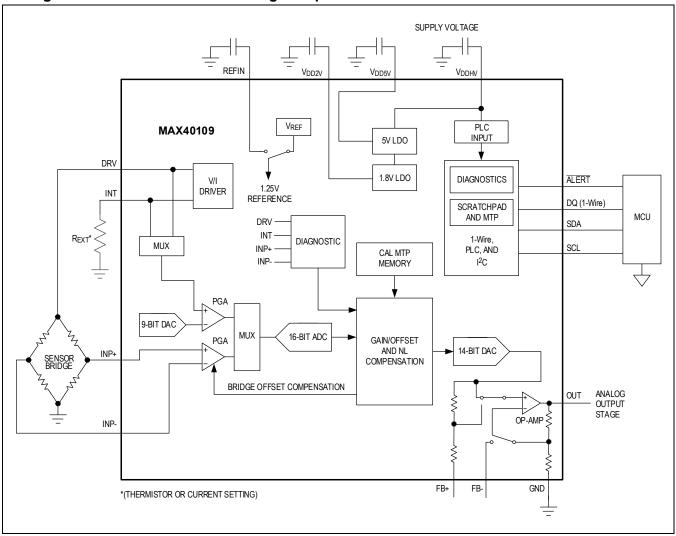

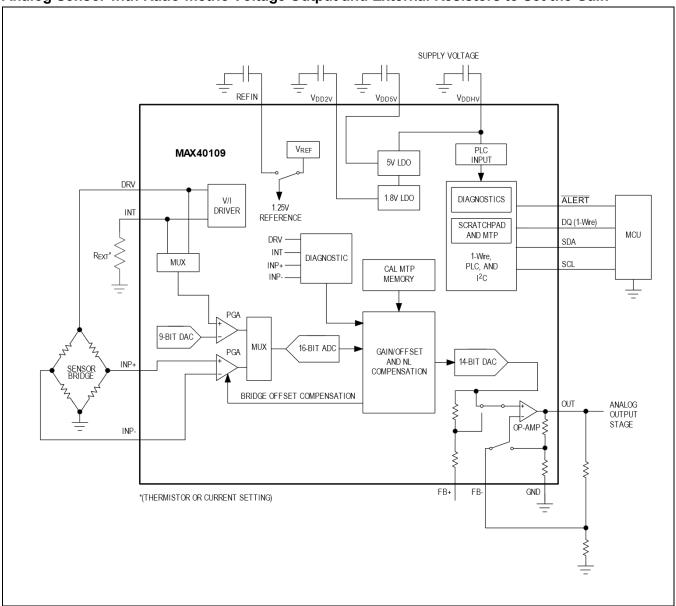

The MAX40109 is a low-power, precision sensor interface SoC that includes a high-precision, programmable Analog frontend (AFE), Analog-to-Digital Converter (ADC), calibration memory, and digital signal processing. It also includes a Digital-to-Analog Converter (DAC) with an output buffer to support analog voltage output and a 4mA–20mA current loop. It is designed for sensor applications such as strain gauges, pressure, force, and temperature.

This Sensor AFE has both analog and digital outputs. The digital 1-Wire/I<sup>2</sup>C interfaces program the calibration memory, the front-end Programmable gain amplifier (PGA)'s gain, and the internal current source that drives the sensors' bridge. The digital I<sup>2</sup>C interface can also be used to retrieve the digital output data and generate alarms.

The MAX40109 operates from 3V to 36V, is available in the Thin quad flat no-lead (TQFN) package and is specified over the -40°C to +125°C operating temperature range.

# **Applications**

- Pressure Sensors

- Strain Gauges

- Force Sensors

- Temperature Sensors

- Wheatstone-Bridge

#### **Benefits and Features**

- Analog Front-End to Interface with Resistive Bridge-Based Pressure Sensors

- Temperature Measurement either directly from the Resistive Bridge or from an External Thermistor

- Analog Zero-Pressure Offset Compensation

- High-Precision PGA Front-End with 20 Gain Options

- Analog and Digital Outputs

- Digital 1-Wire, Power Line Communication (PLC) and I<sup>2</sup>C interfaces

- Calibration Memory with Third-Order Polynomial for Compensation from Temperature and Non-Linearity

- Internal Electromagnetic Interference (EMI)

Rejection

- Supply Voltage Range: 3V to 36V

- Low 2mA (typ.) Supply Current

- · Available in TQFN package

Ordering Information appears at end of data sheet.

# **TABLE OF CONTENTS**

| General Description               | 1  |

|-----------------------------------|----|

| Applications                      | 1  |

| Benefits and Features             | 1  |

| Simplified Block Diagram          | 5  |

| Absolute Maximum Ratings          | 6  |

| Package Information               | 6  |

| Electrical Characteristics        | 7  |

| Typical Operating Characteristics | 13 |

| Pin Configurations                | 17 |

| Pin Descriptions                  | 17 |

| Detailed Description              | 18 |

| Register Function                 | 18 |

| Configuration Register            | 20 |

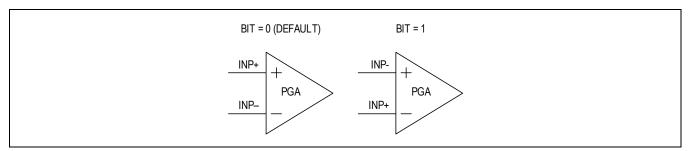

| PGA Input Mux                     | 20 |

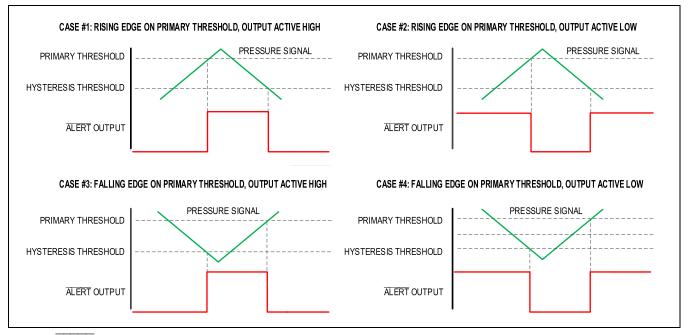

| ALERT Mode                        | 20 |

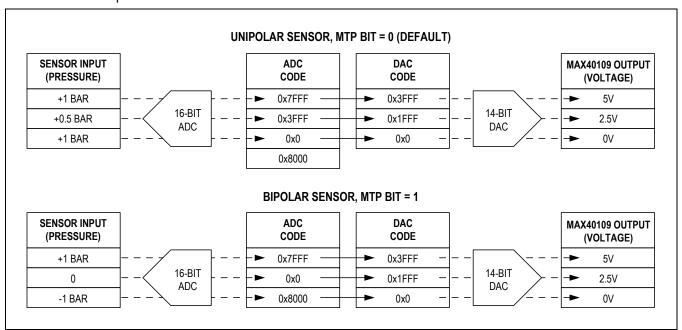

| Pressure Digital Output cases:    | 21 |

| Temp Current                      | 21 |

| Shutdown                          | 22 |

| Current Source Reference Resistor | 22 |

| Reference                         | 22 |

| Digital Filter                    | 22 |

| Pressure Cal Bypass               | 23 |

| Temp Cal Bypass                   | 23 |

| MTP_EN                            | 23 |

| Status Register                   | 23 |

| PGA Pressure Gain                 | 24 |

| Current Source                    | 24 |

| Uncalibrated Pressure             | 25 |

| Uncalibrated Temperature          | 25 |

| ADC Sample Rate                   | 25 |

| Interrupt Enable                  | 26 |

| Bridge Drive                      | 26 |

| PGA Temperature Gain              | 26 |

| Calibrated Pressure               | 27 |

| Calibrated Temperature            | 27 |

| Temp Mode                         | 27 |

| Sensor Offset Cal Config          | 28 |

| Analog Filter BW                  | 28 |

|-----------------------------------|----|

| Zero Pressure Offset RAM Override | 28 |

| Zero Pressure Offset Select.      | 28 |

| Analog Output Stage               | 29 |

| SLP_MR                            | 29 |

| SLP_MREF                          | 29 |

| CP_Control_1                      | 29 |

| CP_Control_2                      | 29 |

| MTP_Control                       | 29 |

| MTP_Status                        | 30 |

| MTP_PROT_ADDR                     | 30 |

| MTP_PROT_WDATA                    | 30 |

| MTP_PROT_RDATA                    | 30 |

| MTP_LEVEL                         | 30 |

| SLP_MRV                           | 30 |

| SLP_MREFV                         | 30 |

| MTP_DATA0                         | 30 |

| MTP_ADDR                          | 30 |

| MTP Memory and Functions          | 31 |

| Bridge Sensor Calibration         | 34 |

| Scratch Pad Memory                | 35 |

| Diagnostics                       | 35 |

| Pressure Thresholds on ALERT      | 36 |

| Zero Pressure Offset.             | 36 |

| Config Register                   | 37 |

| I <sup>2</sup> C Client Address   | 37 |

| Lock MTP                          | 37 |

| Zero-pressure Offset Enable       | 37 |

| Sensor Polarity                   | 38 |

| Output Clipping Enable            | 38 |

| Analog Diagnostic Enable          | 38 |

| Temperature Offset                | 38 |

| MTP Re-programmability            | 39 |

| Output Clipping Thresholds        | 39 |

| Analog Output Diagnostic Levels   | 39 |

| Initializing MTP                  | 40 |

| Burning to MTP                    | 40 |

| Digital Interface Management      | 40 |

| 1-vvire interrace                                                                     | 40 |

|---------------------------------------------------------------------------------------|----|

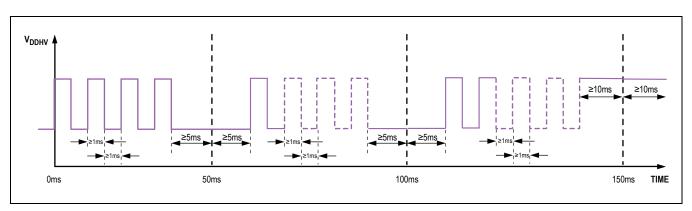

| Power Line Communication (PLC)                                                        | 40 |

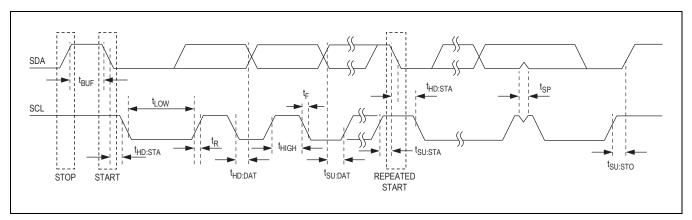

| I <sup>2</sup> C-Compatible Bus Interface                                             | 42 |

| 1-Wire Bus System                                                                     | 43 |

| 64-Bit ROM Code                                                                       | 44 |

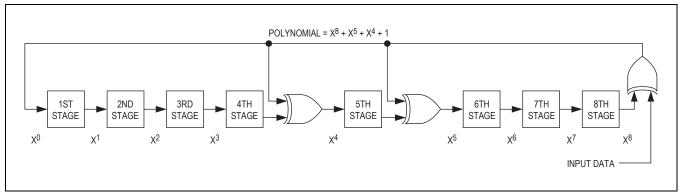

| CRC Generation                                                                        | 44 |

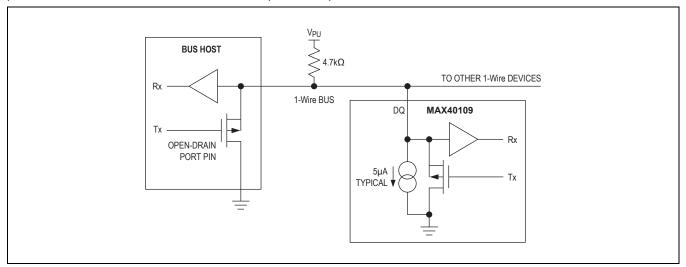

| Hardware Configuration                                                                | 45 |

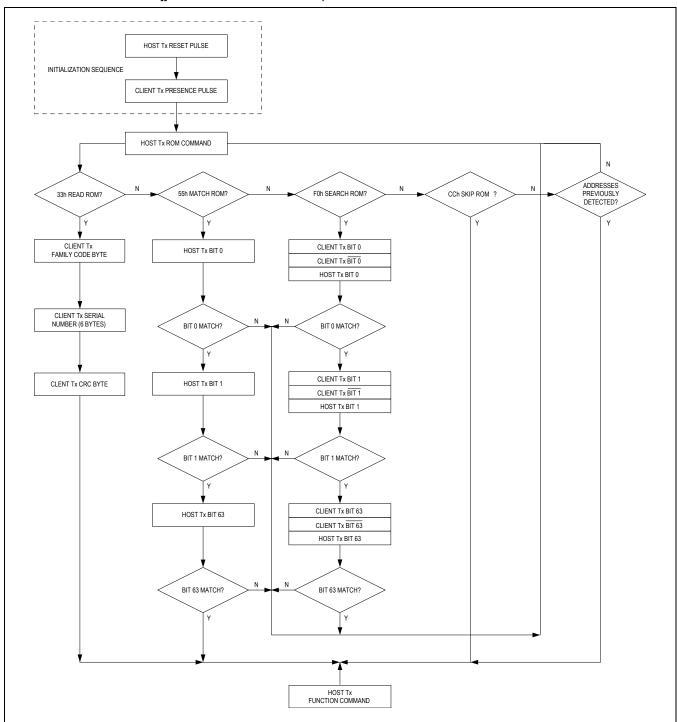

| Transaction Sequence                                                                  | 45 |

| Initialization                                                                        | 45 |

| ROM Commands                                                                          | 45 |

| Search ROM [F0h]                                                                      | 47 |

| Read ROM [33h]                                                                        | 47 |

| Match ROM [55h]                                                                       | 47 |

| Skip ROM[ CCh]                                                                        | 47 |

| Function Command                                                                      | 47 |

| Data Format                                                                           | 48 |

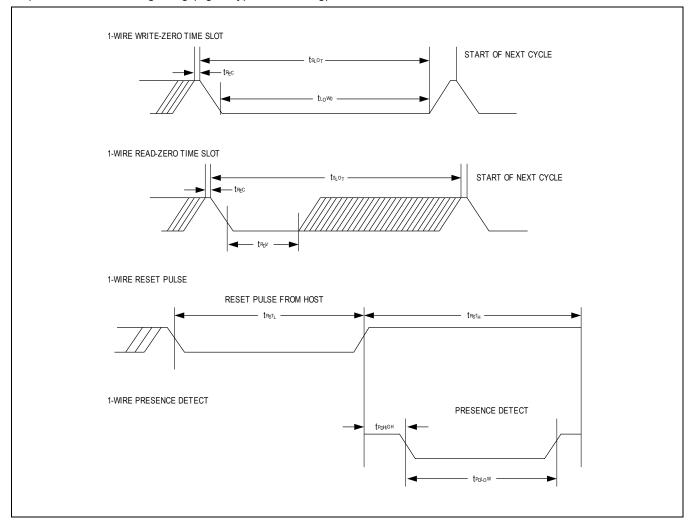

| 1-Wire Signaling                                                                      | 48 |

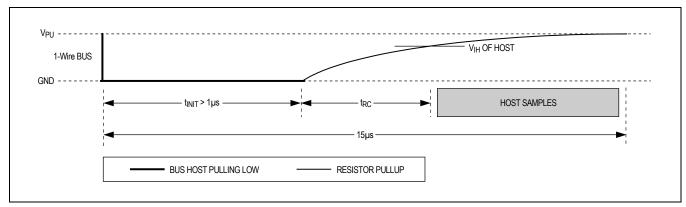

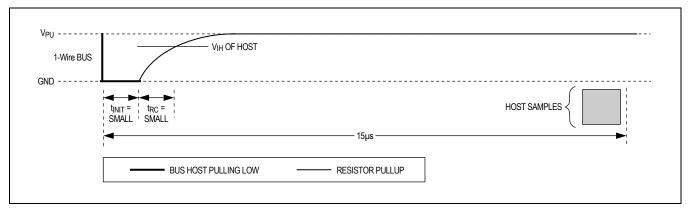

| Initialization Procedure: Reset and Presence Pulses                                   | 48 |

| Read/ Write Time Slots                                                                | 49 |

| Write Time Slots                                                                      | 49 |

| Read Time Slots                                                                       | 50 |

| Applications Information                                                              | 51 |

| Temperature Measurement                                                               | 51 |

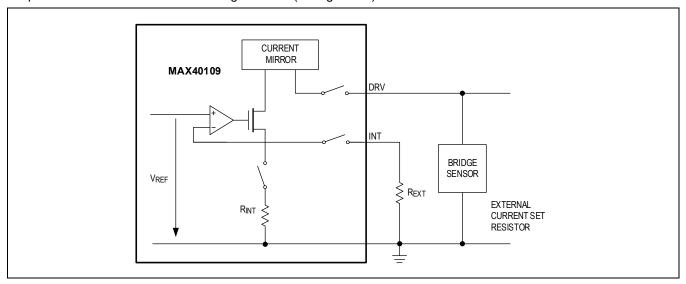

| Use External Resistor for Bridge Current Source                                       | 52 |

| Ratio-metric Voltage Output                                                           | 52 |

| Sensor Offset Calibration                                                             | 52 |

| Using the MAX40109 to Perform Sensor Calibration                                      | 53 |

| Analog Output Stage                                                                   | 53 |

| Layout Recommendations                                                                | 54 |

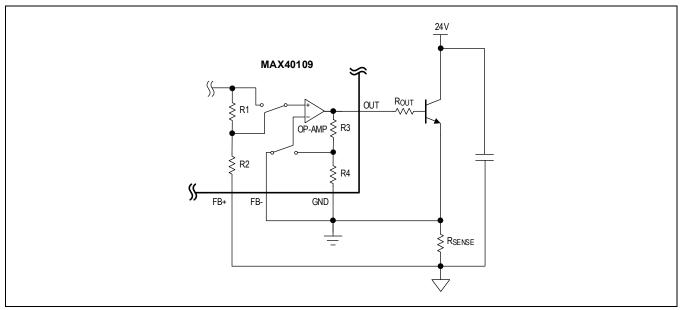

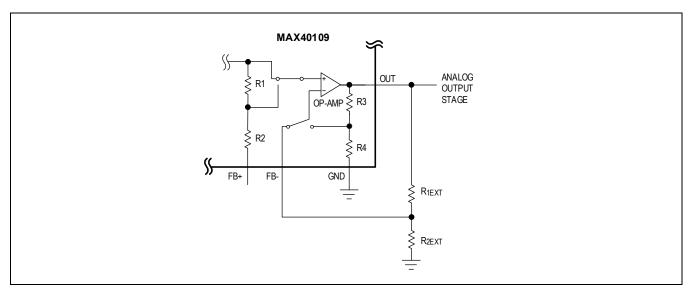

| Typical Application Circuits                                                          | 55 |

| Analog Sensor with Ratio-metric Voltage Output                                        | 56 |

| Analog Sensor with Ratio-metric Voltage Output and External Resistors to Set the Gain | 57 |

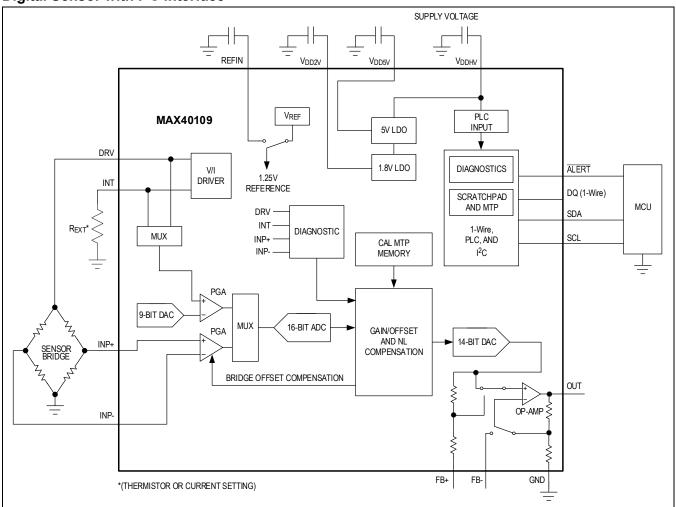

| Digital Sensor with I <sup>2</sup> C Interface                                        | 58 |

| Ordering Information                                                                  | 58 |

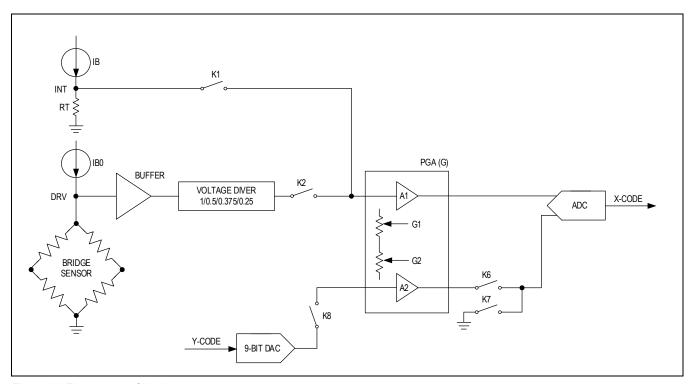

# **Simplified Block Diagram**

# **Absolute Maximum Ratings**

| V <sub>DDHV</sub> to GND40V to +40V                                                              |

|--------------------------------------------------------------------------------------------------|

| OUT to GND40V to +40V                                                                            |

| Pin Voltage Differential (Voltage between any of these two pins: $V_{DD}$ , OUT, GND)40V to +40V |

| V <sub>DD5V</sub> , DRV, FB-, INP+, INP-, INT, SCL, SDA, ALERT to GND0.3V to +6V                 |

| V <sub>DD2V</sub> , REFIN to GND0.3V to +2V                                                      |

| FB+ to GND1.5V to +5V                                                                            |

| DQ to GND                                                                                                                          | 1.5V to +6V          |

|------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| Continuous current into any input/output pin 10r<br>Power Dissipation TQFN (Single Layer Board)<br>derate 20.8 mW/°C above +70°C.) | $T_A = +70^{\circ}C$ |

| Continuous Power Dissipation TQFN (Four (Derate 30.3 mW/°C above +70°C.)                                                           | -Layer Board)        |

| Operating Temperature Range                                                                                                        | -40°C to 125°C       |

| Junction Temperature                                                                                                               | +150°C               |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# **Package Information**

| TQFN                                    |                |

|-----------------------------------------|----------------|

| Package Code                            | T2044-5C       |

| Outline Number                          | <u>21-0139</u> |

| Land Pattern Number                     | <u>90-0429</u> |

| Thermal Resistance, Single Layer Board: |                |

| Junction to Ambient ( $\theta_{JA}$ )   | 48             |

| Junction to Case $(\theta_{JC})$        | 2              |

| Thermal Resistance, Four Layer Board:   |                |

| Junction to Ambient (θ <sub>JA</sub> )  | 33             |

| Junction to Case $(\theta_{JC})$        | 2              |

For the latest package outline information and land patterns (footprints), go to <a href="https://www.analog.com/en/design-center/packaging-quality-symbols-footprints/package-index.html">https://www.analog.com/en/design-center/packaging-quality-symbols-footprints/package-index.html</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.analog.com/en/technical-articles/thermal-characterization-of-ic-packages.html">https://www.analog.com/en/technical-articles/thermal-characterization-of-ic-packages.html</a>.

# **Electrical Characteristics**

(Global conditions unless otherwise stated.  $V_{DDHV}$  = 5V,  $V_{DRV}$  = 4V,  $V_{IN}$ + =  $V_{IN}$ - =  $V_{DRV}$ /2, Analog Filter BW = 1.2kHz, Typical values at 25°C, Min\Max Temperature = -40°C  $\leq$  T<sub>A</sub>  $\leq$  +125°C.)

| PARAMETER                        | SYMBOL            |                                                                                                                          | NDITIONS                                                                                                                    | MIN                        | TYP                                                                                                                                         | MAX                        | UNITS |

|----------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-------|

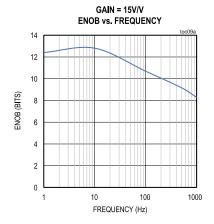

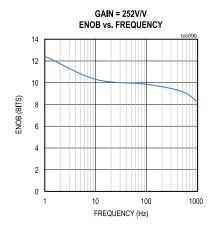

| System Level Performance: Noise- |                   | 4mV (DC), G = 25                                                                                                         | $V_{DRV}$ = 4V, 10k $\Omega$ bridge, $V_{INP}$ + $-V_{INP}$ - = 4mV (DC), G = 252V/V, Noise BW 3dB = 1kHz, $G_{OUT}$ = 4V/V |                            | 12.4                                                                                                                                        |                            |       |

| Free Effective<br>Resolution     |                   | $I_{DRV}$ = 500μA, 3.5kΩ bridge, $V_{INP}$ + – $V_{INP}$ - = 75mV (DC), G = 15V/V, Noise BW 3dB = 1kHz, $G_{OUT}$ = 1V/V |                                                                                                                             |                            | 12.8                                                                                                                                        |                            | bits  |

| INPUT PGA                        |                   |                                                                                                                          |                                                                                                                             |                            |                                                                                                                                             |                            |       |

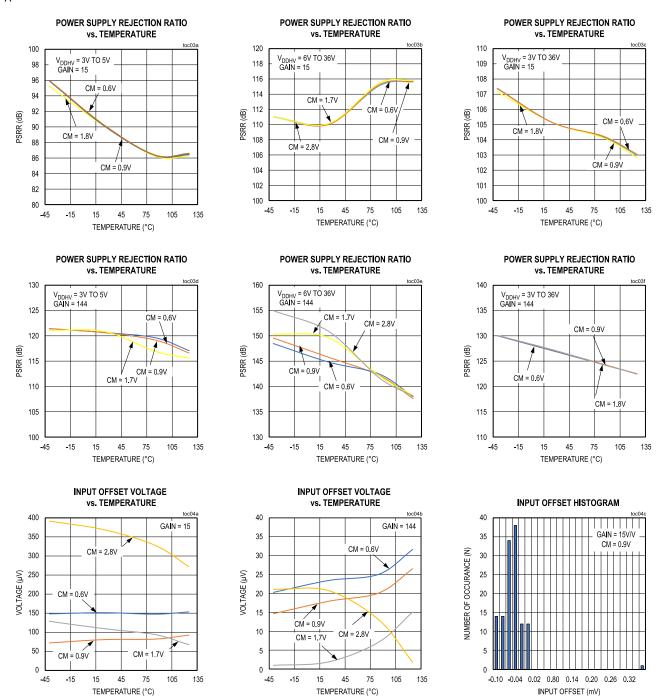

|                                  |                   | G = 15V/V                                                                                                                | 0.6V < V <sub>CM</sub> < 1.7V                                                                                               |                            | 180                                                                                                                                         | 850                        |       |

| Input Offset Voltage Vo          | V <sub>OS</sub>   | Zero-pressure offset compensation disabled                                                                               | 1.7V < V <sub>CM</sub> < 2.8V                                                                                               |                            | 440                                                                                                                                         | 2000                       | wV    |

|                                  | .03               | G = 144V/V<br>Zero-pressure<br>offset<br>compensation<br>disabled                                                        | 0.6V < V <sub>CM</sub> < 2.8V                                                                                               |                            | 76                                                                                                                                          | 450                        | μV    |

|                                  | -0.4              | V <sub>CM</sub> > 1.7V                                                                                                   |                                                                                                                             |                            | 0.062                                                                                                                                       | 1.6                        |       |

| Input Offset Drift               | TCV <sub>OS</sub> | V <sub>CM</sub> < 1.7V                                                                                                   |                                                                                                                             |                            | 0.018                                                                                                                                       | 0.8                        | μV/°C |

|                                  |                   | T <sub>A</sub> = +25°C                                                                                                   |                                                                                                                             |                            | 60                                                                                                                                          | 400                        |       |

| Input Bias Current               | Ι <sub>Β</sub>    | -40°C ≤ T <sub>A</sub> ≤ +125                                                                                            | -40°C ≤ T <sub>A</sub> ≤ +125°C                                                                                             |                            |                                                                                                                                             | 3860                       | pA    |

| Input Offset Current             | I <sub>OS</sub>   |                                                                                                                          |                                                                                                                             |                            | 9.2                                                                                                                                         | 400                        | pA    |

|                                  | V <sub>CM</sub>   | Zero-pressure<br>offset<br>compensation<br>disabled                                                                      | V <sub>DDHV</sub> ≥ 4.4V                                                                                                    | 0.6                        |                                                                                                                                             | 2.8                        | -     |

| Input Common Mode                |                   |                                                                                                                          | 3.8V ≤ V <sub>DDHV</sub> ≤ 4.4V                                                                                             | 0.6                        |                                                                                                                                             | 2.6                        |       |

| Range                            |                   |                                                                                                                          | V <sub>DDHV</sub> ≤ 3.8V                                                                                                    | 0.6                        |                                                                                                                                             | V <sub>VDDHV</sub><br>-1.2 |       |

|                                  |                   | Zero-pressure offs enabled                                                                                               | set compensation                                                                                                            | 0.37 x<br>V <sub>DRV</sub> |                                                                                                                                             | 0.63 x<br>V <sub>DRV</sub> | V     |

| Range of Gain                    | G                 | Programmable<br>through 1-wire<br>and/or I <sup>2</sup> C                                                                | Internal ADC Input<br>Full-Scale Range is<br>1.25V                                                                          |                            | 5, 10,<br>15, 20,<br>24, 40,<br>60,<br>72,<br>90,<br>108,<br>126,<br>144,<br>160,<br>180,<br>200,<br>252,<br>540,<br>1080,<br>1440,<br>2520 |                            | V/V   |

| Gain Selection Settling<br>Time  |                   |                                                                                                                          |                                                                                                                             |                            | 10                                                                                                                                          |                            | ms    |

(Global conditions unless otherwise stated.  $V_{DDHV}$  = 5V,  $V_{DRV}$  = 4V,  $V_{IN}$ + =  $V_{IN}$ - =  $V_{DRV}$ /2, Analog Filter BW = 1.2kHz, Typical values at 25°C, Min\Max Temperature = -40°C  $\leq$  T<sub>A</sub>  $\leq$  +125°C.)

| PARAMETER                          | SYMBOL            | CONI                                                       | DITIONS                                                                                  | MIN  | TYP                                                                           | MAX   | UNITS             |

|------------------------------------|-------------------|------------------------------------------------------------|------------------------------------------------------------------------------------------|------|-------------------------------------------------------------------------------|-------|-------------------|

| O-: F                              | O.F.              | G = 15V/V                                                  |                                                                                          |      | 0.15                                                                          | 0.9   | 0/                |

| Gain Error                         | GE                | G = 144V/V                                                 |                                                                                          |      | 0.45                                                                          | 1.4   | %                 |

| Gain Error Temperature             | TC <sub>GE</sub>  | G = 15V/V                                                  |                                                                                          |      | 4                                                                             |       | n no ma /0C       |

| Coefficient                        | IOGE              | G = 144V/V                                                 |                                                                                          |      | 9                                                                             |       | ppm/°C            |

| INPUT PGA/AC SPECIFI               | CATIONS           |                                                            |                                                                                          |      |                                                                               |       |                   |

| Ciarra I Danadari dili             | BW <sub>3dB</sub> | G = 15V/V                                                  |                                                                                          |      | 55                                                                            |       | 1.11=             |

| Signal Bandwidth                   | PM30B             | G = 144V/V                                                 |                                                                                          |      | 24.5                                                                          |       | kHz               |

|                                    |                   | 0.1Hz ≤ f ≤ 1kHz,                                          | Zero-pressure offset compensation disabled                                               |      | 2.5                                                                           |       |                   |

|                                    | V                 | G = 15V/V                                                  | Zero-pressure<br>offset<br>compensation<br>enabled (at<br>30mV/V)                        |      | 2.7                                                                           |       |                   |

| Input Voltage-Noise V <sub>N</sub> | ۷N                | V <sub>N</sub>                                             | Zero-pressure<br>offset<br>compensation<br>disabled                                      |      | 0.23                                                                          |       | μV <sub>RMS</sub> |

|                                    |                   | 0.1Hz ≤ f ≤ 10Hz,<br>G = 144V/V                            | Zero-pressure<br>offset<br>compensation<br>enabled (at<br>80mV/V)                        |      | 0.78                                                                          |       |                   |

| EMI Rejection Ratio                | EMIRR             | V <sub>RFpeak</sub> = 100mVp<br>900MHz, 1800MHz<br>and IN- | , f = 400MHz,<br>, 2400MHz, both IN+                                                     |      | 80                                                                            |       | dB                |

| INPUT PGA/ZERO-PRES                | SURE OFFSET       | COMPENSATION                                               |                                                                                          |      |                                                                               |       |                   |

| Resolution                         |                   | Including sign                                             | Corresponds to 44µV/V                                                                    |      | 12                                                                            |       | bits              |

| Offset Range                       |                   |                                                            |                                                                                          | 80   | 93                                                                            |       | mV/V              |

| TEMPERATURE MEASU                  | REMENT            |                                                            |                                                                                          |      |                                                                               |       |                   |

| Current Source Range               |                   | Sourced at INT pin<br>V <sub>INT</sub> = 0V to 1.6V        |                                                                                          |      | 150,<br>250,<br>500, 750                                                      |       | uA                |

| Input Common Mode<br>Range         | V <sub>CM</sub>   | Guaranteed by CMI                                          | RR parameter                                                                             | 0.25 |                                                                               | 1.6   | V                 |

| Common Mode<br>Rejection Rate      | CMRR              | V <sub>CM</sub> = 0.25V to 1.6                             | V                                                                                        |      | 95                                                                            |       | dB                |

| Range of Gain                      | G                 | Programmable<br>through 1-wire<br>and/or I <sup>2</sup> C  | G = 1, 1.5, and 2<br>are for single-<br>ended only. G = 3<br>is for differential<br>only |      | 1.5, 2, 3,<br>5, 6, 10,<br>15, 20,<br>24, 30,<br>36, 40,<br>45, 60,<br>72, 90 |       | V/V               |

| Input Offset Voltage               | V <sub>OS</sub>   |                                                            | •                                                                                        |      | 50                                                                            | 2,000 | μV                |

| Gain Error                         | GE                | Gain = 10V/V                                               |                                                                                          |      | ±0.4                                                                          | ±2.5  | %                 |

(Global conditions unless otherwise stated.  $V_{DDHV}$  = 5V,  $V_{DRV}$  = 4V,  $V_{IN}$ + =  $V_{IN}$ - =  $V_{DRV}$ /2, Analog Filter BW = 1.2kHz, Typical values at 25°C, Min\Max Temperature = -40°C  $\leq$  T<sub>A</sub>  $\leq$  +125°C.)

| PARAMETER                                  | SYMBOL            | CONDITIONS                                                                         |                                     | MIN | TYP                                                         | MAX | UNITS              |

|--------------------------------------------|-------------------|------------------------------------------------------------------------------------|-------------------------------------|-----|-------------------------------------------------------------|-----|--------------------|

| Gain-Bandwidth Product                     | GBW               |                                                                                    |                                     |     | 200                                                         |     | kHz                |

| Input Voltage-Noise<br>Density             | V <sub>N</sub>    | f = 1kHz                                                                           |                                     |     | 180                                                         |     | nV/√ <del>Hz</del> |

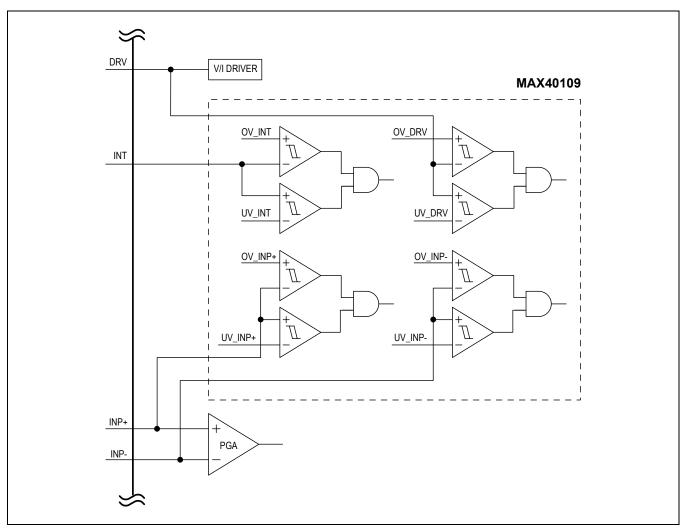

| BRIDGE DIAGNOSTICS                         |                   |                                                                                    |                                     |     |                                                             |     |                    |

| Diagnostic Voltage<br>Threshold Resolution |                   | Applies to all: OV_IN OV_INP+, UV_INP+, UV_INP+, OV_DRV, UV_DRV, OV_INT, UV_INT    |                                     |     | 8                                                           |     | bits               |

| Diagnostic Voltage                         |                   | Applies to all: OV_INP+, OV_INP-, UV_INP+, UV_INP-, OV_DRV, UV_DRV, OV_INT, UV_INT | From 0% to 90% of V <sub>DD5V</sub> |     | ±3                                                          |     |                    |

| Threshold Accuracy                         |                   | Applies to all: OV_INP+, OV_INP-, UV_INP+, UV_INP, OV_DRV, UV_DRV, OV_INT, UV_INT  | Above 90% of V <sub>DD5V</sub>      |     | -3 ±2                                                       |     | LSB                |

| ANALOG-TO-DIGITAL C                        | ONVERTER          | 1                                                                                  | 1                                   |     |                                                             |     |                    |

| Sample Frequency                           |                   |                                                                                    |                                     |     | 1, 2, 4,<br>8, 16                                           |     | ksps               |

| SENSOR BRIDGE VOLT                         | AGE SOURCE        |                                                                                    |                                     |     |                                                             |     |                    |

| Voltage Source Range                       | $V_{DRV}$         | Programmable<br>through Digital<br>Interfaces                                      | I <sub>DRV</sub> = 0mA to 2mA       |     | 1.8, 2.3,<br>3.3, 4.0                                       |     | V                  |

| Voltage Source Range<br>Accuracy           | $\Delta V_{DRV}$  | I <sub>DRV</sub> = 0mA to 2mA                                                      |                                     |     |                                                             | 3.5 | %                  |

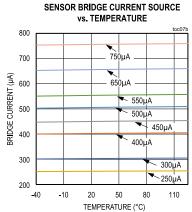

| SENSOR BRIDGE CURR                         | ENT SOURCE        |                                                                                    |                                     |     |                                                             |     |                    |

| Current Source Range                       | I <sub>DRV</sub>  | Programmable<br>through 1-wire<br>and/or I <sup>2</sup> C                          | V <sub>DRV</sub> = 4V               | _   | 250,<br>300,<br>400,<br>450,<br>500,<br>550,<br>650,<br>750 | _   | μА                 |

| Current Source Range<br>Accuracy           | ΔI <sub>DRV</sub> | V <sub>DRV</sub> = 0V to 4V                                                        |                                     |     |                                                             | 5   | %                  |

(Global conditions unless otherwise stated.  $V_{DDHV}$  = 5V,  $V_{DRV}$  = 4V,  $V_{IN}$ + =  $V_{IN}$ - =  $V_{DRV}$ /2, Analog Filter BW = 1.2kHz, Typical values at 25°C, Min\Max Temperature = -40°C  $\leq$  T<sub>A</sub>  $\leq$  +125°C.)

| PARAMETER                             | SYMBOL                                                          | COND                                 | ITIONS                                                                                             | MIN  | TYP  | MAX                                     | UNITS  |

|---------------------------------------|-----------------------------------------------------------------|--------------------------------------|----------------------------------------------------------------------------------------------------|------|------|-----------------------------------------|--------|

| Voltage Range at Bridge<br>Top        | .,                                                              | V <sub>DDHV</sub> ≥ 4.65V            | Zero-pressure compensation offset enabled  Guaranteed by Input Referred Residual Voltage           | 1.8  |      | 4.2                                     | V      |

|                                       | V <sub>DRV</sub>                                                | 3V ≤<br>V <sub>DDHV</sub> ≤ 4.65V    | Zero-pressure compensation offset enabled  Guaranteed by Input Referred Residual Voltage           | 1.8  |      | 3 x In<br>(V <sub>DDHV</sub> )<br>-0.41 | V      |

| Input Referred Residual<br>Voltage    | V <sub>RES</sub>                                                | Top" specification. Z                | Applies over "Voltage Range at Bridge Top" specification. Zero-pressure compensation offset = FS/4 |      |      | ±3                                      | mV     |

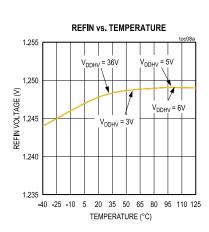

| INTERNAL/EXTERNAL R                   | REFERENCE                                                       | Impatt OA Gain - To                  | ,                                                                                                  |      |      |                                         |        |

| Reference Voltage                     | V <sub>REF</sub>                                                |                                      |                                                                                                    |      | 1.25 |                                         | V      |

| Internal Reference<br>Voltage Temp-Co | V <sub>REFTC</sub>                                              |                                      |                                                                                                    |      | 15   |                                         | ppm/°C |

| OUTPUT AMPLIFIER AN                   | D DIGITAL TO                                                    | ANALOG CONVERTE                      | R                                                                                                  |      |      |                                         |        |

|                                       | G <sub>OUT</sub>                                                | Current (4mA-20mA) Output            |                                                                                                    |      | 1    |                                         |        |

| Gain                                  |                                                                 | Voltage Output, 5V                   | DAC Full-Scale<br>1.25V, V <sub>DDHV</sub> =<br>5.5V                                               |      | 4    |                                         | V/V    |

|                                       |                                                                 | Voltage Output, 3V                   | DAC Full-Scale<br>0.5V, V <sub>DDHV</sub> =<br>3.3V                                                |      | 6    |                                         |        |

| Output Voltage High                   | V <sub>OH</sub>                                                 | V <sub>DD5V</sub> - V <sub>OUT</sub> | $R_L$ = 10KΩ to GND                                                                                |      | 94   | 160                                     | mV     |

| Output Voltage Low                    | $V_{OL}$                                                        | V <sub>OUT</sub> - GND               | $R_L$ = 10KΩ to GND                                                                                |      | 3    | 15                                      | mV     |

| Slew Rate                             | SR                                                              |                                      |                                                                                                    |      | 0.12 |                                         | V/µs   |

| Capacitive Loading<br>Stability       | C <sub>LOAD</sub>                                               | A <sub>V</sub> = 4V/V                |                                                                                                    |      | 500  |                                         | pF     |

| POWER SUPPLY                          |                                                                 | Ta                                   | - 1000 -                                                                                           |      |      |                                         |        |

| Supply Voltage                        | $V_{DDHV}$                                                      | Guaranteed by PSRI<br>+125°C         | K, -40°C < T <sub>A</sub> <                                                                        | 3    |      | 36                                      | V      |

| Internal Digital Supply<br>Voltage    | $V_{DD2V}$                                                      |                                      |                                                                                                    | 1.7  | 1.8  | 1.9                                     | V      |

| Internal Analog Supply<br>Voltage     | $V_{\text{DD5V}}$                                               | V <sub>DDHV</sub> ≥ 6V               |                                                                                                    | 5.05 | 5.28 | 5.5                                     | V      |

| Internal Analog Supply LDO Dropout    | V <sub>DDHV</sub> –<br>V <sub>DD5V</sub><br>V <sub>DDHV</sub> – | V <sub>DDHV</sub> = 5V               |                                                                                                    |      | 121  | 201                                     | mV     |

| ·                                     | V <sub>DD5V</sub>                                               | V <sub>DDHV</sub> = 3V               |                                                                                                    |      | 121  | 199                                     |        |

| Power Supply Rejection<br>Ratio       | PSRR                                                            | 6 ≤ V <sub>DDHV</sub> ≤ 36V          |                                                                                                    |      | 105  |                                         | dB     |

(Global conditions unless otherwise stated.  $V_{DDHV}$  = 5V,  $V_{DRV}$  = 4V,  $V_{IN}$ + =  $V_{IN}$ - =  $V_{DRV}$ /2, Analog Filter BW = 1.2kHz, Typical values at 25°C, Min\Max Temperature = -40°C  $\leq$  T<sub>A</sub>  $\leq$  +125°C.)

| PARAMETER                                                                          | SYMBOL               | COND                            | CONDITIONS                                               |                                    | TYP    | MAX                        | UNITS |

|------------------------------------------------------------------------------------|----------------------|---------------------------------|----------------------------------------------------------|------------------------------------|--------|----------------------------|-------|

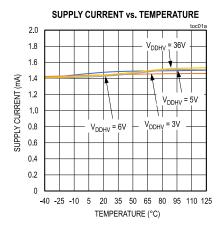

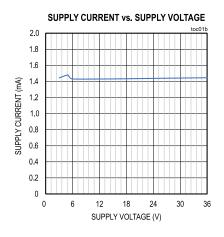

| Supply Current                                                                     | I <sub>DD</sub>      |                                 |                                                          |                                    | 2      | 2.57                       | mA    |

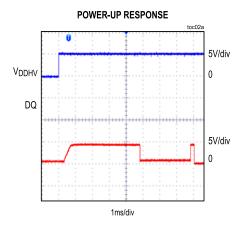

|                                                                                    |                      |                                 | Communication ready                                      |                                    | 2      |                            |       |

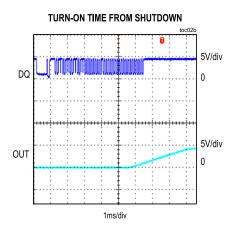

| Power-Up Time                                                                      | <sup>t</sup> ON      | V <sub>DDHV</sub> = 0V to 5V    | ADC Calibration<br>completed – Ready<br>for Measurements |                                    | 140    |                            | ms    |

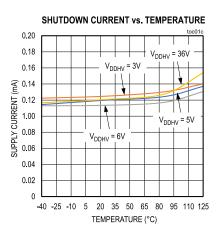

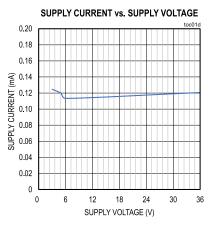

| Low-Power Mode<br>Supply Current                                                   | I <sub>SHDN</sub>    | -40°C ≤ T <sub>A</sub> ≤ +125°C |                                                          |                                    |        | 250                        | μA    |

| Turn-On Time                                                                       | tONSD                | From Low-Power Mo               | ode (through I <sup>2</sup> C)                           |                                    | 50     |                            | μs    |

| I <sup>2</sup> C LOGIC DC CHARAC                                                   | TERISTICS            |                                 |                                                          |                                    |        |                            |       |

| Input High Voltage                                                                 | V <sub>IH</sub>      |                                 |                                                          | 0.7 x<br>V <sub>DD5V</sub>         |        |                            | V     |

| Input Low Voltage                                                                  | $V_{IL}$             |                                 |                                                          |                                    |        | 0.3 x<br>V <sub>DD5V</sub> | V     |

| Input High Leakage<br>Current                                                      | lін                  | Logic Input to V <sub>DD5</sub> | V                                                        | -1                                 | ±0.005 | +1                         | μA    |

| Input Low Leakage<br>Current                                                       | I <sub>IL</sub>      | Logic Input to 0V               |                                                          | -1                                 | ±0.005 | +1                         | μA    |

| Input Capacitance                                                                  | C <sub>IN</sub>      |                                 |                                                          |                                    | 5      |                            | pF    |

| Output Low Voltage                                                                 | V <sub>OL</sub>      | I <sub>OL</sub> = 3mA           |                                                          | 0                                  |        | 0.3                        | V     |

| Output High Leakage<br>Current                                                     |                      | $V_{OUT} = V_{DD5V}$            |                                                          |                                    | ±0.005 | 1                          | μA    |

| I <sup>2</sup> C TIMING                                                            |                      |                                 |                                                          |                                    |        |                            |       |

| Serial Clock Frequency                                                             | f <sub>SCL</sub>     |                                 |                                                          | 50                                 |        | 1M                         | Hz    |

| Bus Free Time Between<br>Start and Stop<br>Conditions                              | t <sub>BUF</sub>     |                                 |                                                          | 0.5                                |        |                            | μs    |

| START Condition Hold<br>Time                                                       | t <sub>HD:STA</sub>  |                                 |                                                          | 0.26                               |        |                            | μs    |

| STOP Condition Setup<br>Time                                                       | tsu:sto              | 90% of SCL to 10%               | of SDA                                                   | 0.26                               |        |                            | μs    |

| Clock Low Period                                                                   | t <sub>LOW</sub>     |                                 |                                                          | 0.5                                |        |                            | μs    |

| Clock High Period                                                                  | <sup>t</sup> HIGH    |                                 |                                                          | 0.26                               |        |                            | μs    |

| START Condition Setup<br>Time                                                      | t <sub>SU:STA</sub>  | 90% of SCL to 90%               | of SDA                                                   | 0.26                               |        |                            | μs    |

| Data Setup Time                                                                    | t <sub>SU:DAT</sub>  | 10% of SDA to 10%               | of SCL                                                   | 50                                 |        |                            | ns    |

| Data In Hold Time                                                                  | tHD:DAT              | 10% of SCL to 10%               | of SDA                                                   | 0                                  |        |                            | μs    |

| SCL/SDA Rise Time                                                                  | t <sub>R</sub>       |                                 |                                                          |                                    |        | 120                        | ns    |

| SCL/SDA Fall Time                                                                  | t <sub>F</sub>       |                                 |                                                          | 20                                 |        | 120                        | ns    |

| Transmit SDA Fall Time                                                             | t <sub>F</sub>       | Bus capacitance = 5             | 550pF. V <sub>DD</sub> ≥ 2.4V                            | 20 x<br>(V <sub>DD</sub><br>/5.5V) |        | 120                        | ns    |

| SCL Time Low for Reset of Serial Interface                                         | t <sub>TIMEOUT</sub> |                                 |                                                          | 20                                 |        | 45                         | ms    |

| Maximum Pulse Width<br>of Spikes That Must Be<br>Suppressed by the Input<br>Filter |                      |                                 |                                                          |                                    | 50     |                            | ns    |

(Global conditions unless otherwise stated.  $V_{DDHV}$  = 5V,  $V_{DRV}$  = 4V,  $V_{IN}$ + =  $V_{IN}$ - =  $V_{DRV}$ /2, Analog Filter BW = 1.2kHz, Typical values at 25°C, Min\Max Temperature = -40°C  $\leq$  T<sub>A</sub>  $\leq$  +125°C.)

| PARAMETER                            | SYMBOL               | CONI                          | DITIONS                                                         | MIN                         | TYP | MAX                        | UNITS |

|--------------------------------------|----------------------|-------------------------------|-----------------------------------------------------------------|-----------------------------|-----|----------------------------|-------|

| Capacitive Load for<br>Each Bus Line | C <sub>B</sub>       |                               |                                                                 |                             | 550 |                            | pF    |

| 1-Wire LOGIC DC CHAR                 | ACTERISTICS (        | DQ)                           |                                                                 |                             |     |                            |       |

| Input Voltage Level High             | $V_{IH}$             | DQ only                       | $V_{DDHV} = 3V \text{ to}$<br>5.5V                              | 0.8 x<br>V <sub>DDHV</sub>  |     |                            | V     |

| Input Voltage Level Low              | $V_{IL}$             | DQ only                       | V <sub>DDHV</sub> = 3V to 5.5V                                  |                             |     | 0.2 x<br>V <sub>DDHV</sub> | V     |

| Output Voltage Level<br>High         | V <sub>OH</sub>      | DQ only                       | $V_{DDHV} = 3V$ to 5.5V                                         | 0.75 x<br>V <sub>DD5V</sub> |     | 4                          | V     |

| Output Voltage Level<br>Low          | V <sub>OL</sub>      | DQ only                       | V <sub>DDHV</sub> = 3V to<br>5.5V, I <sub>SINK</sub> =<br>500μA |                             |     | 200                        | mV    |

| PLC LOGIC DC CHARAC                  | TERISTICS (INI       | PUT V <sub>DDHV</sub> , OUTPU | T OUT)                                                          |                             |     |                            |       |

| Input Voltage Level High             | V <sub>IN_HIGH</sub> |                               |                                                                 | 31                          |     |                            | V     |

| Input Voltage Level Low              | V <sub>IN_LOW</sub>  |                               |                                                                 |                             |     | 24                         | V     |

| Output Voltage Level<br>High         | V <sub>OH</sub>      | Analog OUT only               | DAC output ≥ 0x3665 (85% of full-scale)                         | 0.82 x<br>FS                |     |                            | V     |

| Output Voltage Level<br>Low          | V <sub>OL</sub>      | Analog OUT only               | DAC output ≤<br>0x0999 (15% of<br>full-scale)                   | 0                           |     | 0.18 x<br>FS               | V     |

| 1-Wire TIMING ON DQ                  |                      |                               |                                                                 |                             |     |                            |       |

| Time Slot                            | t <sub>SLOT</sub>    |                               |                                                                 | 60                          |     | 120                        | μs    |

| Recovery Time                        | t <sub>REC</sub>     |                               |                                                                 | 1                           |     |                            | μs    |

| Write-Zero Low Time                  | $t_{LOW0}$           |                               |                                                                 | 60                          |     | 120                        | μs    |

| Write-One Low Time                   | t <sub>LOW1</sub>    |                               |                                                                 | 1                           |     | 15                         | μs    |

| Read Data Valid                      | t <sub>RDV</sub>     |                               |                                                                 |                             |     | 20                         | μs    |

| Reset Time High                      | t <sub>RSTH</sub>    |                               |                                                                 | 480                         |     |                            | μs    |

| Reset Time Low                       | t <sub>RSTL</sub>    |                               |                                                                 | 480                         |     |                            | μs    |

| Presence-Detect High                 | <sup>t</sup> PDHIGH  |                               |                                                                 | 15                          |     | 60                         | μs    |

| Presence-Detect Low                  | t <sub>PDLOW</sub>   |                               |                                                                 | 60                          |     | 240                        | μs    |

| DQ (Data) Capacitance                | C <sub>IN/OUT</sub>  |                               |                                                                 |                             | 25  |                            | pF    |

| PLC TIMING WITH V <sub>DDH</sub>     | V AS INPUT AN        | D OUT AS OUTPUT               |                                                                 |                             |     |                            |       |

| Time Slot                            | t <sub>SLOT</sub>    |                               |                                                                 | 480                         |     | 960                        | μs    |

| Recovery Time                        | t <sub>REC</sub>     |                               |                                                                 | 8                           |     |                            | μs    |

| Write-Zero Low Time                  | t <sub>LOW0</sub>    |                               |                                                                 | 480                         |     | 960                        | μs    |

| Write-One Low Time                   | t <sub>LOW1</sub>    |                               |                                                                 | 100                         |     | 120                        | μs    |

| Read Data Valid                      | t <sub>RDV</sub>     |                               |                                                                 |                             |     | 120                        | μs    |

| Reset Time High                      | t <sub>RSTH</sub>    |                               |                                                                 | 3.84                        |     |                            | ms    |

| Reset Time Low                       | t <sub>RSTL</sub>    |                               |                                                                 | 3.84                        |     |                            | ms    |

| Presence-Detect High                 | <sup>t</sup> PDHIGH  |                               |                                                                 | 120                         |     | 480                        | μs    |

| Presence-Detect Low                  | t <sub>PDLOW</sub>   |                               |                                                                 | 480                         |     | 1920                       | μs    |

|                                      |                      | •                             |                                                                 | •                           |     |                            |       |

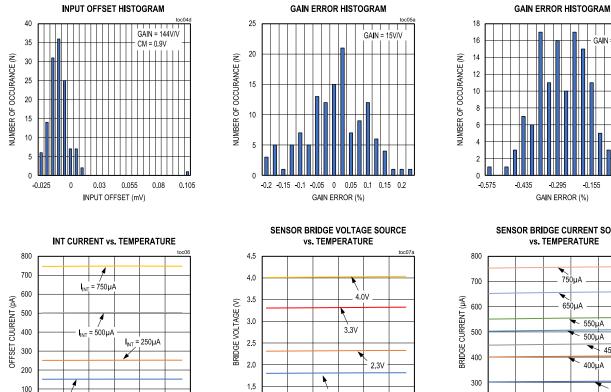

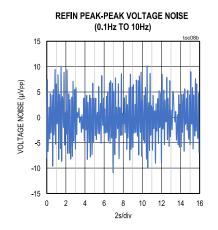

# **Typical Operating Characteristics**

$V_{DDHV}$  = 5V,  $V_{DRV}$  = 4V,  $V_{IN}$ + =  $V_{IN}$ - =  $V_{DRV}$ /2, Analog Filter BW = 1.2kHz, Typical values at 25°C, Min\Max Temperature = -40°C  $\leq$   $T_A \leq +125$ °C.

$V_{DDHV}$  = 5V,  $V_{DRV}$  = 4V,  $V_{IN}$ + =  $V_{IN}$ - =  $V_{DRV}$ /2, Analog Filter BW = 1.2kHz, Typical values at 25°C, Min\Max Temperature = -40°C  $\leq$   $T_A \leq +125$ °C.

100

0

-45

= 150µÅ

TEMPERATURE (°C)

-15

$V_{DDHV} = 5V, \ V_{DRV} = 4V, \ V_{IN} + = V_{IN} - = V_{DRV}/2, \ Analog \ Filter \ BW = 1.2kHz, \ Typical \ values \ at 25°C, \ Min\ Max \ Temperature = -40°C \le 1.00$  $T_A \le +125$ °C.

1.0

<del>-4</del>5

-15

1.8V

45

TEMPERATURE (°C)

105

-0.295

-0.155

-0.15

105 135

$V_{DDHV}$  = 5V,  $V_{DRV}$  = 4V,  $V_{IN}$ + =  $V_{IN}$ - =  $V_{DRV}$ /2, Analog Filter BW = 1.2kHz, Typical values at 25°C, Min\Max Temperature = -40°C  $\leq$   $T_A \leq$  +125°C.

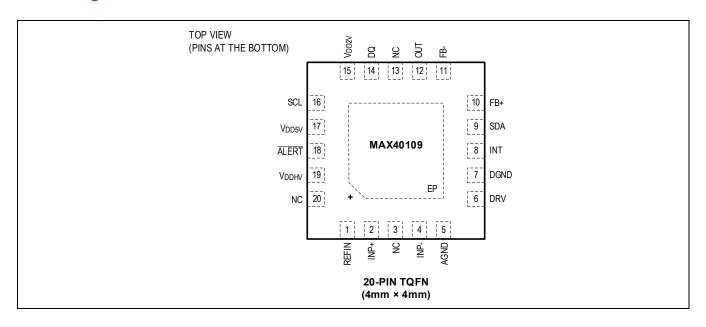

# **Pin Configurations**

# **Pin Descriptions**

| PIN       | NAME              | FUNCTION                                                                                                                                                                                |

|-----------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN       | NAME              |                                                                                                                                                                                         |

| 6         | DRV               | Sensor Bridge Drive: Drive either current or voltage. It is also used to measure the temperature (as a voltage) from the bridge.                                                        |

| 2         | INP+              | Non-inverting Pressure Sensor Input. Users can connect up to 10nF between INP+ and INP                                                                                                  |

| 4         | INP-              | Inverting Pressure Sensor Input. Users can connect up to 10nF between INP+ and INP                                                                                                      |

| 5         | AGND              | Analog Ground                                                                                                                                                                           |

| 7         | DGND              | Digital Ground                                                                                                                                                                          |

| 19        | V <sub>DDHV</sub> | Main positive supply voltage and power line communication serial interface input. The range is from 3V to 36V. The suggested (but not required) bypass capacitor is from 10nF to 100nF. |

| 8         | INT               | Input Temperature: Connect to either a diode or a thermistor.                                                                                                                           |

| 1         | REFIN             | Input reference and also bypass capacitor (100nF) for the Internal reference: A bit in the Config Register selects between external and internal voltage reference.                     |

| 9         | SDA               | I <sup>2</sup> C Data                                                                                                                                                                   |

| 16        | SCL               | I <sup>2</sup> C Clock                                                                                                                                                                  |

| 14        | DQ                | 1-Wire Serial Input/Output. It must be held to a logic level high when idle.                                                                                                            |

| 18        | ALERT             | Active Low Alert Interrupt Output. See the <u>ALERT Mode</u> section for the functionality of this output.                                                                              |

| 10        | FB+               | Output Amplifier Feedback Input, Positive.                                                                                                                                              |

| 11        | FB-               | Output Amplifier Feedback Input, Negative.                                                                                                                                              |

| 12        | OUT               | Analog output, as well as PLC serial interface output.                                                                                                                                  |

| 17        | $V_{DD5V}$        | Internal 5V output from LDO: Bypass with a 220nF capacitor.                                                                                                                             |

| 15        | $V_{DD2V}$        | Internal 1.8V output from LDO: Bypass with a 220nF capacitor.                                                                                                                           |

| 3, 13, 20 | NC                | Do not connect.                                                                                                                                                                         |

| EP        | EP                | Exposed Pad. Connect to analog ground.                                                                                                                                                  |

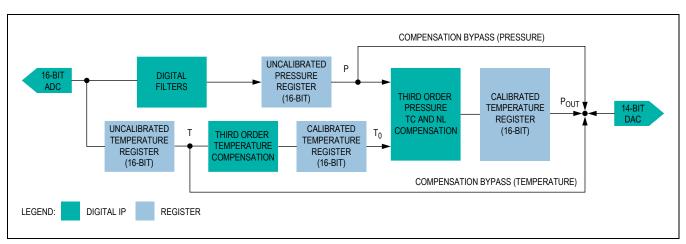

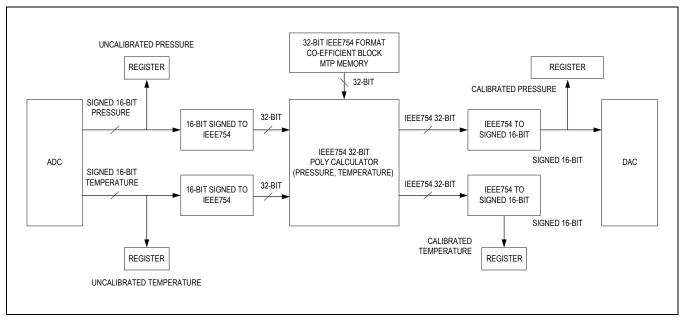

# **Detailed Description**

The MAX40109 is a low-power, precision sensor interface SoC that includes a high-precision, programmable AFE, ADC, calibration memory, and digital signal processing. It also includes a DAC with an output buffer to support analog voltage output and a 4mA–20mA current loop. It is designed for sensor applications such as strain gauges, pressure, force, and temperature.

## **Register Function**

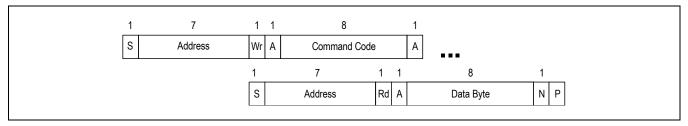

The registers are accessible from all digital interfaces such as 1-Wire, I<sup>2</sup>C, and PLC.

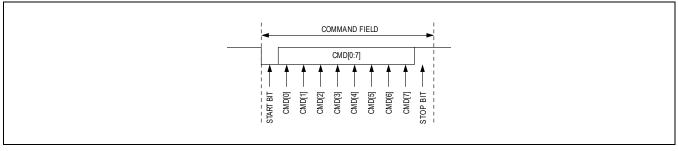

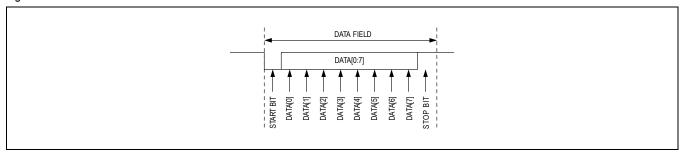

All digital interfaces follow the same sequence of sending the register address first (command field), followed by the data field. Data can be either one byte or two bytes, depending on the type of register.

Upon power-up, all registers listed in <u>Table 1</u> as both Random-access memory (RAM) and Multi-time programmable (MTP) memory will initialize with the last saved content in the MTP memory. Such content can be overwritten during normal functionality, but unless saved in the MTP memory, this new content will be lost once the device is powered down. See the section <u>Burning to MTP</u> for the procedure of saving the register content in the MTP memory.

Table 1. Register Functions and POR States

| REGISTER NAME               | ADDRESS<br>(HEX) | NUMBER<br>OF BITS | POR STATE<br>(HEX) | READ/WRITE | DESCRIPTION                                                                                                                                                                                                                       |

|-----------------------------|------------------|-------------------|--------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Configuration               | 00h              | 16                | 0000h              | R/W        | The configuration register contains bit control for MTP enable, temperature calibration enable, digital filter, reference input, current source reference resistor, shutdown, temperature current, alert mode, and PGA input mux. |

| Status                      | 02h              | 12                | 000h               | R/W        | The status register reports all the anomalies that generate an interrupt on the ALERT output pin.                                                                                                                                 |

| PGA Pressure Gain           | 04h              | 8                 | 00h                | R/W        | The PGA pressure gain register selects between 20 settings.                                                                                                                                                                       |

| Current Source              | 05h              | 3                 | 0h                 | R/W        | The current source register selects between 8 settings.                                                                                                                                                                           |

| Uncalibrated<br>Pressure    | 06h              | 16                | 0000h              | RO         | The uncalibrated pressure register holds the last pressure measurement data from the ADC before the digital calibration.                                                                                                          |

| Uncalibrated<br>Temperature | 08h              | 16                | 0000h              | RO         | The uncalibrated temperature register holds the last temperature measurement from the ADC before the digital calibration.                                                                                                         |

| ADC Sample Rate             | 0Ah              | 4                 | 0h                 | R/W        | The ADC sample rate register contains bits to control the sample rate pressure, sample rate temperature, and system switch time between samples.                                                                                  |

| Interrupt Enable            | 0Bh              | 10                | 3FFh               | R/W        | The interrupt enable register includes the enables for interrupt generation flags with the same bit order as the status register.                                                                                                 |

| Bridge Drive                | 0Dh              | 3                 | 0h                 | R/W        | The bridge drive register connects the sensor bridge to either a current or a voltage source.                                                                                                                                     |

| REGISTER NAME                        | ADDRESS<br>(HEX) | NUMBER<br>OF BITS | POR STATE<br>(HEX) | READ/WRITE | DESCRIPTION                                                                                                                                                                                        |

|--------------------------------------|------------------|-------------------|--------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PGA Temperature<br>Gain              | 0Eh              | 8                 | 0h                 | R/W        | The PGA temperature gain register selects between 16 settings.                                                                                                                                     |

| Calibrated Pressure                  | 0Fh              | 16                | 0000h              | RO         | The calibrated pressure register holds the last pressure measurement after the digital calibration.                                                                                                |

| Calibrated<br>Temperature            | 11h              | 16                | 0000h              | RO         | The calibrated temperature register holds the last temperature measurement after the digital calibration.                                                                                          |

| Temp Mode                            | 13h              | 5                 | 00h                | R/W        | The temp mode register configures the temperature channel at the INT and DRV pins.                                                                                                                 |

| Sensor Offset Cal<br>Config          | 14h              | 3                 | 0h                 | R/W        | The sensor offset cal configuration register is used during the sensor offset calibration procedure to cancel out the sensor offset.                                                               |

| Analog Filter BW                     | 15h              | 2                 | 0h                 | R/W        | The analog filter BW register is used to select the internal analog filter for the pressure channel.                                                                                               |

| Zero Pressure Offset<br>RAM Override | 1Ah              | 16                | 0000h              | R/W        | The zero pressure filter offset RAM override register can override and replace the content of the MTP register "zero pressure offset". This register is only temporary since it is a RAM register. |

| Zero Pressure Offset<br>Select       | 1Ch              | 1                 | 0h                 | R/W        | Sets the zero pressure offset RAM override value.                                                                                                                                                  |

| Analog Output Stage                  | 1Eh              | 4                 | 0h                 | R/W        | The analog output stage register sets the signal at the OUT pin.                                                                                                                                   |

| SLP_MR                               | 9Bh              | 16                | 0000h              | R/W        | Register for initializing MTP.                                                                                                                                                                     |

| SLP_MREF                             | 9Dh              | 16                | 0000h              | R/W        | Register for initializing MTP.                                                                                                                                                                     |

| CP_Control_1                         | 9Fh              | 8                 | 00h                | R/W        | Control register 1.                                                                                                                                                                                |

| CP_Control_2                         | A0h              | 8                 | 00h                | R/W        | Control register 2.                                                                                                                                                                                |

| MTP_Control                          | A2h              | 8                 | 00h                | R/W        | MTP control.                                                                                                                                                                                       |

| MTP_Status                           | A3h              | 8                 | 00h                | R/W        | MTP status.                                                                                                                                                                                        |

| MTP_PROT_ADDR                        | A4h              | 8                 | 00h                | R/W        | MTP prototyping write address.                                                                                                                                                                     |

| MTP_PROT_WDATA                       | A5h              | 16                | 0000h              | R/W        | MTP prototyping write data.                                                                                                                                                                        |

| MTP_PROT_RDATA                       | A7h              | 16                | 0000h              | RO         | MTP prototyping read data                                                                                                                                                                          |

| MTP_LEVEL                            | A9h              | 16                | 00h                | RO         | MTP burn count.                                                                                                                                                                                    |

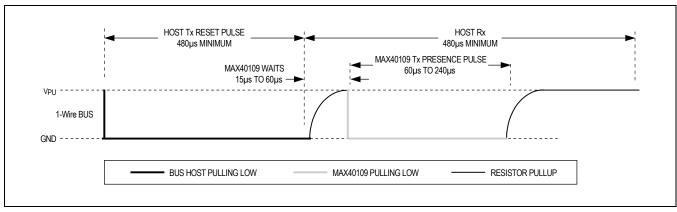

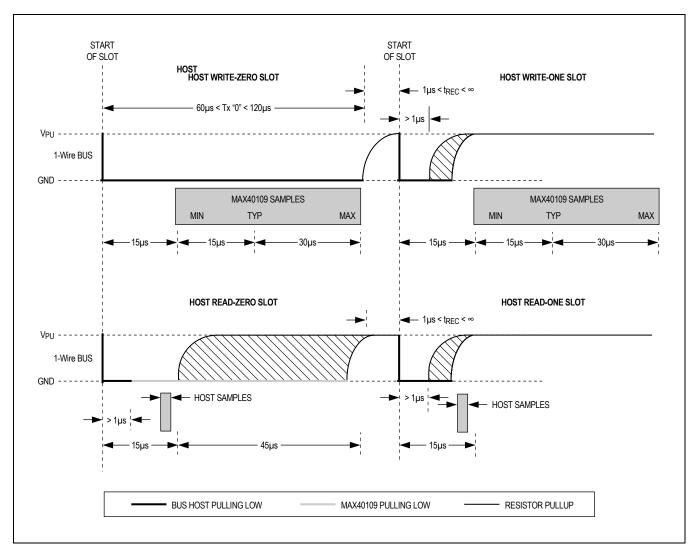

| SLP_MRV                              | ABh              | 16                | 0000h              | R/W        | Register for initializing MTP.                                                                                                                                                                     |