Silicon Carbide Power C3M™ MOSFET Technology N-Channel Enhancement Mode

#### **Features**

- 3rd generation Silicon Carbide (SiC) MOSFET technology

- Optimized package with separate driver source pin

- High blocking voltage with low on-resistance

- High-speed switching with low capacitances

- Fast intrinsic diode with low reverse recovery (Q<sub>rr</sub>)

- Halogen free, RoHS compliant

Wolfspeed, Inc. is in the process of rebranding its products and related materials pursuant to the entity name change from Cree, Inc. to Wolfspeed, Inc. During this transition period, products received may be marked with either the Cree name and/or logo or the Wolfspeed name and/or logo.

| Part Number  | Package      | Marking      |

|--------------|--------------|--------------|

| C3M0032120J1 | TO 263-7L XL | C3M0032120J1 |

## **Applications**

- Solar inverters

- EV motor drive

- High voltage DC/DC converters

- Switched mode power supplies

- Load switch

## **Benefits**

- Reduce switching losses and minimize gate ringing

- Higher system efficiency

- Reduce cooling requirements

- Increase power density

- Increase system switching frequency

#### **Key Parameters**

| Parameter                       | Symbol                                  | Min. | Тур.  | Max            | Unit | Conditions                                                                | Note              |

|---------------------------------|-----------------------------------------|------|-------|----------------|------|---------------------------------------------------------------------------|-------------------|

| Drain - Source Voltage          | V <sub>DS</sub>                         |      |       | 1200           |      | T <sub>c</sub> = 25°C                                                     |                   |

| Maximum Gate - Source Voltage   | V <sub>GS(max)</sub>                    | -8   |       | +19            | v    | Transient                                                                 |                   |

| Operational Gate-Source Voltage | V <sub>GS op</sub>                      |      | -4/15 |                |      | Static                                                                    | Note 1            |

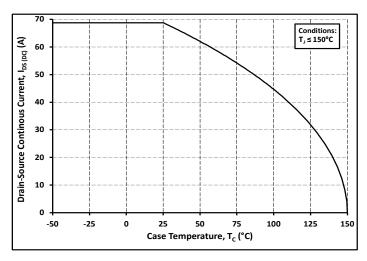

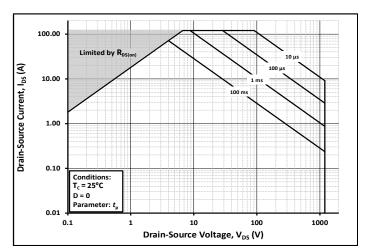

| DC Continuous Drain Current     |                                         |      |       | 68             |      | $V_{GS} = 15 \text{ V}, T_{C} = 25 \text{ °C}, T_{J} \le 150 \text{ °C}$  | Fig. 19<br>Note 2 |

|                                 | l <sub>D</sub>                          |      |       | 44             | Α    | $V_{GS} = 15 \text{ V}, T_{C} = 100 \text{ °C}, T_{J} \le 150 \text{ °C}$ |                   |

| Pulsed Drain Current            | I <sub>DM</sub>                         |      |       | 120            |      | $t_{Pmax}$ limited by $T_{jmax}$<br>$V_{GS} = 15V$ , $T_C = 25$ °C        | Fig. 22           |

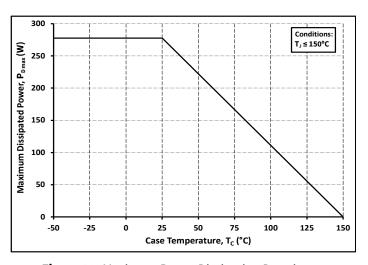

| Power Dissipation               | P <sub>D</sub>                          |      |       | 277            | w    | $T_{c} = 25 ^{\circ} \text{C}, T_{J} = 150 ^{\circ} \text{C}$             | Fig. 20           |

| Operating Junction Temperature  | T,                                      |      |       | -40 to<br>+175 |      |                                                                           |                   |

| Case and Storage Temperature    | $T_{_{\mathrm{c}}},T_{_{\mathrm{stg}}}$ |      |       | -40 to<br>150  | °C   |                                                                           |                   |

| Solder Temperature              | TL                                      |      |       | 260            |      | According to JEDEC J-STD-020                                              |                   |

$Note~(1): Recommended~turn-on~gate~voltage~is~15V~with~\pm 5\%~regulation~tolerance, see~Application~Note~PRD-04814~for~additional~details~turn-on~gate~voltage~is~15V~with~\pm 5\%~regulation~tolerance, see~Application~Note~PRD-04814~for~additional~details~turn-on~gate~voltage~is~15V~with~\pm 5\%~regulation~tolerance, see~Application~Note~PRD-04814~for~additional~details~turn-on~gate~voltage~is~15V~with~\pm 5\%~regulation~tolerance, see~Application~Note~PRD-04814~for~additional~details~turn-on~gate~voltage~is~15V~with~\pm 5\%~regulation~tolerance, see~Application~tolerance~is~15V~with~\pm 5\%~regulation~tolerance~is~15V~with~\pm 5\%~regulation~tolerance~is~15V~wit~\pm 5\%~regulation~tolerance~is~15V~with~\pm 5\%~regulation~tolerance$

Note (2): Verified by design

# **Electrical Characteristics** ( $T_c = 25^{\circ}$ C unless otherwise specified)

| Parameter                                  | Symbol               | Min. | Тур. | Max. | Unit                                                                                  | <b>Test Conditions</b>                                                         | Note        |  |

|--------------------------------------------|----------------------|------|------|------|---------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|-------------|--|

| Drain-Source Breakdown Voltage             | V <sub>(BR)DSS</sub> | 1200 | _    | _    |                                                                                       | $V_{GS} = 0 \text{ V}, I_{D} = 100 \mu\text{A}$                                |             |  |

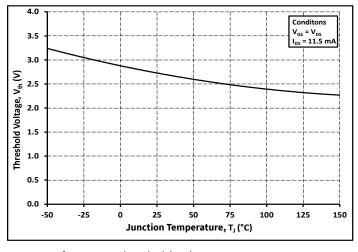

| Cata Thurshald Valta as                    |                      | 1.8  | 2.7  | 3.6  | V                                                                                     | $V_{DS} = V_{GS}$ , $I_{D} = 11.5$ mA, $T_{J} = 25$ °C                         | F: 44       |  |

| Gate Threshold Voltage                     | $V_{GS(th)}$         | _    | 2.2  | _    |                                                                                       | $V_{DS} = V_{GS}, I_D = 11.5 \text{ mA}, T_J = 150^{\circ}\text{C}$            | Fig. 11     |  |

| Zero Gate Voltage Drain Current            | I <sub>DSS</sub>     | _    | 1    | 50   | μΑ                                                                                    | V <sub>DS</sub> = 1200 V, V <sub>GS</sub> = 0 V                                |             |  |

| Gate-Source Leakage Current                | I <sub>GSS</sub>     | _    | 10   | 250  | nA                                                                                    | V <sub>GS</sub> = 15 V, V <sub>DS</sub> = 0 V                                  |             |  |

| Durin Course On State Projeton             |                      | 23   | 32   | 43   |                                                                                       | $V_{GS} = 15 \text{ V}, I_D = 41.4 \text{ A}, T_J = 25^{\circ}\text{C}$        | Fig. 4,     |  |

| Drain-Source On-State Resistance           | R <sub>DS(on)</sub>  | _    | 55   | _    | mΩ                                                                                    | V <sub>GS</sub> = 15 V, I <sub>D</sub> = 41.4 A, T <sub>J</sub> = 150°C        | 5,6         |  |

| Transconductance                           | _                    |      | 25   |      | S                                                                                     | $V_{DS} = 20 \text{ V}, I_{DS} = 41.4 \text{ A}, T_{J} = 25^{\circ}\text{C}$   |             |  |

| Transconductance                           | <b>g</b> fs          | _    | 24   | _    | 3                                                                                     | $V_{DS} = 20 \text{ V}, I_{DS} = 41.4 \text{ A}, T_{J} = 175 ^{\circ}\text{C}$ | Fig. 7      |  |

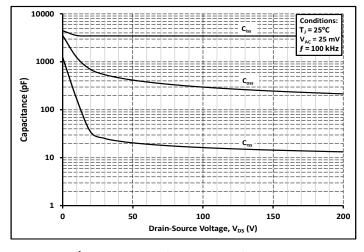

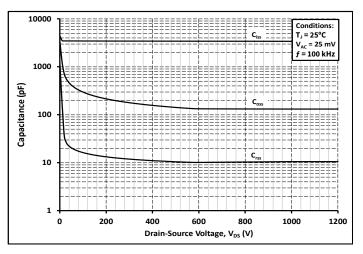

| Input Capacitance                          | C <sub>iss</sub>     | _    | 3424 | _    |                                                                                       |                                                                                | Fig. 17, 18 |  |

| Output Capacitance                         | Coss                 | _    | 133  | _    | pF                                                                                    | $V_{GS} = 0 \text{ V}, V_{DS} = 1000 \text{ V}$                                |             |  |

| Reverse Transfer Capacitance               | C <sub>rss</sub>     | _    | 11   | _    |                                                                                       | $f = 100 \text{ khz}$ $V_{AC} = 25 \text{ mV}$                                 |             |  |

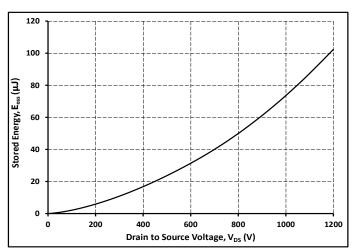

| Output Capacitance Stored Energy           | E <sub>oss</sub>     | _    | 72   | _    | μJ                                                                                    |                                                                                | Fig. 16     |  |

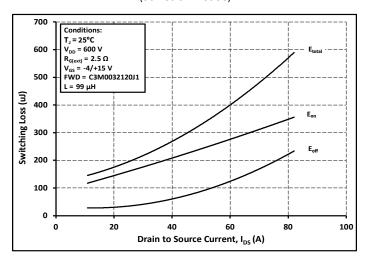

| Turn-On Switching Energy (Body Diode FWD)  | Eon                  | _    | 360  | _    |                                                                                       | $V_{DS} = 800 \text{ V}, V_{GS} = -4 \text{ V}/15 \text{ V},$                  | Fig.        |  |

| Turn-Off Switching Energy (Body Diode FWD) | E <sub>off</sub>     | _    | 90   | _    | μJ                                                                                    | $I_D = 41.4 \text{ A}, R_{G(ext)} = 2.5 \Omega,$<br>$L = 99 \mu H$             | 26          |  |

| Turn-On Delay Time                         | t <sub>d(on)</sub>   | _    | 15   | _    |                                                                                       | $V_{DD} = 800 \text{ V}, V_{GS} = -4 \text{ V}/15 \text{ V}$                   |             |  |

| Rise Time                                  | t <sub>r</sub>       | _    | 16   | _    |                                                                                       | $I_D = 41.4 \text{ A}, R_{G(ext)} = 2.5 \Omega,$                               | Fig. 27     |  |

| Turn-Off Delay Time                        | t <sub>d(off)</sub>  | _    | 25   | _    | ns                                                                                    | L= 99 μH<br>Timing relative to V <sub>DS</sub>                                 |             |  |

| Fall Time                                  | t <sub>f</sub>       | _    | 7    | _    |                                                                                       | Inductive load                                                                 |             |  |

| Internal Gate Resistance                   | R <sub>G(int)</sub>  | _    | 1.6  | _    | Ω                                                                                     | $f = 1 \text{ MHz}, V_{AC} = 25 \text{ mV}$                                    |             |  |

| Gate to Source Charge                      | $Q_{\rm gs}$         | _    | 40   | _    |                                                                                       | $V_{DS} = 800 \text{ V}, V_{GS} = -4 \text{ V}/15 \text{ V}$                   |             |  |

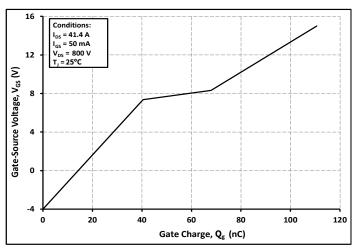

| Gate to Drain Charge                       | $Q_{\rm gd}$         | _    | 28   | _    | $I_{DS} = 800 \text{ V}, V_{GS} = -4 \text{ V}/15 \text{ V}$ $I_{D} = 41.4 \text{ A}$ |                                                                                | Fig. 12     |  |

| Total Gate Charge                          | Qg                   | _    | 111  | _    |                                                                                       | Per IEC60747-8-4 pg 21                                                         |             |  |

# **Reverse Diode Characteristics** ( $T_c = 25^{\circ}$ C unless otherwise specified)

| Parameter                        | Symbol                | Тур. | Max. | Unit | <b>Test Conditions</b>                                                                                                                            | Notes    |

|----------------------------------|-----------------------|------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Diode Forward Voltage            | V                     | 5.0  | _    | .,   | V - 4V 20 A T - 25%                                                                                                                               | Fig.     |

| Diode Forward Voltage            | V <sub>SD</sub>       | 4.5  | _    | V    | $V_{GS} = -4 \text{ V}, I_{SD} = 20 \text{ A}, T_{J} = 25^{\circ}\text{C}$                                                                        | 8, 9, 10 |

| Continuous Diode Forward Current | Is                    | _    | 49   |      | $V_{GS} = -4 \text{ V}, T_J = 150^{\circ}\text{C}, I_{SD} = 20 \text{ A},$                                                                        | Note 1   |

| Diode Pulse Current              | I <sub>S, pulse</sub> | _    | 120  | А    | $V_{GS} = -4 \text{ V}$ , pulse width $t_P$ limited by $T_{j \text{ max}}$                                                                        | Note 1   |

| Reverse Recovery Time            | t <sub>rr</sub>       | 13   | _    | ns   |                                                                                                                                                   |          |

| Reverse Recovery Charge          | Qrr                   | 323  | _    | nC   | $V_{GS} = -4 \text{ V}, I_{SD} = 41.4 \text{ A}, V_{R} = 800 \text{ V},$<br>$di_{z}/dt = 7450 \text{ A}/\mu\text{s}, T_{J} = 150^{\circ}\text{C}$ | Note 1   |

| Peak Reverse Recovery Current    | I <sub>RRM</sub>      | 45   | _    | Α    | γ,, ζ                                                                                                                                             |          |

| Reverse Recovery Time            | t <sub>rr</sub>       | 18   | _    | ns   |                                                                                                                                                   |          |

| Reverse Recovery Charge          | Qrr                   | 164  | _    | nC   | $V_{GS} = -4 \text{ V}, I_{SD} = 41.4 \text{ A}, V_{R} = 800 \text{ V},$<br>$di_z/dt = 2200 \text{ A}/\mu\text{s}, T_J = 150^{\circ}\text{C}$     | Note 1   |

| Peak Reverse Recovery Current    | I <sub>RRM</sub>      | 16   | _    | Α    | μ =====,μ.,μ., .,                                                                                                                                 |          |

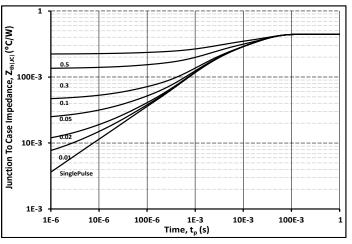

### **Thermal Characteristics**

| Parameter                                   | Symbol          | Тур  | Unit            | Note    |

|---------------------------------------------|-----------------|------|-----------------|---------|

| Thermal Resistance from Junction to Case    | $R_{	heta$ JC   | 0.45 | 9 <i>C</i> /\\\ | Fig. 21 |

| Thermal Resistance From Junction to Ambient | $R_{\theta JA}$ | 40   | °C/W            | Fig. 21 |

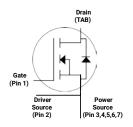

# 4

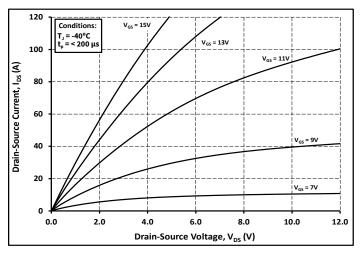

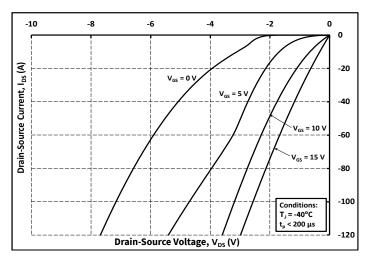

Figure 1. Output Characteristics  $T_1 = -40^{\circ}C$

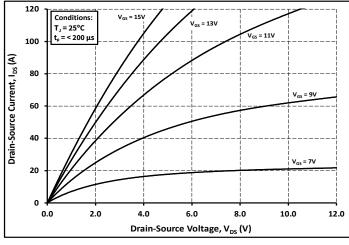

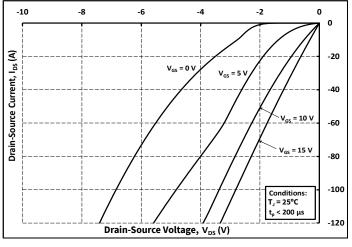

**Figure 2.** Output Characteristics  $T_1 = 25^{\circ}C$

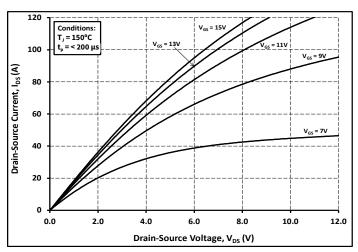

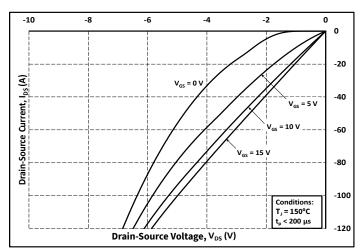

Figure 3. Output Characteristics T<sub>J</sub> = 150°C

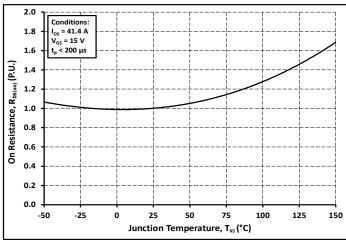

Figure 4. Normalized On-Resistance vs Temperature

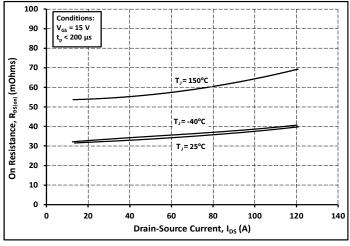

**Figure 5.** On-Resistance vs Drain Current For Various Temperatures

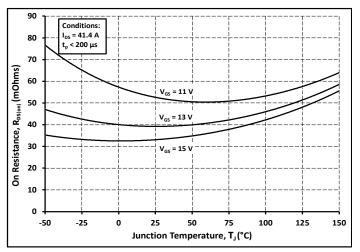

**Figure 6.** On-Resistance vs Temperature For Various Gate Voltage

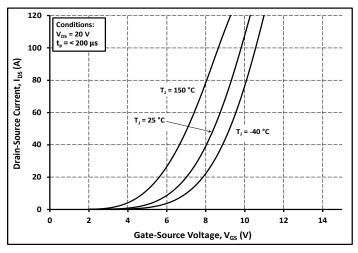

**Figure 7.** Transfer Characteristic for Various Junction Temperatures

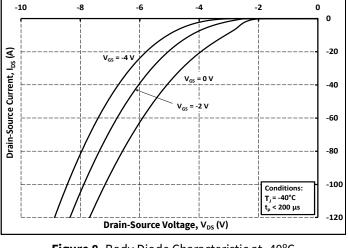

Figure 8. Body Diode Characteristic at -40°C

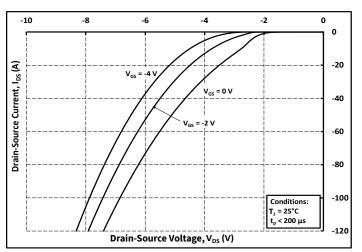

Figure 9. Body Diode Characteristic at 25°C

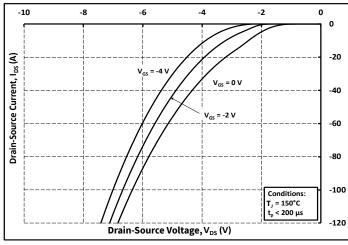

**Figure 10.** Body Diode Characteristic at 150°C

Figure 11. Threshold Voltage vs Temperature

Figure 12. Gate Charge Characteristics

Figure 13. 3rd Quadrant Characteristic at -40°C

Figure 14. 3rd Quadrant Characteristic at 25°C

Figure 15. 3rd Quadrant Characteristic at 150°C

Figure 16. Output Capacitor Stored Energy

**Figure 17.** Capacitances vs Drain-Source Voltage (0 - 200 V)

**Figure 18.** Capacitances vs Drain-Source Voltage (0 - 1200 V)

**Figure 19.** Continuous Drain Current Derating vs Case Temperature

**Figure 21.** Transient Thermal Impedance (Junction - Case)

Figure 23. Clamped Inductive Switching Energy vs Drain Current ( $V_{DD} = 600 \text{ V}$ )

**Figure 20.** Maximum Power Dissipation Derating vs Case Temperature

Figure 22. Safe Operating Area

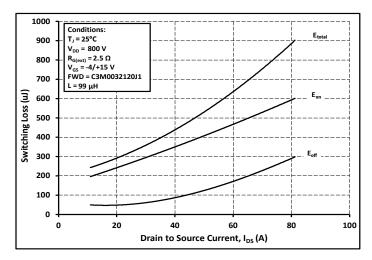

**Figure 24.** Clamped Inductive Switching Energy vs Drain Current  $(V_{DD} = 800 \text{ V})$

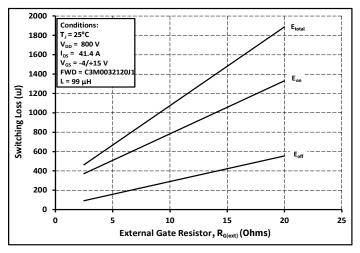

Figure 25. Clamped Inductive Switching Energy vs R<sub>G(ext)</sub>

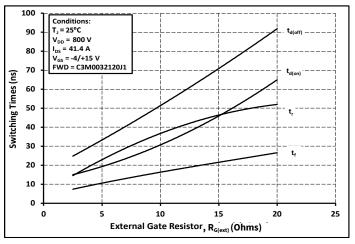

Figure 27. Switching Times vs. R<sub>G(ext)</sub>

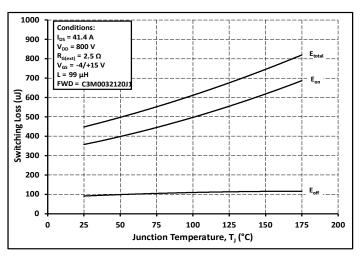

Figure 26. Clamped Inductive Switching Energy vs Temperature

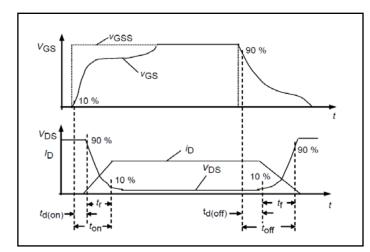

Figure 28. Switching Times Definition

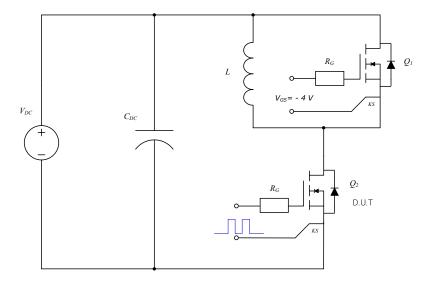

#### **Test Circuit Schematic**

Figure 29. Clamped Inductive Switching Waveform Test Circuit

#### Note:

Turn-off and Turn-on switching energy and timing values measured using SiC MOSFET Body Diode as shown above.

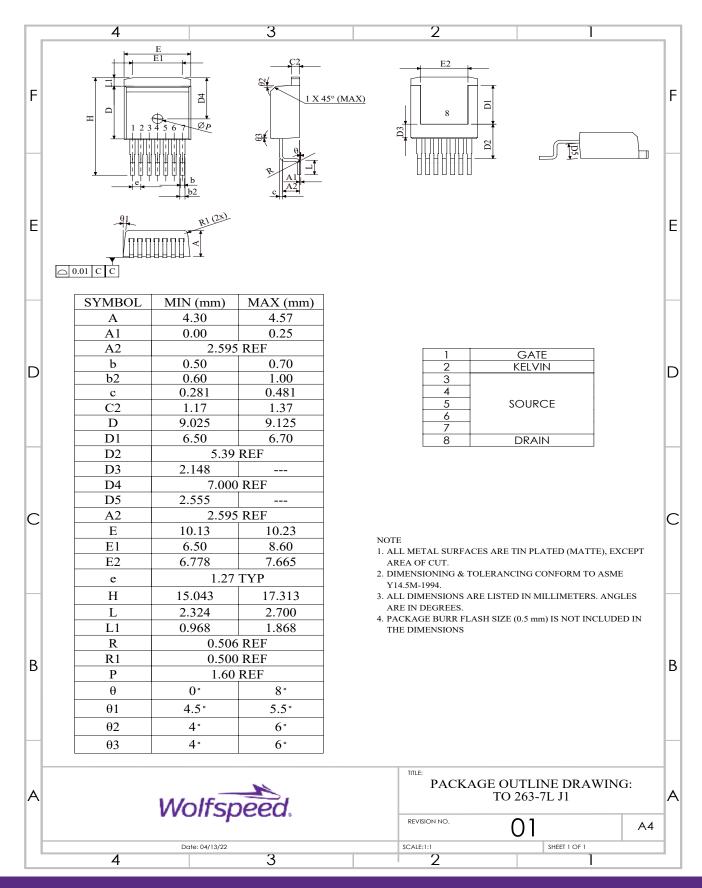

#### Package Dimensions - Package TO-263-7L XL

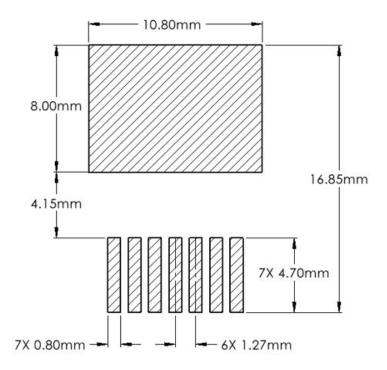

### **Recommended Solder Pad Layout**

# **Revision History**

| Current Revision | Date of Release | Description of Changes                                                                                                   |

|------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------|

| 2                | December-2020   | N/A                                                                                                                      |

| 3                | December-2023   | Updated Wolfspeed branding, package drawing, package image, solder pad layout, added Rev history, Table 1 layout revised |

#### **Related Links**

- SPICE Models

- SiC MOSFET Isolated Gate Driver reference design

- SiC MOSFET Evaluation Board

#### Notes & Disclaimer

This document and the information contained herein are subject to change without notice. Any such change shall be evidenced by the publication of an updated version of this document by Wolfspeed. No communication from any employee or agent of Wolfspeed or any third party shall effect an amendment or modification of this document. No responsibility is assumed by Wolfspeed for any infringement of patents or other rights of third parties which may result from use of the information contained herein. No license is granted by implication or otherwise under any patent or patent rights of Wolfspeed.

Notwithstanding any application-specific information, guidance, assistance, or support that Wolfspeed may provide, the buyer of this product is solely responsible for determining the suitability of this product for the buyer's purposes, including without limitation for use in the applications identified in the next bullet point, and for the compliance of the buyers' products, including those that incorporate this product, with all applicable legal, regulatory, and safety-related requirements.

This product has not been designed or tested for use in, and is not intended for use in, applications in which failure of the product would reasonably be expected to cause death, personal injury, or property damage, including but not limited to equipment implanted into the human body, life-support machines, cardiac defibrillators, and similar emergency medical equipment, aircraft navigation, communication, and control systems, aircraft power and propulsion systems, air traffic control systems, and equipment used in the planning, construction, maintenance, or operation of nuclear facilities.

The Silicon Carbide MOSFET module switches at speeds beyond what is customarily associated with IGBT-based modules. Therefore, special precautions are required to realize optimal performance. The interconnection between the gate driver and module housing needs to be as short as possible. This will afford optimal switching time and avoid the potential for device oscillation. Also, great care is required to insure minimum inductance between the module and DC link capacitors to avoid excessive VDS overshoot.

#### **RoHS Compliance**

The levels of RoHS restricted materials in this product are below the maximum concentration values (also referred to as the threshold limits) permitted for such substances, or are used in an exempted application, in accordance with EU Directive 2011/65/EC (RoHS2), as implemented January 2, 2013. RoHS Declarations for this product can be obtained from your Wolfspeed representative or from the Product Documentation sections of www.wolfspeed.com.

#### **REACh Compliance**

REACh substances of high concern (SVHCs) information is available for this product. Since the European Chemical Agency (ECHA) has published notice of their intent to frequently revise the SVHC listing for the foreseeable future, please contact your Wolfspeed representative to ensure you get the most up-to-date REACh SVHC Declaration. REACh banned substance information (REACh Article 67) is also available upon request.

#### **Contact info:**

4600 Silicon Drive Durham, NC 27703 USA Tel: +1.919.313.5300 www.wolfspeed.com/power