# Please note that Cypress is an Infineon Technologies Company.

The document following this cover page is marked as "Cypress" document as this is the company that originally developed the product. Please note that Infineon will continue to offer the product to new and existing customers as part of the Infineon product portfolio.

## **Continuity of document content**

The fact that Infineon offers the following product as part of the Infineon product portfolio does not lead to any changes to this document. Future revisions will occur when appropriate, and any changes will be set out on the document history page.

# **Continuity of ordering part numbers**

Infineon continues to support existing part numbers. Please continue to use the ordering part numbers listed in the datasheet for ordering.

www.infineon.com

# CY8C201xx Register Reference Guide

# CY8C201xx

# Register Reference Guide

Spec. # 001-45146 Rev. \*G, May 5, 2015

Cypress Semiconductor 198 Champion Court San Jose, CA 95134-1709

Phone (USA): 800.858.1810 Phone (Intnl): 408.943.2600 http://www.cypress.com

#### Copyrights

Copyright © 2008-2015 Cypress Semiconductor Corporation. All rights reserved.

PSoC® is a registered trademark and PSoC Designer™, and Programmable System-on-Chip™ are trademarks of Cypress Semiconductor Corporation (Cypress), along with Cypress® and Cypress Semiconductor™. All other trademarks or registered trademarks referenced herein are the property of their respective owners.

Purchase of  $I^2C$  components from Cypress or one of its sublicensed Associated Companies conveys a license under the Philips  $I^2C$  Patent Rights to use these components in an  $I^2C$  system, provided that the system conforms to the  $I^2C$  Standard Specification as defined by Philips.

The information in this document is subject to change without notice and should not be construed as a commitment by Cypress. While reasonable precautions have been taken, Cypress assumes no responsibility for any errors that may appear in this document. No part of this document may be copied or reproduced in any form or by any means without the prior written consent of Cypress. Made in the U.S.A.

#### Disclaimer

CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes without further notice to the materials described herein. Cypress does not assume any liability arising out of the application or use of any product or circuit described herein. Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress' product in a life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

#### Flash Code Protection

Cypress products meet the specifications contained in their particular Cypress PSoC Data Sheets. Cypress believes that its family of PSoC products is one of the most secure families of its kind on the market today, regardless of how they are used. There may be methods, unknown to Cypress, that can breach the code protection features. Any of these methods, to our knowledge, would be dishonest and possibly illegal. Neither Cypress nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Cypress is willing to work with the customer who is concerned about the integrity of their code. Code protection is constantly evolving. We at Cypress are committed to continuously improving the code protection features of our products.

# Contents

| 1.      | Regis   | ster Map and Reference                     |                |

|---------|---------|--------------------------------------------|----------------|

|         | 1.1     | Maneuvering Around the Registers           |                |

|         | 1.2     | Register Conventions                       |                |

|         | 1.3     | GPIO Status Registers                      |                |

|         | 1.4     | GPIO Setting Registers                     | 10             |

|         | 1.5     | Drive Mode Registers                       |                |

|         | 1.6     | PWM Output Registers                       |                |

|         | 1.7     | Output Control Setting Registers           | 24             |

|         | 1.8     | CapSense Global Parameter Registers        | 30             |

|         | 1.9     | CapSense Sensor Parameter Registers        |                |

|         | 1.10    |                                            |                |

|         | 1.11    | Device Setting Registers                   |                |

|         | 1.12    |                                            | 5 <sup>-</sup> |

|         | 1.13    | CapSense Slider Read-back Values Registers |                |

| Revisio | n Histo | ory                                        | 6′             |

# 1. Register Map and Reference

This chapter is a reference for all the CapSense Express™ registers in address order. The most detailed descriptions of the CapSense Express registers are in the Register Definitions section of each chapter.

# 1.1 Maneuvering Around the Registers

For ease-of-use, this chapter has been formatted so that there is one register per page, although some registers use two pages. On each page, from top to bottom, there are four sections:

- 1. Register name and address (from lowest to highest).

- 2. Register table showing the bit organization, with reserved bits grayed out.

- 3. Written description of register specifics or links to additional register information.

- 4. Detailed register bit descriptions.

Use the register tables, in addition to the detailed register bit descriptions, to determine which bits are reserved. Reserved bits are grayed table cells and are not described in the bit description section. Reserved bits must always be written with a value of '0'.

# 1.2 Register Conventions

This table lists the register conventions that are specific to this chapter.

Table 1-1. Register Conventions

| Convention                   | Example | Description                                            |

|------------------------------|---------|--------------------------------------------------------|

| 'x' in a register name       | PRTxIE  | Multiple instances/address ranges of the same register |

| R                            | R:00    | Read register or bit(s)                                |

| W                            | W:00    | Write register or bit(s)                               |

| WP                           | WPR: 00 | Write register with passcode                           |

| 0                            | RO:00   | Only a read/write register or bit(s).                  |

| L                            | RL:00   | Logical register or bit(s)                             |

| С                            | RC:00   | Clearable register or bit(s)                           |

| 00                           | RW:00   | FD value is 0x00 or 00h                                |

| FD                           |         | Factory default value of the register                  |

| Empty, grayed-out table cell |         | Reserved bit or group of bits, unless otherwise stated |

Table 1-2. Register Map User Space

| Table 1-2.       | Regi            | ster i | viap u | Iser Space      |                 |        |      |                  |                 |        |      |      |                 |        |      |

|------------------|-----------------|--------|--------|-----------------|-----------------|--------|------|------------------|-----------------|--------|------|------|-----------------|--------|------|

| Name             | Addr<br>(0,Hex) | Access | Page   | Name            | Addr<br>(0,Hex) | Access | Page | Name             | Addr<br>(0,Hex) | Access | Page | Name | Addr<br>(0,Hex) | Access | Page |

| INPUT_PORT0      | 00              | R      | 7      | OPR1_PRT0_12    | 40              | RW     | 26   | SLEEP_SA_CTR     | 80              | RW     | 50   |      | C0              |        |      |

| INPUT_PORT1      | 01              | R      | 7      | OPR1_PRT1_12    | 41              | RW     | 27   | CS_READ_BUTTON   | 81              | RW     | 51   |      | C1              |        |      |

| STATUS_PORT0     | 02              | R      | 8      | OPR2_PRT0_12    | 42              | RW     | 28   | CS_READ_BL       | 82              | R      | 52   |      | C2              |        | . I  |

| STATUS_PORT1     | 03              | R      | 8      | OPR2_PRT1_12    | 43              | RW     | 29   |                  | 83              |        | 52   |      | C3              |        |      |

| OUTPUT_PORT0     | 04              | W      | 9      | OP_SEL_13       | 44              | RW     | 24   | CS_READ_DIFF     | 84              | R      | 53   |      | C4              |        | . I  |

| OUTPUT_PORT1     | 05              | W      | 9      | OPR1_PRT0_13    | 45              | RW     | 26   |                  | 85              |        | 53   |      | C5              |        |      |

| CS_ENABLE0       | 06              | RW     | 10     | OPR1_PRT1_13    | 46              | RW     | 27   | CS_READ_RAW      | 86              | R      | 54   |      | C6              |        | . I  |

| CS_ENABLE1       | 07              | RW     | 10     | OPR2_PRT0_13    | 47              | RW     | 29   |                  | 87              |        | 54   |      | C7              |        | . I  |

| GPIO_ENABLE0     | 08              | RW     | 11     | OPR2_PRT1_13    | 48              | RW     | 29   | CS_READ_STATUS   | 88              | R      | 55   |      | C8              |        |      |

| GPIO_ENABLE1     | 09              | RW     | 11     | OP_SEL_14       | 49              | RW     | 24   |                  | 89              |        | 55   |      | C9              |        | . I  |

| INVERSION_MASK0  | 0A              | RW     | 12     | OPR1_PRT0_14    | 4A              | RW     | 26   | CS_READ_CEN_POS  | 8A              | R      | 56   |      | CA              |        | . I  |

| INVERSION_MASK1  | 0B              | RW     | 12     | OPR1_PRT1_14    | 4B              | RW     | 27   |                  | 8B              |        | 56   |      | СВ              |        |      |

| INT_MASK0        | 0C              | RW     | 13     | OPR2_PRT0_14    | 4C              | RW     | 28   | CS_READ_CEN_PEAK | 8C              | R      | 57   |      | СС              |        | . I  |

| INT_MASK1        | 0D              | RW     | 13     | OPR2_PRT1_14    | 4D              | RW     | 29   |                  | 8D              |        | 57   |      | CD              |        | . I  |

| STATUS_HOLD_MSK0 | 0E              | RW     | 14     | CS_NOISE_TH     | 4E              | RW     | 30   |                  | 8E              |        |      |      | CE              |        | . I  |

| STATUS_HOLD_MSK1 | 0F              | RW     | 14     | CS_BL_UPD_TH    | 4F              | RW     | 31   |                  | 8F              |        |      |      | CF              |        | . I  |

| DM_PULL_UP0      | 10              | RW     | 16     | CS_SETL_TIME    | 50              | RW     | 32   |                  | 90              |        |      |      | D0              |        |      |

| DM_STRONG0       | 11              | RW     | 17     | CS_OTH_SET      | 51              | RW     | 33   |                  | 91              |        |      |      | D1              |        |      |

| DM_HIGHZ0        | 12              | RW     | 18     | CS_HYSTERISIS   | 52              | RW     | 34   |                  | 92              |        |      |      | D2              |        |      |

| DM_OD_LOW0       | 13              | RW     | 19     | CS_DEBOUNCE     | 53              | RW     | 35   |                  | 93              |        |      |      | D3              |        |      |

| DM_PULL_UP1      | 14              | RW     | 16     | CS_NEG_NOISE_TH | 54              | RW     | 36   |                  | 94              |        |      |      | D4              |        |      |

| DM_STRONG1       | 15              | RW     | 17     | CS_LOW_BL_RST   | 55              | RW     | 37   |                  | 95              |        | 1    |      | D5              |        | 1    |

| DM_HIGHZ1        | 16              | RW     | 18     | CS_FILTERING    | 56              | RW     | 38   |                  | 96              |        | 1    |      | D6              |        | . I  |

| DM_OD_LOW1       | 17              | RW     | 26     | CS_SCAN_POS_00  | 57              | RW     | 39   |                  | 97              |        | 1    |      | D7              |        | ı I  |

| PWM_ENABLE0      | 18              | RW     | 20     | CS_SCAN_POS_01  | 58              | RW     | 39   |                  | 98              |        | 1    |      | D8              |        |      |

| PWM_ENABLE1      | 19              | RW     | 20     | CS_SCAN_POS_02  | 59              | RW     | 39   |                  | 99              |        | 1    |      | D9              |        | . I  |

| PWM_MODE_DC      | 1A              | RW     | 21     | CS_SCAN_POS_03  | 5A              | RW     | 39   |                  | 9A              |        | 1    |      | DA              |        | . I  |

| PWM_DELAY        | 1B              | RW     | 23     | CS_SCAN_POS_04  | 5B              | RW     | 39   |                  | 9B              |        | 1    |      | DB              |        | . I  |

| OP_SEL_00        | 1C              | RW     | 24     | CS_SCAN_POS_10  | 5C              | RW     | 39   |                  | 9C              |        | 1    |      | DC              |        | . I  |

| OPR1_PRT0_00     | 1D              | RW     | 26     | CS_SCAN_POS_11  | 5D              | RW     | 39   |                  | 9D              |        | 1    |      | DD              |        | ı I  |

| OPR1_PRT1_00     | 1E              | RW     | 27     | CS_SCAN_POS_12  | 5E              | RW     | 39   |                  | 9E              |        | 1    |      | DE              |        |      |

| OPR2_PRT0_00     | 1F              | RW     | 28     | CS_SCAN_POS_13  | 5F              | RW     | 39   |                  | 9F              |        | 1    |      | DF              |        | . I  |

| OPR2_PRT1_00     | 20              | RW     | 29     | CS_SCAN_POS_14  | 60              | RW     | 39   | COMMAND_REG      | A0              | W      | 58   |      | E0              |        |      |

| OP_SEL_01        | 21              | RW     | 24     | CS_FINGER_TH_00 | 61              | RW     | 40   |                  | A1              |        | 1    |      | E1              |        | ı I  |

| OPR1_PRT0_01     | 22              | RW     | 26     | CS_FINGER_TH_01 | 62              | RW     | 40   |                  | A2              |        | 1    |      | E2              |        | . I  |

| OPR1_PRT1_01     | 23              | RW     | 27     | CS_FINGER_TH_02 | 63              | RW     | 40   |                  | A3              |        | 1    |      | E3              |        | . I  |

| OPR2_PRT0_01     | 24              | RW     | 28     | CS_FINGER_TH_03 | 64              | RW     | 40   |                  | A4              |        | 1    |      | E4              |        | ı I  |

| OPR2_PRT1_01     | 25              | RW     | 29     | CS_FINGER_TH_04 | 65              | RW     | 40   |                  | A5              |        | 1    |      | E5              |        | . I  |

| OP_SEL_02        | 26              | RW     | 24     | CS_FINGER_TH_10 | 66              | RW     | 40   |                  | A6              |        | 1    |      | E6              |        | ı I  |

| OPR1_PRT0_02     | 27              | RW     | 26     | CS_FINGER_TH_11 | 67              | RW     | 40   |                  | A7              |        | 1    |      | E7              |        | ı I  |

| OPR1_PRT1_02     | 28              | RW     | 27     | CS_FINGER_TH_12 | 68              | RW     | 40   |                  | A8              |        | 1    |      | E8              |        | . I  |

| OPR2_PRT0_02     | 29              | RW     | 28     | CS_FINGER_TH_13 | 69              | RW     | 40   |                  | A9              |        | 1    |      | E9              |        | ı I  |

| OPR2_PRT1_02     | 2A              | RW     | 29     | CS_FINGER_TH_14 | 6A              | RW     | 40   |                  | AA              |        | 1    |      | EA              |        | . I  |

| OP_SEL_03        | 2B              | RW     | 24     | CS_IDAC_00      | 6B              | RW     | 41   |                  | AB              |        | 1    |      | EB              |        |      |

| OPR1_PRT0_03     | 2C              | RW     | 26     | CS_IDAC_01      | 6C              | RW     | 41   |                  | AC              |        | 1    |      | EC              |        |      |

| OPR1 PRT1 03     | 2D              | RW     | 27     | CS_IDAC_02      | 6D              | RW     | 41   |                  | AD              |        | 1    |      | ED              |        |      |

| OPR2_PRT0_03     | 2E              | RW     | 28     | CS_IDAC_03      | 6E              | RW     | 41   |                  | AE              |        | 1    |      | EE              |        | 1    |

| OPR2_PRT1_03     | 2F              | RW     | 29     | CS_IDAC_04      | 6F              | RW     | 41   |                  | AF              |        |      |      | EF              |        | . I  |

| OP_SEL_04        | 30              | RW     | 24     | CS_IDAC_10      | 70              | RW     | 41   |                  | B0              | _      | ł    |      | F0              |        | ı I  |

| OPR1_PRT0_04     | 31              | RW     | 27     | CS_IDAC_11      | 71              | RW     | 41   |                  | B1              |        | -    |      | F1              | _      | . I  |

| OPR1_PRT1_04     | 32              | RW     | 27     | CS_IDAC_11      | 72              | RW     | 41   |                  | B2              |        | -    |      | F2              |        |      |

| OPR2_PRT0_04     | 33              | RW     | 28     | CS_IDAC_12      | 73              | RW     | 41   |                  | B3              |        |      |      | F3              |        | ı I  |

| OPR2_PRT1_04     | 34              | RW     | 29     | CS_IDAC_14      | 74              | RW     |      |                  | B4              | _      |      |      | F4              |        | ı I  |

| OP SEL 10        |                 |        |        |                 |                 |        | 41   |                  |                 |        | l    |      |                 |        | ı I  |

|                  | 35              | RW     | 24     | CS_SLID_CONFIG  | 75<br>76        | RW     | 42   |                  | B5              |        |      |      | F5              |        |      |

| OPR1_PRT0_10     | 36              | RW     | 26     | CC CLID MULA    | 76              | D\A/   | 42   |                  | B6              |        | 1    |      | F6              |        |      |

| OPR1_PRT1_10     | 37              | RW     | 27     | CS_SLID_MULM    | 77              | RW     | 43   |                  | B7              |        |      |      | F7              |        |      |

| OPR2_PRT0_10     | 38              | RW     | 28     | CS_SLID_MULL    | 78              | RW     | 43   |                  | B8              |        | 1    |      | F8              |        |      |

| OPR2_PRT1_10     | 39              | RW     | 29     | I2C_DEV_LOCK    | 79              | RW     | 44   |                  | B9              |        |      |      | F9              |        |      |

| OP_SEL_11        | 3A              | RW     | 24     | DEVICE_ID       | 7A              | R      | 45   |                  | BA              |        |      |      | FA              |        |      |

| OPR1_PRT0_11     | 3B              | RW     | 26     | DEVICE_STATUS   | 7B              | R      |      |                  | BB              |        |      |      | FB              |        |      |

| OPR1_PRT1_11     | 3C              | RW     | 27     | I2C_ADDR_DM     | 7C              | RW     | 47   |                  | BC              |        | 1    |      | FC              |        |      |

| OPR2_PRT0_11     | 3D              | RW     | 28     |                 | 7D              |        |      |                  | BD              |        |      |      | FD              |        |      |

| OPR2_PRT1_11     | 3E              | RW     | 29     | SLEEP_PIN       | 7E              | RW     | 48   |                  | BE              |        |      |      | FE              |        |      |

| OP_SEL_12        | 3F              | RW     | 24     | SLEEP_CTRL      | 7F              | RW     | 49   |                  | BF              |        | l    |      | FF              |        |      |

Gray fields are reserved. # Access is bit specific.

# 1.3 **GPIO Status Registers**

# 1.3.1 INPUT\_PORTx

## **Input Port 0/1 Registers**

### **Individual Register Names and Addresses:**

INPUT\_PORT0:00h

INPUT\_PORT1:01h

|             | 7 | 6 | 5 | 4 | 3 | 2       | 1 | 0 |

|-------------|---|---|---|---|---|---------|---|---|

| Access : FD |   |   |   |   |   | R:00    |   |   |

| Bit Name    |   |   |   |   |   | GP[4:0] |   |   |

The Input Port registers represent the actual logical levels on the pins and are used for I/O port reading operations. For CapSense® pins, they represent the status of the sensor, ON (1) or OFF (0).

The Inversion registers (0Ah-0Bh) change the state of reads from these ports.

| Bit | Name    | Description                                                                  |

|-----|---------|------------------------------------------------------------------------------|

| 4:0 | GP[4:0] | For GPIOs, these bits represent the read value from port. For CapSense pins: |

|     |         | 0 Sensor OFF.                                                                |

|     |         | 1 Sensor ON.                                                                 |

# 1.3.2 STATUS\_PORTx

## **Status Since Last Read Port 0/1 Registers**

#### **Individual Register Names and Addresses:**

STATUS\_PORT : 02h STATUS\_PORT1 : 03h

0

|             | 7 | 6 | 5 | 4 | 3 | 2       | 1 | 0 |

|-------------|---|---|---|---|---|---------|---|---|

| Access : FD |   |   |   |   |   | R:00    |   |   |

| Bit Name    |   |   |   |   |   | GP[4:0] |   |   |

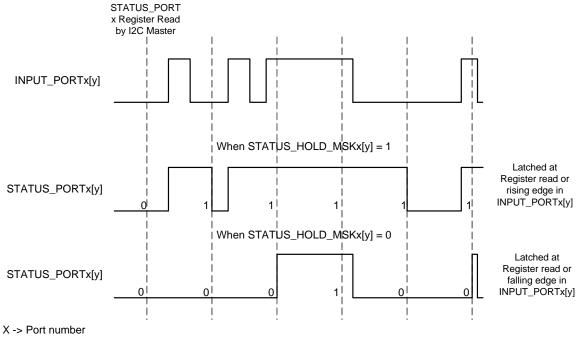

These registers hold the port bit status in the corresponding line since the last read of the register. The status latch direction can be set in registers 0Eh-0Fh. Bits in the STATUS\_PORTx registers are reset to the opposite of registers 0Eh-0Fh after a read of or write to registers 0Eh-0Fh.

| Bit | Name    | Description                                              |

|-----|---------|----------------------------------------------------------|

| 4:0 | GP[4:0] | Status of the port pins since last read of the register. |

# 1.3.3 OUTPUT\_PORTx

## **Output Port 0/1 Registers**

#### **Individual Register Names and Addresses:**

OUTPUT\_PORT0:04h OUTPUT\_PORT1:05h

|             | 7 | 6 | 5 | 4 | 3 | 2       | 1 | 0 |

|-------------|---|---|---|---|---|---------|---|---|

| Access : FD |   |   |   |   |   | W : 00  |   |   |

| Bit Name    |   |   |   |   |   | GP[4:0] |   |   |

These registers are used to write data to GPIO ports. By default, both ports are in high Z mode. Pins defined as CapSense inputs or as output of combinational logic (see registers 1Ch-4Dh) cannot be set using this register.

| Bit | Name    | Description                                                                                                                                                                                  |

|-----|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4:0 | GP[4:0] | A bit set in this register sets the logic level of the output (depending on the drive mode selected as per Table 1-3, "Drive Mode Registers," on page 16).  0 0 logic level.  1 logic level. |

# 1.4 GPIO Setting Registers

## 1.4.1 CS\_ENABLEX

## Select CapSense Input Port 0/1 Registers

#### **Individual Register Names and Addresses:**

CS\_ENABLE0:06h CS\_ENABLE1:07h

|             | 7 | 6 | 5 | 4 | 3 | 2       | 1 | 0 |

|-------------|---|---|---|---|---|---------|---|---|

| Access : FD |   |   |   |   |   | RW: 00  |   |   |

| Bit Name    |   |   |   |   |   | GP[4:0] |   | · |

These registers select which pins of the two ports are to be used as CapSense inputs. If a pin is selected as CapSense input, its configuration in registers 0Ch -0Dh (Interrupt Masks) and 10h-17h (Drive Modes) is ignored.

It is mandatory that you set these registers before finger threshold and IDAC setting (registers 61h to 6Ah and 6Bh to 74h) registers are set.

A pin enabled for CapSense cannot be enabled for GPIO. If a pin needs to be changed from CapSense to GPIO, it first has to be disabled from CapSense and then enabled to GPIO.

Further CapSense pin parameters are configurable in subsequent registers.

These registers have read only access in "Normal Operation Mode" and read/write access in "Setup Operation Mode" (also see the COMMAND\_REG register on page 58).

| Bit | Name    | Description                                                                                                                             |

|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 4:0 | GP[4:0] | These bits are used for selecting the pins of two ports to be used as CapSense inputs.  Disable CapSense input.  Enable CapSense input. |

# 1.4.2 GPIO\_ENABLEx

## Select Enabled GPIO Port 0/1 Registers

#### **Individual Register Names and Addresses:**

GPIO\_ENABLE0:08h GPIO\_ENABLE1:09h

|   |             | 7 | 6 | 5 | 4 | 3 | 2       | 1 | 0 |

|---|-------------|---|---|---|---|---|---------|---|---|

| 1 | Access : FD |   |   |   |   |   | RW: 00  |   |   |

| 1 | Bit Name    |   |   |   |   |   | GP[4:0] |   |   |

These registers are used to select which pins of each port are enabled as GPIO.

Pins not enabled are tri-stated.

A pin enabled for GPIO cannot be enabled for CapSense. If a pin needs to be changed from GPIO to CapSense, it first has to be disabled from GPIO and then enabled to CapSense.

These registers have read only access in "Normal Operation Mode" and read/write access in "Setup Operation Mode" (also see the COMMAND\_REG register on page 58).

| Bit | Name    | Description                                                              |

|-----|---------|--------------------------------------------------------------------------|

| 4:0 | GP[4:0] | These bits are used for selecting the pins of each port enabled as GPIO. |

|     |         | 0 Disable GPIO.                                                          |

|     |         | 1 Enable GPIO.                                                           |

# 1.4.3 INVERSION\_MASKx

## **Inversion Port 0/1 Registers**

#### **Individual Register Names and Addresses:**

INVERSION\_MASK0: 0Ah INVERSION\_MASK1: 0Bh

|             | 7 | 6 | 5 | 4 | 3 | 2       | 1 | 0 |

|-------------|---|---|---|---|---|---------|---|---|

| Access : FD |   |   |   |   |   | RW: 00  |   |   |

| Bit Name    |   |   |   |   |   | GP[4:0] |   |   |

These registers invert the logic of the input ports and also of the "Status since last read" registers. Each '1' written to this register inverts the logic of the corresponding bit in the Input/Status register of the related port. This register is also used to invert the inputs and outputs for the logic operations of the I/O and CapSense pins (see registers 1Ch, 4Eh).

| Bit | Name    | Description                                                                          |

|-----|---------|--------------------------------------------------------------------------------------|

| 4:0 | GP[4:0] | These bits invert the logic of the input ports and status since last read registers. |

|     |         | 0 No inversion.                                                                      |

|     |         | 1 Inversion.                                                                         |

## 1.4.4 INT\_MASKx

### **Interrupt Mask Port 0/1 Registers**

#### **Individual Register Names and Addresses:**

INT\_MASK0:0Ch INT\_MASK1:0Dh

|             | 7 | 6 | 5 | 4 | 3 | 2       | 1 | 0 |

|-------------|---|---|---|---|---|---------|---|---|

| Access : FD |   |   |   |   |   | RW:00   |   |   |

| Bit Name    |   |   |   |   |   | GP[4:0] |   |   |

The INT\_MASKx registers are used to set which GPIO (not CapSense pins) can generate internal hardware interrupts on 0-1 and 1-0 transitions. Its main purpose is to enable wakeup from sleep upon GPIO changes. If a pin is to be configured for an interrupt, it should be enabled as a GPIO using the GPIO\_ENABLEx Register, and the corresponding mask bit in this INT\_MASKx register should be written with a value '1'.

In addition, if a pin is configured as a sleep control pin using the SLEEP\_PIN register, the corresponding bit in the INT\_MASK is automatically enabled.

These registers have read only access in "Normal Operation Mode" and read/write access in "Setup Operation Mode" (also see the COMMAND\_REG register on page 58).

| Bit | Name    | Desc | ription                                                                            |

|-----|---------|------|------------------------------------------------------------------------------------|

| 4:0 | GP[4:0] | 0    | GPIO disabled to generate internal hardware interrupts on 0-1 and 1-0 transitions. |

|     |         | 1    | GPIO enabled to generate internal hardware interrupts on 0-1 and 1-0 transitions.  |

#### STATUS HOLD MSKx 1.4.5

## Port Status Hold Mask Port 0/1 Registers

#### **Individual Register Names and Addresses:**

STATUS\_HOLD\_MSK0: 0Eh STATUS\_HOLD\_MSK1: 0Fh

|        |      | 7 | 6 | 5 | 4 | 3 | 2                      | 1 | 0 |

|--------|------|---|---|---|---|---|------------------------|---|---|

| Access | : FD |   |   |   |   |   | RW: 03/1F <sup>1</sup> |   |   |

| Bit Na | me   |   |   |   |   |   | GP[4:0]                |   |   |

<sup>1. 03</sup> is for CY8C20142 part only

These registers are used to define the value to be held (0 or 1) in registers 02h-03h until the next read. They set the latch direction of registers 02h-03h. This register can be written with a value of 1 only if the corresponding pin is enabled either as a GPIO or as a CapSense button. Else, this register will always return 0.

In the table above, note that reserved bits are grayed table cells and are not described in the bit description section below. Reserved bits must always be written with a value of '0'.

| Bit | Name    | Description                                                          |

|-----|---------|----------------------------------------------------------------------|

| 4:0 | GP[4:0] | These bits are used to set the latch direction of registers 02h-03h. |

Figure 1-1. Latch Direction of STATUS\_PORTx Register

Y -> Port bit

0Eh

# 1.5 Drive Mode Registers

Each port's data pin can be set separately to one of four available drive modes. To perform this configuration, the four drive mode registers are used. Each '1' written to this register changes the corresponding line drive mode. Registers 10h through 17h have last-register priority meaning that the bit set to high in which the last register was written will overwrite those that came before. Reading these registers reflects the actual setting, not what was originally written.

The register settings for bits assigned to CapSense inputs are ignored. Table 1-3 summarizes the drive mode register settings.

Table 1-3. Drive Mode Registers

| Register | Pin State         | Description                          |

|----------|-------------------|--------------------------------------|

| 10h/14h  | Resistive Pull Up | Resistive High, Strong Low (Default) |

| 11h/15h  | Strong Drive      | Strong High, Strong Low              |

| 12h/16h  | High Impedance    | High Z - Analog                      |

| 13h/17h  | Open Drain Low    | Strong Low, High Z High              |

**Note** To enable a GPIO pin for digital input, set it to drive mode open drain low or resistive pull up with its corresponding output registers 04h-05h set to '1'. The high impedance drive mode is used only for analog input (e.g., CapSense) and disconnects the pin from the internal digital bus.

## 1.5.1 DM\_PULL\_UPx

## Pull Up Port 0/1 Registers

#### **Individual Register Names and Addresses:**

DM\_PULL\_UP0:10h DM\_PULL\_UP1:14h

|             | 7 | 6 | 5 | 4 | 3 | 2       | 1 | 0 |

|-------------|---|---|---|---|---|---------|---|---|

| Access : FD |   |   |   |   |   | RW:00   |   |   |

| Bit Name    |   |   |   |   | · | GP[4:0] |   |   |

These registers have read only access in "Normal Operation Mode" and read/write access in "Setup Operation Mode" (also see the COMMAND\_REG register on page 58).

| Bit | Name    | Description                                                          |

|-----|---------|----------------------------------------------------------------------|

| 4:0 | GP[4:0] | These bits are used to set the pull up drive mode for the port pins. |

|     |         | 0                                                                    |

|     |         | 1 Enables pull up drive mode.                                        |

# 1.5.2 DM\_STRONGx

## **Strong Port 0/1 Registers**

#### **Individual Register Names and Addresses:**

DM\_STRONG0: 11h DM\_STRONG1: 15h

|             | 7 | 6 | 5 | 4 | 3 | 2       | 1 | 0 |

|-------------|---|---|---|---|---|---------|---|---|

| Access : FD |   |   |   |   |   | RW: 00  |   |   |

| Bit Name    |   |   |   |   |   | GP[4:0] |   |   |

These registers have read only access in "Normal Operation Mode" and read/write access in "Setup Operation Mode" (also see the COMMAND\_REG register on page 58).

| Bit | Name    | Description                                                   |

|-----|---------|---------------------------------------------------------------|

| 4:0 | GP[4:0] | These bits are used to set the strong mode for the port pins. |

|     |         | 0                                                             |

|     |         | 1 Enables strong drive mode.                                  |

# 1.5.3 DM\_HIGHZx

## High Z Port 0/1 Registers

#### **Individual Register Names and Addresses:**

DM\_HIGHZ0:12h DM\_HIGHZ1:16h

|             | 7 | 6 | 5 | 4 | 3 | 2       | 1 | 0 |

|-------------|---|---|---|---|---|---------|---|---|

| Access : FD |   |   |   |   |   | RW: 00  |   |   |

| Bit Name    |   |   |   | · |   | GP[4:0] |   |   |

These registers have read only access in "Normal Operation Mode" and read/write access in "Setup Operation Mode" (also see the COMMAND\_REG register on page 58).

| Bit | Name    | Description                                                   |

|-----|---------|---------------------------------------------------------------|

| 4:0 | GP[4:0] | These bits are used to set the high Z mode for the port pins. |

|     |         | 0                                                             |

|     |         | 1 Enables high Z drive mode.                                  |

# 1.5.4 DM\_OD\_LOWx

## **Open Drain Low Port 0/1 Registers**

#### **Individual Register Names and Addresses:**

DM\_OD\_LOW0: 13h

DM\_OD\_LOW1:17h

|             | 7 | 6 | 5 | 4 | 3 | 2       | 1 | 0 |

|-------------|---|---|---|---|---|---------|---|---|

| Access : FD |   |   |   |   |   | RW:00   |   |   |

| Bit Name    |   |   |   |   |   | GP[4:0] |   |   |

These registers have read only access in "Normal Operation Mode" and read/write access in "Setup Operation Mode" (also see the COMMAND\_REG register on page 58).

| Bit | Name    | Description                                                           |

|-----|---------|-----------------------------------------------------------------------|

| 4:0 | GP[4:0] | These bits are used to set the open drain low mode for the port pins. |

|     |         | 0                                                                     |

|     |         | 1 Enables open drain low drive mode.                                  |

## 1.6 PWM Output Registers

## 1.6.1 PWM\_ENABLEx

## **PWM Enable 0/1 Registers**

#### **Individual Register Names and Addresses:**

PWM\_ENABLE0: 18h PWM\_ENABLE1: 19h

|             | 7 | 6 | 5 | 4 | 3 | 2       | 1 | 0 |

|-------------|---|---|---|---|---|---------|---|---|

| Access : FD |   |   |   |   |   | RW: 00  |   |   |

| Bit Name    |   |   |   |   |   | GP[4:0] |   |   |

These registers are used to select which GPIO pins are enabled for PWM output. Only pins that have been enabled for GPIO can be enabled for PWM output. These GPIO pins must be previously enabled by writing to the GPIO\_ENABLEx register on page 11. For pins enabled as PWM, their output is set to 0, 1, or the PWM signal, depending on the PWM configuration (PWM\_MODE\_DC register on page 21) and the output settings.

| Bit | Name    | Description                                                               |

|-----|---------|---------------------------------------------------------------------------|

| 4:0 | GP[4:0] | These bits are used to select which GPIO pins are enabled for PWM output. |

|     |         | 0 Disable PWM output.                                                     |

|     |         | 1 Fnable PWM output                                                       |

# 1.6.2 PWM\_MODE\_DC

# **PWM Mode and Duty Cycle Configuration Register**

### **Individual Register Names and Addresses:**

PWM\_MODE\_DC : 1Ah

|             | 7 6       | 5        | 4           | 3 | 2       | 1         | 0 |

|-------------|-----------|----------|-------------|---|---------|-----------|---|

| Access : FD | RW: 00    | RW:00    | RW:00       |   | RW      | : 00      |   |

| Bit Name    | Mode[1:0] | 0/1 Link | Apply Delay |   | Duty Cy | /cle[3:0] |   |

This register controls PWM mode output and duty cycle.

| Bit     | Name               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6     | Mode[1:0]          | Used to select the PWM mode of operation.  Normal mode. PWM output is activated and released the same time as the source event (e.g., a button press).  Single Flash mode. PWM output is activated by one transition event (a button press or release) and released automatically after the delay (PWM_DELAY register on page 23) has elapsed (20 ms to 5s). In case the reverse transition event occurs before the delay has elapsed, the PWM output is released at the same time.  Delayed Transition mode. PWM output is activated by one transition event (e.g., a button press or release) and released after the reverse transition event and the delay (PWM_DELAY register on page 23) has elapsed (20 ms to 5s).  Toggle Flip-Flop mode. PWM output is activated and released alternately only at one of the two transition events (e.g., a button press or release). |

| 5       | 0/1 Link           | Used to select the link between 0/1 logic state of the pin and the PWM/logic level of the output.  O Pin state 0 = output level 0 (0% duty cycle).  Pin state 1 = output PWM signal (selected duty cycle).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|         |                    | 1 Pin state 0 = output PWM signal (selected duty cycle). Pin state 1 = output level 1 (100% duty cycle).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 4       | Apply Delay        | Used to select whether to apply the delay value (for Flash and Delayed Transition modes) to the PWM output '0' or the logic level output '1'. This bit has no effect on Normal and Toggle Flip-Flop modes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3:0     | Duty Cycle[3:0]    | Used to select among 15 duty cycles (duty cycle is defined as the "high" time write to the full PWM signal period). See the following table:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| (contin | nued on next page) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

# 1.6.2 PWM\_MODE\_DC (continued)

| Bit 3 | Bit 2 | Bit 1 | Bit 0 | HEX | DC%      |

|-------|-------|-------|-------|-----|----------|

| 0     | 0     | 0     | 0     | 0x0 | Reserved |

| 0     | 0     | 0     | 1     | 0x1 | 2.5      |

| 0     | 0     | 1     | 0     | 0x2 | 5        |

| 0     | 0     | 1     | 1     | 0x3 | 10       |

| 0     | 1     | 0     | 0     | 0x4 | 15       |

| 0     | 1     | 0     | 1     | 0x5 | 22.5     |

| 0     | 1     | 1     | 0     | 0x6 | 30       |

| 0     | 1     | 1     | 1     | 0x7 | 45       |

| 1     | 0     | 0     | 0     | 0x8 | 55       |

| 1     | 0     | 0     | 1     | 0x9 | 70       |

| 1     | 0     | 1     | 0     | 0xA | 77.5     |

| 1     | 0     | 1     | 1     | 0xB | 85       |

| 1     | 1     | 0     | 0     | 0xC | 90       |

| 1     | 1     | 0     | 1     | 0xD | 95       |

| 1     | 1     | 1     | 0     | 0xE | 97.5     |

| 1     | 1     | 1     | 1     | 0xF | 99.5     |

# 1.6.3 PWM\_DELAY

# **PWM Delay Register**

### **Individual Register Names and Addresses:**

PWM\_DELAY : 1Bh

|             | 7 | 6          | 5 | 4 | 3 | 2 | 1 | 0 |

|-------------|---|------------|---|---|---|---|---|---|

| Access : FD |   | RW:00      |   |   |   |   |   |   |

| Bit Name    |   | Delay[7:0] |   |   |   |   |   |   |

This register sets the delay value for Normal mode ('01') and Single Flash mode ('10') in increments of approximately 20 ms. The minimum value is 0, and the maximum value is 0xFE (~5s). The value 0xFF indicates an indefinite delay.

| Bit | Name       | Description                                                                                                    |

|-----|------------|----------------------------------------------------------------------------------------------------------------|

| 7:0 | Delay[7:0] | Sets the delay value for Normal mode ('01') and Single Flash mode ('10') in increments of approximately 20 ms. |

# 1.7 Output Control Setting Registers

# 1.7.1 **OP\_SEL\_xx**

## **Operation Select Registers**

#### **Individual Register Names and Addresses:**

| OP_SEL_00 : 1Ch | OP_SEL_01 : 21h | OP_SEL_02 : 26h | OP_SEL_03 : 2Bh |

|-----------------|-----------------|-----------------|-----------------|

| OP_SEL_04 : 30h | OP_SEL_10:35h   | OP_SEL_11 : 3Ah | OP_SEL_12 : 3Fh |

| OP_SEL_13 : 44h | OP_SEL_14:49h   |                 |                 |

|             | 7     | 6     | 5         | 4     | 3      | 2     | 1      | 0     |

|-------------|-------|-------|-----------|-------|--------|-------|--------|-------|

| Access : FD | RW:00 | RW:00 | RW:00     | RW:00 | RW:00  | RW:00 | RW:00  | RW:00 |

| Bit Name    | Oper  | N_Op  | Comb[1:0] |       | InvOp2 | Op2   | InvOp1 | Op1   |

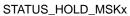

These registers are used to select the operation to be performed on a combination of buttons and/or GPIOs.

The number of pins configurable as this type of output depends on the number of pins used as CapSense inputs and GPIOs. Only the pins enabled as GPIOs in registers 08h and 09h are configured with this set of registers. Configuration for pins already defined as CapSense Input are ignored.

Bit

Name

## 1.7.1 OP\_SEL\_xx (continued)

Description

Operations are performed using the selected input bits (registers 00h-01h) or Port Status Since Last Read bits (registers 02h-03h) from the two ports, inverted according to the Inversion Mask (registers 0Ah-0Bh), ORed or ANDed together, outputting the result (optionally inverted) on the selected output pin.

Having two operands to select allows maximum flexibility for various conditions able to trigger the status of an output pin. If further complexity is needed, the master device can always read the input registers and set the output registers directly.

| operands defined in the next registers, set the bit to '1'.  The bits used for the operations depend on the content of the Op1/2 Port0/1 Mask register (registers 00h-01h), and Port Status Since Last Read (registers 02h-03h).  Op1/2 Port0/1 Mask registers define a mask to select which pins should be used for the o and also have one bit to select whether to use bits from the Input or Port Status register. The always inverted according to the Inversion Mask (registers 04h-08h).  N_Op  This bit determines whether the operation uses one or two operands. A value of '0' uses or and 1 and the result of the operation is the calculated Operand 1 (optionally inverted). A value of values both operands, and the result of the operation is Operand 1 AND/OR/XOR (depe bits 4-5) Operand 2.  These two bits select which operator should be used to combine Operand 1 and Operand 2 at to the table below.  Comb[1:0]  Operand 1 OR Operand 2  10 Operand 1 OR Operand 2  11 Operand 1 XOR Operand 2  OP2  This bit selects which operator should be used to compute Operand 2. A value of '0' calcu OR of the bits selected with the Op2 Port0/1 Mask registers. A value of '1' calculates the Anbits.  InvOp1  Setting this bit to '1' enables the Operand 1 inversion.  Op1  This bit selects which operator should be used to compute Operand 1. A value of '0' calculates the Anbits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Dit | Hamo      | Beschiption                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| (registers 00h-01h), and Port Status Since Last Read (registers 02h-03h).  Op1/2 Port0/1 Mask registers define a mask to select which pins should be used for the o and also have one bit to select whether to use bits from the Input or Port Status register. The always inverted according to the Inversion Mask (registers 0Ah-0Bh).  Inis bit determines whether the operation uses one or two operands. A value of '0' uses or and 1 and the result of the operation is the calculated Operand 1 (optionally inverted). A vawill uses both operands, and the result of the operation is Operand 1 (optionally inverted). A vawill uses both operands, and the result of the operation is Operand 1 AND/OR/XOR (depebits 4-5) Operand 2.  These two bits select which operator should be used to combine Operand 1 and Operand 2 at to the table below.  Comb[1:0] Operand 1 Operand 2  Operand 1 Operand 2  Operand 1 Operand 2  Operand 1 NDO Operand 2  In Operand 1 NDO Operand 2  This bit to '1' enables the Operand 2 inversion.  Population of the bits selected with the Op2 Port0/1 Mask registers. A value of '0' calculates the Albits.  InvOp1 Setting this bit to '1' enables the Operand 1 inversion.  Op1 This bit selects which operator should be used to compute Operand 1. A value of '0' calculates the Albits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 7   | Oper      | This bit enables or disables the operation on the selected output. To enable the operation with the operands defined in the next registers, set the bit to '1'.                                                                                                                                                              |  |  |  |  |

| and also have one bit to select whether to use bits from the Input or Port Status register. The always inverted according to the Inversion Mask (registers 0Ah-0Bh).  N_Op  This bit determines whether the operation uses one or two operands. A value of '0' uses or and 1 and the result of the operation is the calculated Operand 1 (optionally inverted). A va will uses both operands, and the result of the operation is Operand 1 AND/OR/XOR (depe bits 4-5) Operand 2.  These two bits select which operator should be used to combine Operand 1 and Operand 2 at to the table below.  Comb[1:0]  Operation  OO  Reserved  O1  Operand 1 OR Operand 2  10  Operand 1 XOR Operand 2  11  Operand 1 XOR Operand 2  InvOp2  Setting this bit to '1' enables the Operand 2 inversion.  OP2  This bit selects which operator should be used to compute Operand 2. A value of '0' calcu OR of the bits selected with the Op2 Port0/1 Mask registers. A value of '1' calculates the Albits.  InvOp1  Setting this bit to '1' enables the Operand 1 inversion.  Op1  This bit selects which operator should be used to compute Operand 1. A value of '0' calcu OR of the bits selected with the Op1 Port0/1 Mask registers. A value of '1' calculates the Albits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |           | The bits used for the operations depend on the content of the Op1/2 Port0/1 Mask registers, inpu (registers 00h-01h), and Port Status Since Last Read (registers 02h-03h).                                                                                                                                                   |  |  |  |  |

| and 1 and the result of the operation is the calculated Operand 1 (optionally inverted). A value of '0' calculated Operand 1 (optionally inverted). A value of '0' calculated Operand 1 (optionally inverted). A value of '0' calculor of the bits selects which operator should be used to combine Operand 1 and Operand 2 at the table below.    Comb[1:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |           | Op1/2 Port0/1 Mask registers define a mask to select which pins should be used for the operation and also have one bit to select whether to use bits from the Input or Port Status register. The output is always inverted according to the Inversion Mask (registers 0Ah-0Bh).                                              |  |  |  |  |

| to the table below.    Comb[1:0]   Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6   | N_Op      | This bit determines whether the operation uses one or two operands. A value of '0' uses only Operand 1 and the result of the operation is the calculated Operand 1 (optionally inverted). A value of '1' will uses both operands, and the result of the operation is Operand 1 AND/OR/XOR (depending on bits 4-5) Operand 2. |  |  |  |  |

| 3 InvOp2 Setting this bit to '1' enables the Operand 2 inversion.  2 OP2 This bit selects which operator should be used to compute Operand 2. A value of '0' calculor OR of the bits selected with the Op2 Port0/1 Mask registers. A value of '1' calculates the AN bits.  1 InvOp1 Setting this bit to '1' enables the Operand 1 inversion.  Op1 This bit selects which operator should be used to compute Operand 1. A value of '0' calculor OR of the bits selected with operator should be used to compute Operand 1. A value of '0' calculor OR of the bits selected with the Op1 Port0/1 Mask registers. A value of '1' calculates the AN OR of the bits selected with the Op1 Port0/1 Mask registers. A value of '1' calculates the AN OR of the bits selected with the Op1 Port0/1 Mask registers. A value of '1' calculates the AN OR of the bits selected with the Op1 Port0/1 Mask registers. A value of '1' calculates the AN OR of the bits selected with the Op1 Port0/1 Mask registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5:4 | Comb[1:0] | These two bits select which operator should be used to combine Operand 1 and Operand 2 according to the table below.                                                                                                                                                                                                         |  |  |  |  |

| Operand 1 OR Operand 2  10 Operand 1 AND Operand 2  11 Operand 1 XOR Operand 2  11 Operand 1 XOR Operand 2  12 OP2 Setting this bit to '1' enables the Operand 2 inversion.  This bit selects which operator should be used to compute Operand 2. A value of '0' calculor OR of the bits selected with the Op2 Port0/1 Mask registers. A value of '1' calculates the AND bits.  InvOp1 Setting this bit to '1' enables the Operand 1 inversion.  Op1 This bit selects which operator should be used to compute Operand 1. A value of '0' calculor OR of the bits selected with the Op1 Port0/1 Mask registers. A value of '1' calculates the AND OP1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |           | Comb[1:0] Operation                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| InvOp2  Setting this bit to '1' enables the Operand 2 inversion.  This bit selects which operator should be used to compute Operand 2. A value of '0' calculor OR of the bits selected with the Op2 Port0/1 Mask registers. A value of '1' calculates the AN bits.  InvOp1  Setting this bit to '1' enables the Operand 1 inversion.  This bit selects which operator should be used to compute Operand 1. A value of '0' calculor OP1  This bit selects which operator should be used to compute Operand 1. A value of '0' calculor OP1  Op1  This bit selects which operator should be used to compute Operand 1. A value of '1' calculates the AN oP1  OP1  This bit selects which operator should be used to compute Operand 1. A value of '1' calculates the AN oP1  OP3  This bit selects which operator should be used to compute Operand 1. A value of '1' calculates the AN oP1  OP3  This bit selects which operator should be used to compute Operand 1. A value of '1' calculates the AN oP1  OP3  This bit selects which operator should be used to compute Operand 1. A value of '1' calculates the AN oP1  OP3  This bit selects which operator should be used to compute Operand 1. A value of '1' calculates the AN oP1  OP3  This bit selects which operator should be used to compute Operand 1. A value of '1' calculates the AN oP1  OP3  This bit selects which operator should be used to compute Operand 1. A value of '1' calculates the AN oP1  OP3  This bit selects which operator should be used to compute Operand 1. A value of '1' calculates the AN oP1  This bit selects which operator should be used to compute Operand 1. A value of '1' calculates the AN oP1  This bit selects which operator should be used to compute Operand 1. A value of '1' calculates the AN oP1  This bit selects which operator should be used to compute Operand 1. A value of '1' calculates the AN oP1  This bit selects which operator should be used to compute Operand 1. A value of '1' calculates the AN oP1  This bit selects which operator should be used to compute Operand 1. A value of '1' calc |     |           | 00 Reserved                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| InvOp2 Setting this bit to '1' enables the Operand 2 inversion.  OP2 This bit selects which operator should be used to compute Operand 2. A value of '0' calculor OR of the bits selected with the Op2 Port0/1 Mask registers. A value of '1' calculates the AN bits.  InvOp1 Setting this bit to '1' enables the Operand 1 inversion.  Op1 This bit selects which operator should be used to compute Operand 1. A value of '0' calculor OR of the bits selected with the Op1 Port0/1 Mask registers. A value of '1' calculates the AN operator should be used to compute Operand 1. A value of '0' calculor OR of the bits selected with the Op1 Port0/1 Mask registers. A value of '1' calculates the AN operator should be used to compute Operand 1. A value of '0' calculor OR of the bits selected with the Op1 Port0/1 Mask registers. A value of '1' calculates the AN operator should be used to compute Operand 1. A value of '0' calculor OR of the bits selected with the Op1 Port0/1 Mask registers. A value of '1' calculates the AN operator should be used to compute Operand 1. A value of '0' calculor OR of the bits selected with the Op1 Port0/1 Mask registers. A value of '1' calculates the AN operator should be used to compute Operand 1. A value of '0' calculor OR of the bits selected with the Op1 Port0/1 Mask registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |           | 01 Operand 1 OR Operand 2                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| 3 InvOp2 Setting this bit to '1' enables the Operand 2 inversion.  2 OP2 This bit selects which operator should be used to compute Operand 2. A value of '0' calculor OR of the bits selected with the Op2 Port0/1 Mask registers. A value of '1' calculates the AN bits.  1 InvOp1 Setting this bit to '1' enables the Operand 1 inversion.  Op1 This bit selects which operator should be used to compute Operand 1. A value of '0' calculor OR of the bits selected with the Op1 Port0/1 Mask registers. A value of '1' calculates the AN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |           | 10 Operand 1 AND Operand 2                                                                                                                                                                                                                                                                                                   |  |  |  |  |