# **IQS7222B DATASHEET**

20 Channel Mutual / 8 Channel Self- Capacitive Touch and Proximity Controller with I<sup>2</sup>C communications interface, configurable GPIOs and low power options

#### 1 Device Overview

The IQS7222B ProxFusion<sup>®</sup> IC is a sensor fusion device for various multi-button applications. The sensor is fully I<sup>2</sup>C compatible and on-chip calculations enable the IC to respond effectively even in lowest power modes.

#### 1.1 Main Features

- > Highly flexible ProxFusion® device

- > 9 (QFN) / 8 (WLCSP) external sensor pad connections

- > Configure up to 20 Mutual capacitive buttons,18 mutual capacitance buttons with proximity wakeup function or up to 8 self-capacitance buttons<sup>i</sup>

- > Built-in basic functions:

- Automatic tuning

- Noise filtering

- Debounce & hysteresis

- Dual direction trigger indication

- > Design simplicity

- PC Software for debugging and obtaining optimal settings and performance

- One-time programmable settings for custom power-on IC configuration

- Auto-run from programmed settings for simplified integration

- > Automated system power modes for optimal response vs consumption

- > I<sup>2</sup>C communication interface with IRQ/RDY(up to fast plus -1MHz)

- > Event and streaming modes

- > Customizable user interface due to programmable memory

- > Small packages

- WLCSP18 (1.62 x 1.62 x 0.5 mm) interleaved 0.4mm x 0.6mm ball pitch

- QFN20 (3 x 3 x 0.5 mm) 0.4mm pitch

# 1.2 Applications

- > Remote Control User Interface

- > Home Automation Device User Interface

- > Wireless Speaker Controls

WLCSP18 & QFN20 package Representation only

<sup>&</sup>lt;sup>i</sup>WLCSP18 package has 1 less external pad connection and the maximum amount of buttons that can be configured is 18 buttons or 16 buttons with a wake-up function

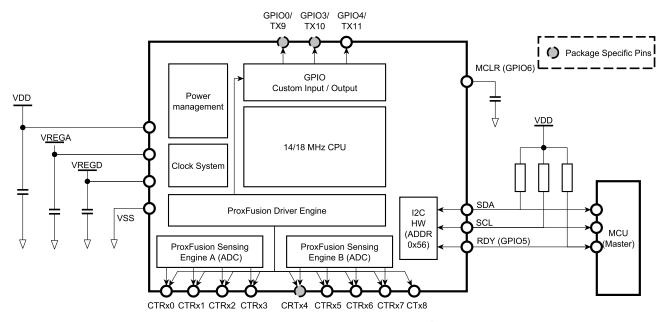

## 1.3 Block Diagram

Figure 1.1: Functional Block Diagrami

## **Contents**

| 1 | Devic             | e Overview                                     | 1   |

|---|-------------------|------------------------------------------------|-----|

|   | 1.1<br>1.2<br>1.3 | Main Features                                  | 1 2 |

| 2 | Hardy             | vare Connection                                | 6   |

|   | 2.1               | WLCSP18 Pin Diagrams                           | 6   |

|   | 2.2               | S .                                            | 6   |

|   | 2.3               |                                                | 7   |

|   | 2.4               |                                                | 8   |

|   | 2.5               |                                                | 9   |

| 3 | Electr            | ical Characteristics                           | 1   |

|   | 3.1               |                                                | 1   |

|   | 3.2               | · · · · · · · · · · · · · · · · · · ·          | 1   |

|   | 3.3               |                                                | 2   |

|   | 3.4               | · · · · · · · · · · · · · · · · · · ·          | 2   |

| 4 |                   | ·                                              |     |

| 4 | 4.1               | <b>5</b> • • • • • • • • • • • • • • • • • • • | 3   |

|   | 4.1               |                                                | 3   |

|   |                   |                                                |     |

|   | 4.3               | 9                                              | 3   |

|   | 4.4               | 9                                              | 4   |

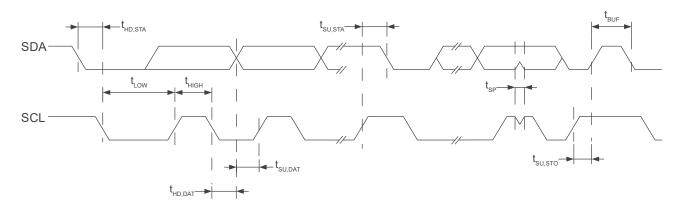

|   | 4.5               | I <sup>2</sup> C Characteristics               | 4   |

| 5 | ProxF             |                                                | 5   |

|   | 5.1               | Capacitive Channels                            | 5   |

|   | 5.2               | Count Value                                    | 5   |

|   |                   | 5.2.1 Max Count                                | 5   |

|   | 5.3               | Reference Value/Long-Term Average (LTA)        | 5   |

|   |                   | 5.3.1 Reseed                                   | 5   |

|   | 5.4               | Automatic Tuning Implementation (ATI)          | 5   |

|   | 5.5               | Automatic Re-ATI                               | 5   |

|   |                   | 5.5.1 Description                              | 5   |

|   |                   |                                                | 6   |

|   |                   | 5.5.3 ATI Error                                | 6   |

| 6 | Sensi             | ng Modes                                       | 7   |

|   | 6.1               | <b>5</b> • • • • • • • • • • • • • • • • • • • | 7   |

|   | 6.2               | Count Filter                                   | 7   |

|   |                   | 6.2.1 IIR Filter                               | 7   |

| 7 | Hardv             | vare Settings                                  | 8   |

|   | 7.1               | Charge Transfer Frequency                      | 8   |

|   | 7.2               | Reset                                          | 8   |

|   |                   | 7.2.1 Reset Indication                         | 8   |

|   |                   | 7.2.2 Software Reset                           | 8   |

| 8 | Additi            | onal Features                                  | 9   |

|   | 8.1               |                                                | 9   |

|   |                   | •                                              |     |

|    | 8.2                                                                                            | Automated Start-up                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 19                                                                                       |

|----|------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

|    | 8.4                                                                                            | RF Immunity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 19                                                                                       |

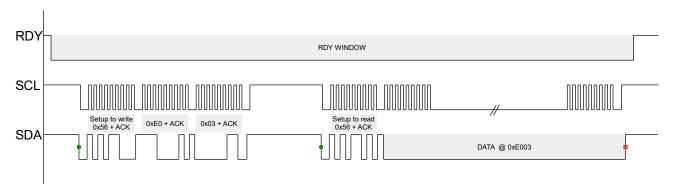

| 9  | I <sup>2</sup> C In                                                                            | terface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 20                                                                                       |

|    | 9.1                                                                                            | I <sup>2</sup> C Module Specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 20                                                                                       |

|    | 9.2                                                                                            | I <sup>2</sup> C Address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 20                                                                                       |

|    | 9.3                                                                                            | I <sup>3</sup> C Compatibility                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 20                                                                                       |

|    | 9.4                                                                                            | Memory Map Addressing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 20                                                                                       |

|    |                                                                                                | 9.4.1 8-bit Address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 20                                                                                       |

|    |                                                                                                | 9.4.2 Extended 16-bit Address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 20                                                                                       |

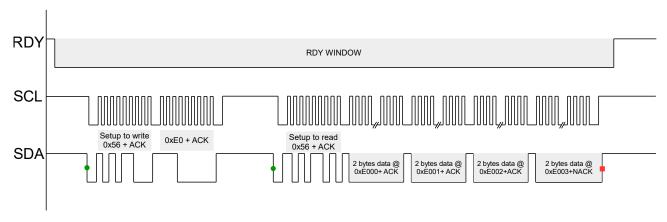

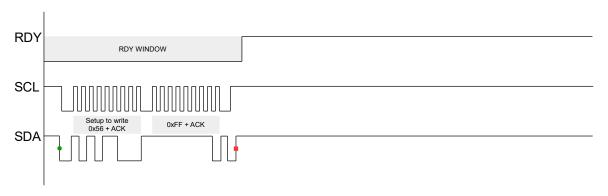

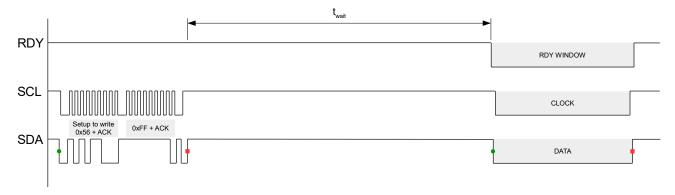

|    | 9.5                                                                                            | Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 21                                                                                       |

|    | 9.6                                                                                            | $I^2C$ Timeout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 22                                                                                       |

|    | 9.7                                                                                            | Terminate Communication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 22                                                                                       |

|    | 9.8                                                                                            | RDY/IRQ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 22                                                                                       |

|    | 9.9                                                                                            | Invalid Communications Return                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 22                                                                                       |

|    | 9.10                                                                                           | I <sup>2</sup> C Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 22                                                                                       |

|    | 9.10                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                          |

|    |                                                                                                | 9.10.1 I <sup>2</sup> C Streaming                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 22                                                                                       |

|    |                                                                                                | 9.10.2 I <sup>2</sup> C Event Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 23                                                                                       |

|    |                                                                                                | 9.10.3 I <sup>2</sup> C Stream in Touch Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 23                                                                                       |

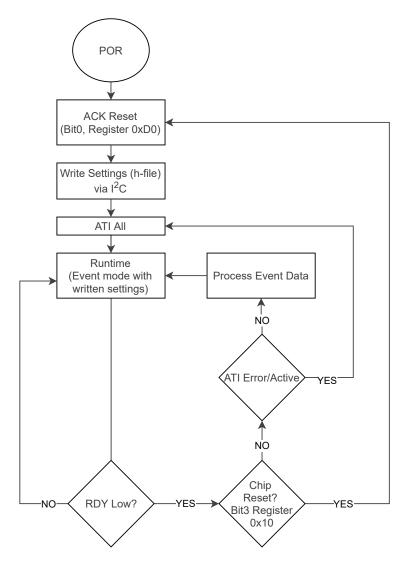

|    | 9.11                                                                                           | Event Mode Communication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 23                                                                                       |

|    |                                                                                                | 9.11.1 Events                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 23                                                                                       |

|    |                                                                                                | 9.11.2 Force Communication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 23                                                                                       |

|    | 9.12                                                                                           | Program Flow Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 25                                                                                       |

|    |                                                                                                | emory Map - Register Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 26                                                                                       |

| 44 | Implo                                                                                          | mentation and Layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 04                                                                                       |

| 11 |                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 31                                                                                       |

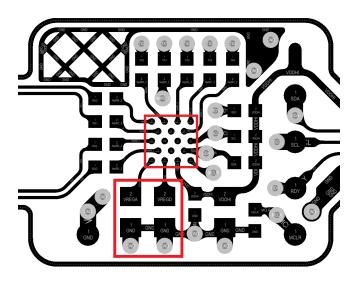

| "  |                                                                                                | Layout Fundamentals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 31                                                                                       |

| '' |                                                                                                | Layout Fundamentals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 31<br>31                                                                                 |

| '' |                                                                                                | Layout Fundamentals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 31                                                                                       |

| '' |                                                                                                | Layout Fundamentals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 31<br>31                                                                                 |

|    | 11.1                                                                                           | Layout Fundamentals  11.1.1 Power Supply Decoupling  11.1.2 VREG Capacitors  11.1.3 WLCSP Light Sensitivity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 31<br>31<br>31<br>32                                                                     |

|    | 11.1 Order                                                                                     | Layout Fundamentals  11.1.1 Power Supply Decoupling  11.1.2 VREG Capacitors  11.1.3 WLCSP Light Sensitivity  ing Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 31<br>31<br>31<br>32<br>33                                                               |

|    | 11.1<br>Order<br>12.1                                                                          | Layout Fundamentals  11.1.1 Power Supply Decoupling  11.1.2 VREG Capacitors  11.1.3 WLCSP Light Sensitivity  ing Information  Ordering Code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 31<br>31<br>32<br>33<br>33                                                               |

|    | 11.1 Order                                                                                     | Layout Fundamentals  11.1.1 Power Supply Decoupling  11.1.2 VREG Capacitors  11.1.3 WLCSP Light Sensitivity  ing Information  Ordering Code  Top Marking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 31<br>31<br>32<br>33<br>33<br>33                                                         |

|    | 11.1<br>Order<br>12.1                                                                          | Layout Fundamentals  11.1.1 Power Supply Decoupling  11.1.2 VREG Capacitors  11.1.3 WLCSP Light Sensitivity  ing Information  Ordering Code  Top Marking  12.2.1 WLCSP18 Package (IQS7222BzzzCSR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 31<br>31<br>32<br>33<br>33<br>33<br>33                                                   |

|    | 11.1<br>Order<br>12.1                                                                          | Layout Fundamentals  11.1.1 Power Supply Decoupling  11.1.2 VREG Capacitors  11.1.3 WLCSP Light Sensitivity  ing Information Ordering Code Top Marking  12.2.1 WLCSP18 Package (IQS7222BzzzCSR)  12.2.2 QFN20 Package Marking Option 1 (IQS7222BzzzQFR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 31<br>31<br>32<br>33<br>33<br>33<br>33                                                   |

|    | 11.1<br>Order<br>12.1                                                                          | Layout Fundamentals  11.1.1 Power Supply Decoupling  11.1.2 VREG Capacitors  11.1.3 WLCSP Light Sensitivity  ing Information  Ordering Code  Top Marking  12.2.1 WLCSP18 Package (IQS7222BzzzCSR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 31<br>31<br>32<br>33<br>33<br>33<br>33                                                   |

| 12 | Order<br>12.1<br>12.2                                                                          | Layout Fundamentals  11.1.1 Power Supply Decoupling  11.1.2 VREG Capacitors  11.1.3 WLCSP Light Sensitivity  ing Information Ordering Code Top Marking  12.2.1 WLCSP18 Package (IQS7222BzzzCSR)  12.2.2 QFN20 Package Marking Option 1 (IQS7222BzzzQFR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 31<br>31<br>32<br>33<br>33<br>33<br>33                                                   |

| 12 | Order<br>12.1<br>12.2                                                                          | Layout Fundamentals  11.1.1 Power Supply Decoupling  11.1.2 VREG Capacitors  11.1.3 WLCSP Light Sensitivity  ing Information  Ordering Code  Top Marking  12.2.1 WLCSP18 Package (IQS7222BzzzCSR)  12.2.2 QFN20 Package Marking Option 1 (IQS7222BzzzQFR)  12.2.3 QFN20 Package Marking Option 2 (IQS7222BzzzQNR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 31<br>31<br>31<br>32<br>33<br>33<br>33<br>34                                             |

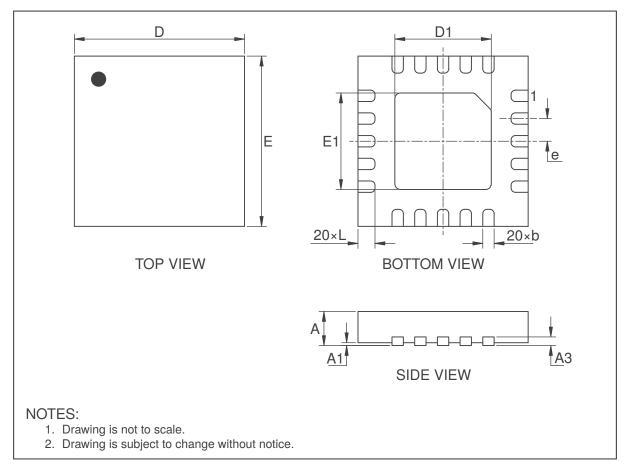

| 12 | Order<br>12.1<br>12.2<br>Packa                                                                 | Layout Fundamentals  11.1.1 Power Supply Decoupling  11.1.2 VREG Capacitors  11.1.3 WLCSP Light Sensitivity  ing Information Ordering Code Top Marking  12.2.1 WLCSP18 Package (IQS7222BzzzCSR)  12.2.2 QFN20 Package Marking Option 1 (IQS7222BzzzQFR)  12.2.3 QFN20 Package Marking Option 2 (IQS7222BzzzQNR)  ige Specification Package Outline Description – QFN20 (QFR)                                                                                                                                                                                                                                                                                                                                                                                                                                | 31<br>31<br>31<br>32<br>33<br>33<br>33<br>34<br>35                                       |

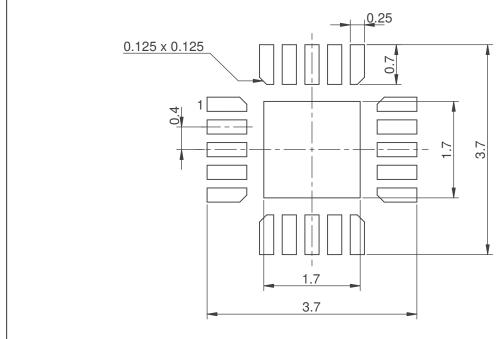

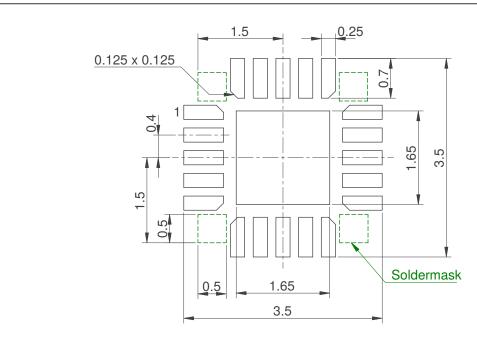

| 12 | Order<br>12.1<br>12.2<br>Packa<br>13.1<br>13.2                                                 | Layout Fundamentals  11.1.1 Power Supply Decoupling  11.1.2 VREG Capacitors  11.1.3 WLCSP Light Sensitivity  ing Information  Ordering Code  Top Marking  12.2.1 WLCSP18 Package (IQS7222BzzzCSR)  12.2.2 QFN20 Package Marking Option 1 (IQS7222BzzzQFR)  12.2.3 QFN20 Package Marking Option 2 (IQS7222BzzzQNR)  ige Specification  Package Outline Description – QFN20 (QFR)  Recommended PCB Footprint – QFN20 (QFR)                                                                                                                                                                                                                                                                                                                                                                                    | 31<br>31<br>31<br>32<br>33<br>33<br>33<br>33<br>34<br>35<br>35<br>36                     |

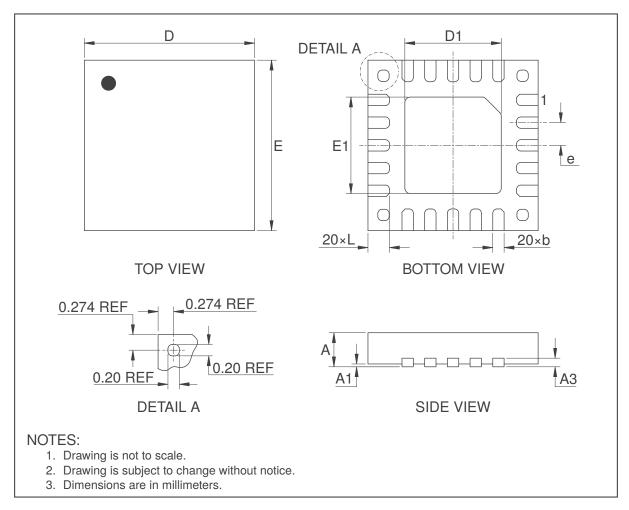

| 12 | Order<br>12.1<br>12.2<br>Packa<br>13.1<br>13.2<br>13.3                                         | Layout Fundamentals  11.1.1 Power Supply Decoupling  11.1.2 VREG Capacitors  11.1.3 WLCSP Light Sensitivity  ing Information Ordering Code Top Marking  12.2.1 WLCSP18 Package (IQS7222BzzzCSR)  12.2.2 QFN20 Package Marking Option 1 (IQS7222BzzzQFR)  12.2.3 QFN20 Package Marking Option 2 (IQS7222BzzzQNR)  ige Specification Package Outline Description – QFN20 (QFR) Recommended PCB Footprint – QFN20 (QFR) Package Outline Description – QFN20 (QNR)                                                                                                                                                                                                                                                                                                                                              | 311<br>311<br>313<br>323<br>333<br>333<br>344<br>35<br>36<br>37                          |

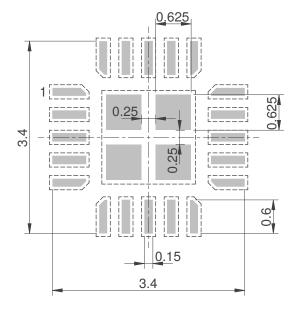

| 12 | Order<br>12.1<br>12.2<br>Packa<br>13.1<br>13.2<br>13.3<br>13.4                                 | Layout Fundamentals  11.1.1 Power Supply Decoupling  11.1.2 VREG Capacitors  11.1.3 WLCSP Light Sensitivity  ing Information  Ordering Code  Top Marking  12.2.1 WLCSP18 Package (IQS7222BzzzCSR)  12.2.2 QFN20 Package Marking Option 1 (IQS7222BzzzQFR)  12.2.3 QFN20 Package Marking Option 2 (IQS7222BzzzQNR)  12.2.4 QFN20 Package Marking Option 2 (IQS7222BzzzQNR)  12.2.5 QFN20 Package Marking Option 2 (IQS7222BzzzQNR)  12.2.6 QFN20 Package Marking Option 2 (IQS7222BzzzQNR)  12.2.7 QFN20 Package Marking Option 2 (IQS7222BzzzQNR)  12.2.8 QFN20 Package Marking Option 2 (IQS7222BzzzQNR)  12.2.9 QFN20 Package Marking Option 2 (IQS7222BzzzQNR)  12.2.1 QFN20 Package Outline Description — QFN20 (QFR)  Recommended PCB Footprint — QFN20 (QNR)  Recommended PCB Footprint — QFN20 (QNR) | 311<br>311<br>313<br>323<br>333<br>333<br>334<br>345<br>355<br>366<br>377<br>388         |

| 12 | Order<br>12.1<br>12.2<br>Packa<br>13.1<br>13.2<br>13.3<br>13.4<br>13.5                         | Layout Fundamentals  11.1.1 Power Supply Decoupling  11.1.2 VREG Capacitors  11.1.3 WLCSP Light Sensitivity  ing Information Ordering Code Top Marking  12.2.1 WLCSP18 Package (IQS7222BzzzCSR)  12.2.2 QFN20 Package Marking Option 1 (IQS7222BzzzQFR)  12.2.3 QFN20 Package Marking Option 2 (IQS7222BzzzQNR)  inge Specification Package Outline Description – QFN20 (QFR) Recommended PCB Footprint – QFN20 (QFR) Package Outline Description – QFN20 (QNR) Recommended PCB Footprint – QFN20 (QNR) Recommended PCB Footprint – QFN20 (QNR) Package Outline Description – QFN20 (QNR) Package Outline Description – QFN20 (QNR)                                                                                                                                                                         | 311<br>311<br>313<br>333<br>333<br>333<br>344<br>353<br>363<br>373<br>383<br>393         |

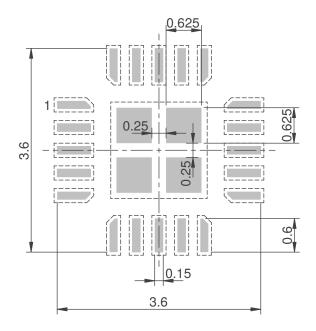

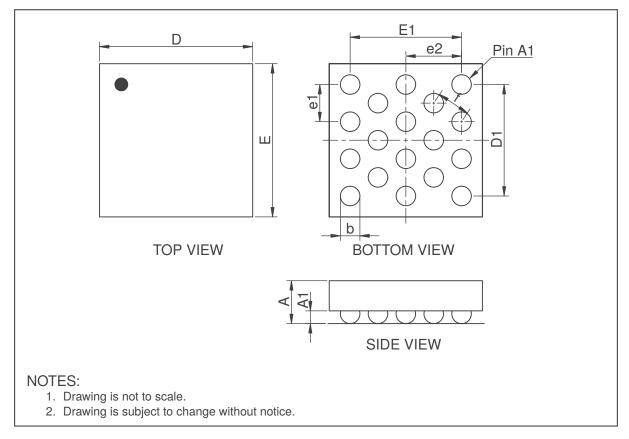

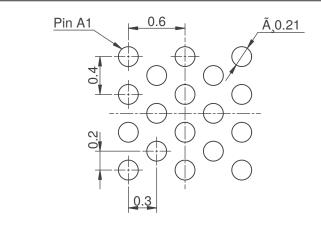

| 12 | Order<br>12.1<br>12.2<br>Packa<br>13.1<br>13.2<br>13.3<br>13.4<br>13.5<br>13.6                 | Layout Fundamentals  11.1.1 Power Supply Decoupling  11.1.2 VREG Capacitors  11.1.3 WLCSP Light Sensitivity  ing Information Ordering Code Top Marking  12.2.1 WLCSP18 Package (IQS7222BzzzCSR)  12.2.2 QFN20 Package Marking Option 1 (IQS7222BzzzQFR)  12.2.3 QFN20 Package Marking Option 2 (IQS7222BzzzQNR)  ge Specification Package Outline Description – QFN20 (QFR) Recommended PCB Footprint – QFN20 (QFR) Package Outline Description – QFN20 (QNR) Recommended PCB Footprint – QFN20 (QNR) Recommended PCB Footprint – QFN20 (QNR) Package Outline Description – QFN20 (QNR) Recommended PCB Footprint – QFN20 (QNR) Package Outline Description – WLCSP18 Recommended PCB Footprint – WLCSP18                                                                                                   | 311<br>311<br>313<br>333<br>333<br>333<br>344<br>355<br>366<br>377<br>388<br>399<br>400  |

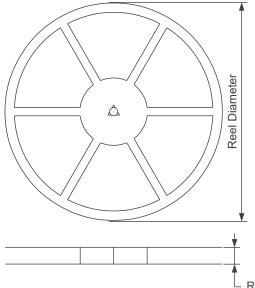

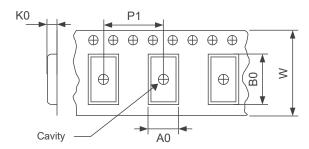

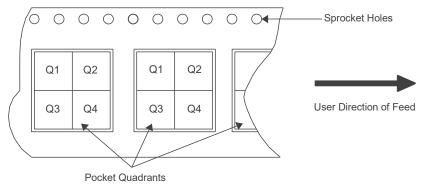

| 12 | Order<br>12.1<br>12.2<br>Packa<br>13.1<br>13.2<br>13.3<br>13.4<br>13.5<br>13.6<br>13.7         | Layout Fundamentals  11.1.1 Power Supply Decoupling  11.1.2 VREG Capacitors  11.1.3 WLCSP Light Sensitivity  ing Information Ordering Code Top Marking  12.2.1 WLCSP18 Package (IQS7222BzzzCSR)  12.2.2 QFN20 Package Marking Option 1 (IQS7222BzzzQFR)  12.2.3 QFN20 Package Marking Option 2 (IQS7222BzzzQNR)  ge Specification Package Outline Description – QFN20 (QFR) Recommended PCB Footprint – QFN20 (QNR) Package Outline Description – QFN20 (QNR) Recommended PCB Footprint – QFN20 (QNR) Recommended PCB Footprint – QFN20 (QNR) Package Outline Description – WLCSP18 Recommended PCB Footprint – WLCSP18 Recommended PCB Footprint – WLCSP18 Tape and Reel Specifications                                                                                                                    | 311<br>311<br>313<br>323<br>333<br>333<br>333<br>344<br>353<br>364<br>373<br>384<br>4041 |

| 12 | Order<br>12.1<br>12.2<br>Packa<br>13.1<br>13.2<br>13.3<br>13.4<br>13.5<br>13.6<br>13.7<br>13.8 | Layout Fundamentals  11.1.1 Power Supply Decoupling  11.1.2 VREG Capacitors  11.1.3 WLCSP Light Sensitivity  ing Information  Ordering Code  Top Marking  12.2.1 WLCSP18 Package (IQS7222BzzzCSR)  12.2.2 QFN20 Package Marking Option 1 (IQS7222BzzzQFR)  12.2.3 QFN20 Package Marking Option 2 (IQS7222BzzzQNR)  ge Specification  Package Outline Description – QFN20 (QFR)  Recommended PCB Footprint – QFN20 (QNR)  Recommended PCB Footprint – QFN20 (QNR)  Recommended PCB Footprint – QFN20 (QNR)  Recommended PCB Footprint – WLCSP18  Recommended PCB Footprint – WLCSP18  Recommended PCB Footprint – WLCSP18  Tape and Reel Specifications  Moisture Sensitivity Levels                                                                                                                         | 311<br>311<br>313<br>333<br>333<br>333<br>343<br>353<br>363<br>373<br>383<br>404<br>4142 |

| 12 | Order<br>12.1<br>12.2<br>Packa<br>13.1<br>13.2<br>13.3<br>13.4<br>13.5<br>13.6<br>13.7         | Layout Fundamentals  11.1.1 Power Supply Decoupling  11.1.2 VREG Capacitors  11.1.3 WLCSP Light Sensitivity  ing Information Ordering Code Top Marking  12.2.1 WLCSP18 Package (IQS7222BzzzCSR)  12.2.2 QFN20 Package Marking Option 1 (IQS7222BzzzQFR)  12.2.3 QFN20 Package Marking Option 2 (IQS7222BzzzQNR)  ge Specification Package Outline Description – QFN20 (QFR) Recommended PCB Footprint – QFN20 (QNR) Package Outline Description – QFN20 (QNR) Recommended PCB Footprint – QFN20 (QNR) Recommended PCB Footprint – QFN20 (QNR) Package Outline Description – WLCSP18 Recommended PCB Footprint – WLCSP18 Recommended PCB Footprint – WLCSP18 Tape and Reel Specifications                                                                                                                    | 311<br>311<br>313<br>323<br>333<br>333<br>333<br>344<br>353<br>364<br>373<br>384<br>4041 |

| В | Revision History | 52 |

|---|------------------|----|

| С | Known Issues     | 53 |

## 2 Hardware Connection

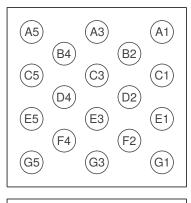

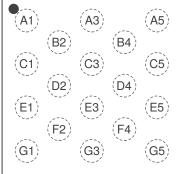

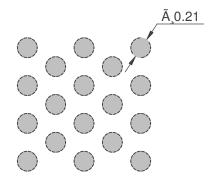

## 2.1 WLCSP18 Pin Diagrams

Table 2.1: 18-pin WLCSP18 Package

Ball-side View

Top-side View

| Pin no. | Signal                              |

|---------|-------------------------------------|

| A1      | CTx9/GPIO0/CTx10/GPIO3 <sup>i</sup> |

| A3      | SCL/GPIO2                           |

| A5      | MCLR/GPIO6                          |

| B2      | CTx11/GPIO4                         |

| B4      | SDA/GPIO1                           |

| C1      | CTx8                                |

| C3      | RDY/GPIO5                           |

| C5      | VDD                                 |

| D2      | CRx2/CTx2                           |

| D4      | VSS                                 |

| E1      | CRx6/CTx6                           |

| E3      | CRx1/CTx1                           |

| E5      | VREGD                               |

| F2      | CRx5/CTx5                           |

| F4      | CRx0/CTx0                           |

| G1      | CRx7/CTx7                           |

| G3      | CRx3/CTx3                           |

| G5      | VREGA                               |

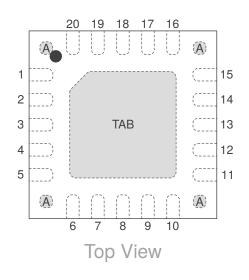

# 2.2 QFN20 Pin Diagram

Table 2.2: 20-pin QFN Package (Top View)

| Signal name | Pin no.                                                               | Signal name                                                                                      |

|-------------|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| VDD         | 11                                                                    | CRx6/CTx6                                                                                        |

| VREGD       | 12                                                                    | CRx7/CTx7                                                                                        |

| VSS         | 13                                                                    | CTx8                                                                                             |

| VREGA       | 14                                                                    | CTx9/GPIO0                                                                                       |

| CRx0/CTx0   | 15                                                                    | CTx10/GPIO3                                                                                      |

| CRx1/CTx1   | 16                                                                    | CTx11/GPIO4                                                                                      |

| CRx2/CTx2   | 17                                                                    | RDY/GPIO5                                                                                        |

| CRx3/CTx3   | 18                                                                    | SCL/GPIO2                                                                                        |

| CRx4/CTx4   | 19                                                                    | SDA/GPIO1                                                                                        |

| CRx5/CTx5   | 20                                                                    | MCLR/GPIO6                                                                                       |

|             | VDD VREGD VSS VREGA CRx0/CTx0 CRx1/CTx1 CRx2/CTx2 CRx3/CTx3 CRx4/CTx4 | VDD 11 VREGD 12 VSS 13 VREGA 14 CRx0/CTx0 15 CRx1/CTx1 16 CRx2/CTx2 17 CRx3/CTx3 18 CRx4/CTx4 19 |

| Area name         | Signal name            |

|-------------------|------------------------|

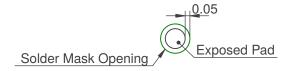

| TAB <sup>ii</sup> | Thermal pad (floating) |

| A <sup>iii</sup>  | Thermal pad (floating) |

<sup>&</sup>lt;sup>i</sup>Please note that CTx9/GPIO0 and CTx10/GPIO3 are connected together in the WLCSP18 package.

<sup>&</sup>lt;sup>ii</sup>It is recommended to connect the thermal pad (TAB) to VSS.

iii Electrically connected to TAB. These exposed pads are only present on -QNR order codes.

## 2.3 Pin Attributes

Table 2.3: Pin Attributes

| Pin no.       |    | Signal name | Signal type  | Buffer type | Power source |

|---------------|----|-------------|--------------|-------------|--------------|

| WLCSP18 QFN20 |    |             |              |             |              |

| C5            | 1  | VDD         | Power        | Power       | N/A          |

| E5            | 2  | VREGD       | Power        | Power       | N/A          |

| D4            | 3  | VSS         | Power        | Power       | N/A          |

| G5            | 4  | VREGA       | Power        | Power       | N/A          |

| F4            | 5  | CRx0/CTx0   | Analog       |             | VREGA        |

| E3            | 6  | CRx1/CTx1   | Analog       |             | VREGA        |

| D2            | 7  | CRx2/CTx2   | Analog       |             | VREGA        |

| G3            | 8  | CRx3/CTx3   | Analog       |             | VREGA        |

| -             | 9  | CRx4/CTx4   | Analog       |             | VREGA        |

| F2            | 10 | CRx5/CTx5   | Analog       |             | VREGA        |

| E1            | 11 | CRx6/CTx6   | Analog       |             | VREGA        |

| G1            | 12 | CRx7/CTx7   | Analog       |             | VREGA        |

| C1            | 13 | CTx8        | Analog       |             | VREGA        |

| A1            | 14 | CTx9/GPIO0  | Prox/Digital |             | VREGA/VDD    |

| B4            | 19 | SDA/GPIO1   | Digital      |             | VDD          |

| A3            | 18 | SCL/GPIO2   | Digital      |             | VDD          |

| A1            | 15 | CTx10/GPIO3 | Prox/Digital |             | VREGA/VDD    |

| B2            | 16 | CTx11/GPIO4 | Prox/Digital |             | VREGA/VDD    |

| C3            | 17 | RDY/GPIO5   | Digital      |             | VDD          |

| A5            | 20 | MCLR/GPIO6  | Digital      |             | VDD          |

# 2.4 Signal Descriptions

Table 2.4: Signal Descriptions

| Function                | Signal name | Pin no.    |       | Pin type <sup>iv</sup> | Description                                                                                                            |  |

|-------------------------|-------------|------------|-------|------------------------|------------------------------------------------------------------------------------------------------------------------|--|

|                         |             | WLCSP18    | QFN20 |                        |                                                                                                                        |  |

|                         | CRx0/CTx0   | F4         | 5     | Ю                      |                                                                                                                        |  |

|                         | CRx1/CTx1   | E3         | 6     | Ю                      |                                                                                                                        |  |

|                         | CRx2/CTx2   | D2         | 7     | IO                     |                                                                                                                        |  |

|                         | CRx3/CTx3   | G3         | 8     | IO                     | ProxFusion <sup>®</sup> channel                                                                                        |  |

|                         | CRx4/CTx4   | -          | 9     | IO                     | Troxi asion chamier                                                                                                    |  |

| ProxFusion <sup>®</sup> | CRx5/CTx5   | F2         | 10    | Ю                      |                                                                                                                        |  |

| T TOXT GOIOTT           | CRx6/CTx6   | E1         | 11    | Ю                      |                                                                                                                        |  |

|                         | CRx7/CTx7   | G1         | 12    | Ю                      |                                                                                                                        |  |

|                         | CTx8        | C1         | 13    | 0                      | CTx8 pad                                                                                                               |  |

|                         | CTx9/GPIO0  | A1         | 14    | Ю                      | CTx9/GPIO0 pad                                                                                                         |  |

|                         | CTx10/GPIO3 | A1         | 15    | Ю                      | CTx10/GPIO3 pad                                                                                                        |  |

|                         | CTx11/GPIO4 | B2         | 16    | Ю                      | CTx11/GPIO4 pad                                                                                                        |  |

|                         | RDY/GPIO5   | C3         | 17    | 0                      | RDY/GPIO5 pad                                                                                                          |  |

| GPIO                    | MCLR/GPIO6  | <b>A</b> 5 | 20    | Ю                      | Active pull-up, 200k resistor to VDD.  Pulled low during POR, and MCLR function enabled by default. VPP input for OTP. |  |

| I <sup>2</sup> C        | SDA/GPIO1   | B4         | 19    | IO                     | I <sup>2</sup> C data                                                                                                  |  |

| 10                      | SCL/GPIO2   | А3         | 18    | IO                     | I <sup>2</sup> C clock                                                                                                 |  |

|                         | VDD         | C5         | 1     | Р                      | Power supply input voltage                                                                                             |  |

| Power                   | VREGD       | E5         | 2     | Р                      | Internal regulated supply output for digital domain                                                                    |  |

| rower                   | VSS         | D4         | 3     | Р                      | Analog/digital ground                                                                                                  |  |

|                         | VREGA       | G5         | 4     | Р                      | Internal regulated supply output for analog domain                                                                     |  |

ivPin Types: I = Input, O = Output, IO = Input or Output, P = Power.

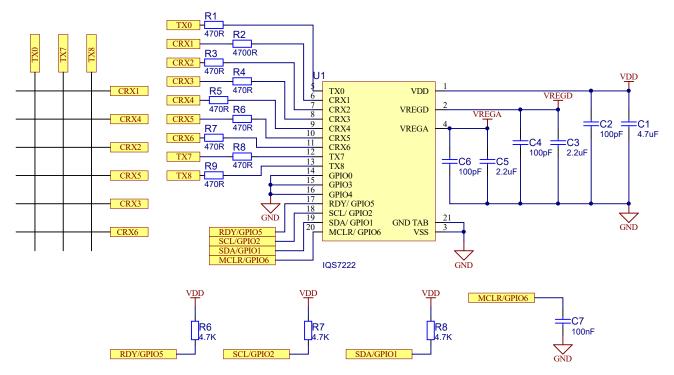

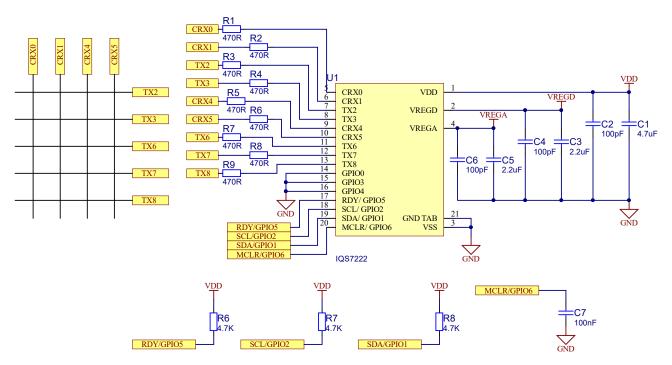

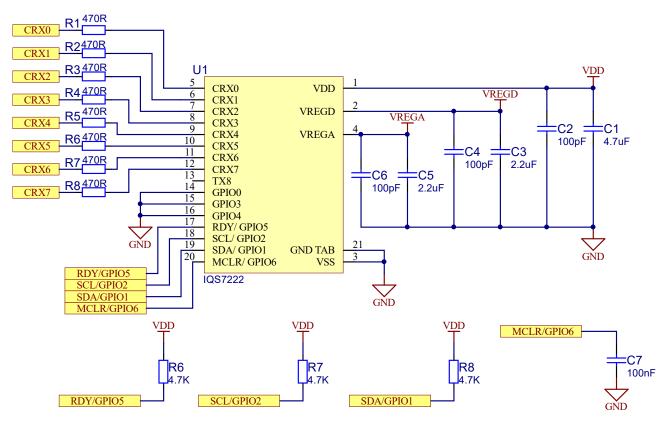

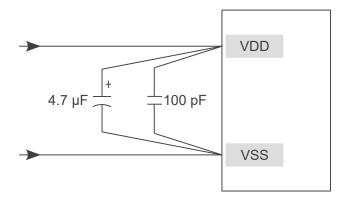

#### 2.5 Reference Schematic

Figure 2.1: 18 Button Mutual Capacitance Reference Schematic

Figure 2.2: 20 Button Mutual Capacitance Reference Schematic

Figure 2.3: 8 Button Self Capacitance Reference Schematic

## 3 Electrical Characteristics

# 3.1 Absolute Maximum Ratings

Table 3.1: Absolute Maximum Ratings

|                                                                                   | Min  | Max                      | Unit |

|-----------------------------------------------------------------------------------|------|--------------------------|------|

| Voltage applied at VDD pin to VSS                                                 | 1.71 | 3.5                      | V    |

| Voltage applied to any $\text{ProxFusion}^{\text{\^{B}}}$ pin (referenced to VSS) | -0.3 | VREGA                    | V    |

| Voltage applied to any other pin (referenced to VSS)                              | -0.3 | VDD + 0.3<br>(3.5 V max) | V    |

| Storage temperature, T <sub>stg</sub>                                             | -40  | 85                       | °C   |

# 3.2 Recommended Operating Conditions

Table 3.2: Recommended Operating Conditions

|                                                |                                                                                                                              | Min                  | Nom                  | Max                                 | Unit |

|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------|-------------------------------------|------|

|                                                | Supply voltage applied at VDD pin:                                                                                           |                      |                      |                                     |      |

| VDD                                            | $F_{OSC} = 14 MHz$                                                                                                           | 1.71                 |                      | 3.5                                 | V    |

|                                                | $F_{OSC} = 18 MHz$                                                                                                           | 2.2                  |                      | 3.5                                 |      |

|                                                | Internal regulated supply output for analog                                                                                  |                      |                      |                                     |      |

| VREGA                                          | domain:                                                                                                                      | 4.40                 | 4.50                 | 4 5 7                               | V    |

|                                                | F <sub>OSC</sub> = 14 MHz                                                                                                    | 1.49                 | 1.53                 | 1.57                                |      |

|                                                | F <sub>OSC</sub> = 18 MHz                                                                                                    | 1.49                 | 1.53                 | 1.57                                |      |

| VREGD                                          | Internal regulated supply output for digital domain:                                                                         | 4.50                 | 4.50                 | 4.04                                | V    |

| VREGD                                          | F <sub>OSC</sub> = 14 MHz                                                                                                    | 1.56                 | 1.59                 | 1.64                                | V    |

| 1/00                                           | F <sub>OSC</sub> = 18 MHz                                                                                                    | 1.75                 | 1.8                  | 1.85                                |      |

| VSS                                            | Supply voltage applied at VSS pin                                                                                            | 4.0                  | 0                    | 0=                                  | V    |

| T <sub>A</sub>                                 | Operating free-air temperature                                                                                               | -40                  | 25                   | 85                                  | °C   |

| C <sub>VDD</sub>                               | Recommended capacitor at VDD                                                                                                 | 2×C <sub>VREGA</sub> | 3×C <sub>VREGA</sub> |                                     | μF   |

| $C_{VREGA}$                                    | Recommended external buffer capacitor at VREGA, ESR $\leq$ 200 m $\Omega$                                                    | 2                    | 4.7                  | 10                                  | μF   |

| C <sub>VREGD</sub>                             | Recommended external buffer capacitor at VREGD, ESR $\leq$ 200 m $\Omega$                                                    | 2                    | 4.7                  | 10                                  | μF   |

| Cx <sub>SELF-VSS</sub>                         | Maximum capacitance between ground and all external electrodes on all ProxFusion <sup>®</sup> blocks (self-capacitance mode) | 1                    |                      | 400 <sup>i</sup>                    | pF   |

| Cm <sub>CTx-CRx</sub>                          | Capacitance between Receiving and Transmitting electrodes on all ProxFusion® blocks (mutual-capacitance mode)                | 0.2                  |                      | 9i                                  | pF   |

| Cp <sub>CRx-VSS</sub>                          | Maximum capacitance between ground and all external electrodes on all ProxFusion <sup>®</sup> blocks                         |                      |                      | _                                   | pF   |

| OPCRX-VSS                                      | Mutual-capacitance mode, $f_{xfer} = 1 \text{ MHz}$<br>Mutual-capacitance mode, $f_{xfer} = 4 \text{ MHz}$                   |                      |                      | 100 <sup>i</sup><br>25 <sup>i</sup> | Pi   |

| Cp <sub>CRx-VSS</sub><br>Cm <sub>CTx-CRx</sub> | Capacitance ratio for optimal SNR in mutual-capacitance mode <sup>ii</sup>                                                   | 10                   |                      | 20                                  | n/a  |

| RCx <sub>CRx/CTx</sub>                         | Series (in-line) resistance of all mutual-capacitance pins (Tx & Rx pins) in mutual-capacitance mode                         | O <sub>iii</sub>     | 0.47                 | 10 <sup>iv</sup>                    | kΩ   |

| RCx <sub>SELF</sub>                            | Series (in-line) resistance of all self-capacitance pins in self-capacitance mode                                            | O <sup>iii</sup>     | 0.47                 | 10 <sup>iv</sup>                    | kΩ   |

## 3.3 ESD Rating

Table 3.3: ESD Rating

|                                            |                                                                 | Value | Unit |

|--------------------------------------------|-----------------------------------------------------------------|-------|------|

| V <sub>(ESD)</sub> Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>v</sup> | ±4000 | V    |

## 3.4 Current Consumption

Mutual Capacitive Mode Setup: Target: CH0 & CH10 = 800, all other channels = 512 @ VDD = 3.3V

**Self-capacitive Mode Setup**: Target = 512,  $f_{xfer}$  = 500kHz @ VDD = 3.3V

Interface Selection: Event mode

Table 3.4: Typical Current Consumption for IQS7222B101

| Power mode | Active channels                                | Report rate<br>(Sampling rate)<br>[ms] | Current [μΑ]<br>Order Code<br>101 |

|------------|------------------------------------------------|----------------------------------------|-----------------------------------|

| NP         | Mutual Capacitance (20 channels)               | 10                                     | 720                               |

| INI        | Self-capacitive (8 channels)                   | 10                                     | 505                               |

| LP         | Mutual Capacitance (20 channels)               | 50                                     | 147                               |

| LI         | Self-capacitive (8 channels)                   | 50                                     | 101                               |

|            | Wake-up proximity - Distributed mutual channel | 100                                    | 14.3                              |

| ULP        | Wake-up proximity - Distributed self channel   | 100                                    | 8.7                               |

| OLF        | Wake-up proximity - Distributed mutual channel | 160                                    | 9.8                               |

|            | Wake-up proximity - Distributed self channel   | 160                                    | 7                                 |

Table 3.5: Typical Current Consumption for IQS7222B201/202

| Power mode | Active channels                                | Report rate (Sampling rate) | Currei<br>Order | nt [μΑ]<br>Code |

|------------|------------------------------------------------|-----------------------------|-----------------|-----------------|

|            |                                                | [ms]                        | 201             | 202             |

| NP         | Mutual Capacitance (20 channels)               | 16                          | 694             | 631             |

| INI        | Self-capacitive (8 channels)                   | 16                          | 457             | 384             |

| LP         | Mutual Capacitance (20 channels)               | 60                          | 180             | 164             |

| LI         | Self-capacitive (8 channels)                   | 60                          | 117             | 100             |

|            | Wake-up proximity - Distributed mutual channel | 100                         | 16.9            | 15.3            |

| ULP        | Wake-up proximity - Distributed self channel   | 100                         | 17.2            | 14.4            |

| OLI        | Wake-up proximity - Distributed mutual channel | 160                         | 12.2            | 11.0            |

|            | Wake-up proximity - Distributed self channel   | 160                         | 12.4            | 10.4            |

$<sup>^{</sup>i}RCx = 0 \Omega$

<sup>&</sup>lt;sup>ii</sup>Please note that the maximum values for Cp and Cm are subject to this ratio.

$<sup>^{\</sup>rm iii}$ Nominal series resistance of 470  $\Omega$  is recommended to prevent received and emitted EMI effects. Typical resistance also adds additional ESD protection.

<sup>&</sup>lt;sup>iv</sup>Series resistance limit is a function of  $F_{xfer}$  and the circuit time constant, RC.  $R_{max} \times C_{max} = \frac{1}{(6 \times f_{xfer})}$  where C is the pin capacitance to VSS.

<sup>&</sup>lt;sup>V</sup>JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. Pins listed as ±4000 V may actually have higher performance.

# 4 Timing and Switching Characteristics

#### 4.1 Reset Levels

Table 4.1: Reset Levels

| Paramete         | er                                            | Min | Тур | Max  | Unit |

|------------------|-----------------------------------------------|-----|-----|------|------|

| V                | Power-up (Reset trigger) - slope > 100 V/s    |     |     | 1.65 | V    |

| V <sub>VDD</sub> | Power-down (Reset trigger) - slope < -100 V/s | 0.9 |     |      | V    |

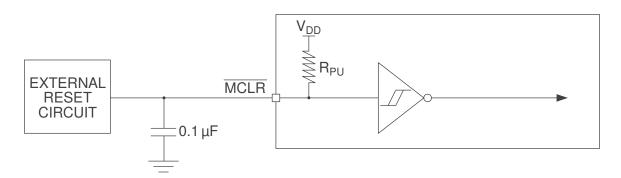

## 4.2 MCLR Pin Levels and Characteristics

Table 4.2: MCLR Pin Characteristics

| Parameter                |                                         | Conditions  | Min       | Тур | Max       | Unit |

|--------------------------|-----------------------------------------|-------------|-----------|-----|-----------|------|

| V                        | MCLD Input low lovel voltage            | VDD = 3.3 V | VSS - 0.3 |     | 1.05      | V    |

| V <sub>IL(MCLR)</sub>    | MCLR Input low level voltage            | VDD = 1.7 V | V35 - 0.3 | -   | 0.75      | V    |

| V                        | MOLD broad bink level with an           |             | 2.25      |     | V/DD 0.0  | V    |

| V <sub>IH(MCLR)</sub>    | MCLR Input high level voltage           | VDD = 1.7 V | 1.05      | -   | VDD + 0.3 | V    |

| R <sub>PU(MCLR)</sub>    | MCLR pull-up equivalent resistor        |             | 180       | 210 | 240       | kΩ   |

| +                        | MCI D input pulse width the trigger     | VDD = 3.3 V |           |     | 15        | no   |

| <sup>t</sup> PULSE(MCLR) | MCLR input pulse width – no trigger     | VDD = 1.7 V | -         | -   | 10        | ns   |

| t <sub>TRIG(MCLR)</sub>  | MCLR input pulse width – ensure trigger |             | 250       | -   | -         | ns   |

Figure 4.1: MCLR Pin Diagram