## **General Description**

The packages with solder balls from ESPROS Photonics are Wafer-Level Chip-Scale Packages (WL-CSP) for use in standard SMT assembly lines with standard SMT processes and equipment. Due to the very thin and space saving silicon chip substrate, the assembly process needs specific attention. The chips are quite brittle and need careful handling. However, by following the guidelines described herein, high yield production and high reliability products can be achieved.

Please note that this information was prepared on certain equipment, with certain PCB base material and consumables under certain conditions. It is in the responsibility of the assembler / process owner to develop and qualify his own process and process parameters and materials to achieve the best results.

Industry experience has shown that ESPROS' WL-CSP packages are fully SMT compatible. Assembly and underfill can be achieved by standard tools and processes. Stable processes will return industry standard quality and yield results. If not otherwise stated in this application note, general rules and requirements for SMT assembly need to be observed.

## **Features**

- PCB layout advice

- Substrate material selection

- Equipment considerations

- SMT assembly process recommendations

- Underfill processing

- Cleaning

- Inspection

Figure 1: epc611 WL-CSP Chip size 2.65 x 2.65mm

Figure 2: epc901 with CSP32 package Note the high aspect ratio of 8.0 x 1.3mm

# **Table of Contents**

| 1. Process flow                                                                                                                                                   | 3        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 2. Recommended PCB design guidelines  2.1. SMT footprint design  2.2. PCB material                                                                                | 3        |

| 3. Stencil printing 3.1. Equipment and tools 3.2. Solder paste 3.3. Stencil                                                                                       | 5        |

| 4. Pick-and-place processing  4.1. Moisture sensitivity level (MSL)  4.2. Machine capability and requirements  4.3. Picking and placement parameters  4.4. Nozzle | 5<br>6   |

| 5. Soldering  6. Underfill                                                                                                                                        | 8        |

| 7. Testing and depaneling of modules                                                                                                                              | 9        |

| 9. Cleaning                                                                                                                                                       |          |

| 11. Rework                                                                                                                                                        | 10       |

| 13. Checklist questions  14. Process Support                                                                                                                      | 10       |

| 15. Summary IMPORTANT NOTICE                                                                                                                                      | 10<br>11 |

## 1. Process flow

The assembly shall follow standard SMT assembly processes like

- Drying of the substrate material

- Printing of solder paste on a PCB

- Component placement using pick-and-place equipment

- Soldering by applying a reflow soldering process

- Cleaning

- Underfill application and curing

- Inspection

# 2. Recommended PCB design guidelines

Good assembly and reliability results can be achieved only by applying an appropriate PCB layout. The pad and the solder mask designs are especially important. If the given advice is not applied, pad lift-off and other assembly defects can occur. Refer as well to the product datasheets where product-specific layout information is provided.

### 2.1. SMT footprint design

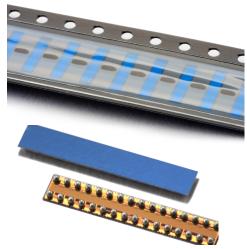

For the PCB fabrication, the following two types of PCB pads/land patterns referred in 3 are used for surface mount assembly:

Figure 3: Basic footprint designs

### ■ Recommended: Non-solder mask defined

The metal pad on the PCB is smaller than the solder mask opening (left picture in 3).

We recommend NSMD pads for CSP, because the copper etching process has a better pattern definition than with the solder masking process and therefore improves the reliability of the solder joints.

#### ■ Not recommended: Solder mask defined

The solder mask opening is smaller than the metal pad.

It is not recommended because lower pitches may not work with this layout due to PCB limitations. A misalignment of the solder mask can cause defects like pad lift-off or openings.

The design of the landing pads has to follow the recommendations for trace, space and solder mask capabilities of the PCB manufacturer. The recommended pad geometry in 1 is for the use of fine-line PCB boards:

| Dimension                  | Ref. | Fine-line PCB |

|----------------------------|------|---------------|

| Pad pitch                  |      | 450μm *       |

| Pad diameter               | Α    | max. 300µm    |

| Line width                 | В    | min. 150μm ** |

| Ratio track to landing pad | B/A  | max. 50%      |

| Space track to line        |      | min. 150μm ** |

| Space track to solder mask | С    | 100μm **      |

Table 1: Recommended PCB design guidelines e.g. epc300

Notes: \* Dimensions defined by chip

\*\* Dimensions defined by PCB design rules

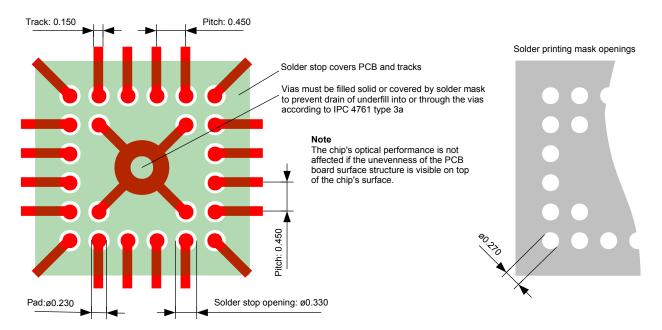

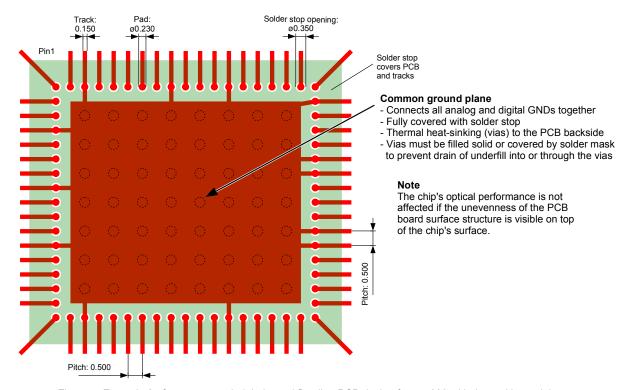

The designer has to take care about the wettable area between the track which is not covered by the solder mask and the landing pad in order to reduce solder drain as much as possible. The trace width at the connection to the landing pad should be as small as possible and must not exceed 50% of the pad diameter. The distance from the solder mask to the landing pad needs to be as small as possible.

The solder mask accuracy and alignment capability of the board manufacturer should be considered first to ensure that the solder mask opening is max. 100 µm larger than the pad on either side.

The fan-out of the tracks should be symmetrical and balanced across both the x and y directions to avoid part rotation and offset forces due to surface tension of the tin during soldering (refer to 4).

Figure 4: Example 1 of a recommended, balanced fine-line PCB design for epc611 with a "closed" center via of the GND pads (dimensions in mm)

Figure 5: Example 2 of a recommended, balanced fine-line PCB design for epc660 with thermal heat-sink (dimensions in mm)

#### IMPORTANT:

1. Reference PCB designs

Reference PCB designs and footprints in the datasheets of the chips are always based on latest practice experience for the individual part and can be more comprehensive than the examples herein. ESPROS suggest to use designs according these proposals.

2. Pull-back of components next to the chip

Refer to Chapter 6 for free distance between TOF chip and other components next to, assembled on the same PCB side.

All advises in this application note shall help the PCB board designer and assembly responsible having a better understanding of the principle of the way to reliably assemble modules with very thin, 50µm thickness, and brittle wafer level chip scale packages (WL CSP).

#### 2.2. PCB material

ESPROS chips can be assembled on standard epoxy-glass substrates. However, High-Tg FR-4 substrate provides much higher reliability over standard FR-4 material due to a lower thermal expansion coefficient (CTE-z). A copper layer thickness of 35μm (1 oz) or less is necessary to achieve the required patterning definition. A higher copper thickness results in lower pad accuracy.

Via-in-pad is not recommended to prevent voiding of the solder joint due to uneven planarity of the pad.

The final layer on the metal pad has a significant effect on assembly yield and reliability. Organic surface preservative (OSP), immersion tin, or electroless nickel/immersion gold with gold thickness limited to <0.2  $\mu$ m are the most appropriate finishes. HASL (Hot Air Solder Leveled) board finish is not recommended.

## 3. Stencil printing

The pad diameter of ESPROS' WL-CSP packages is typically 200 - 300µm. This should not pose any fundamental problems to modern SMD assembly. However, proper application of the solder paste is the baseline for a stable assembly process and both stencil printing equipment as well as the choice of soldering paste are major criteria. The following parameters have demonstrated good results and may therefore be referred to as a guideline.

#### 3.1. Equipment and tools

A fully automatic inline stencil printer shall be used for this process:

Process positioning accuracy:  $\pm 20 \mu m$ ,  $6\sigma$ Stencil cleaning:  $\pm 20 \mu m$ ,  $6\sigma$

Cleaning cycle: After each print by wet/vacuum/dry

Alignment: With vision system using 2-3 markers

Print verification by a 2.5D vision system is highly recommended for high yield results. Experience shows that the process can be stabilized without the requirement of a 100% vision inspection.

#### 3.2. Solder paste

Solder paste type is a key factor for stable assembly results. Solder paste Senju M705-RGS800HF has proven good and stable results (www.senju-m.co.jp):

Type: SAC305 (96.5Sn/3.0Ag,0.5Cu), Type 5

Solder flux class: No-Clean; ROL0

3.3. Stencil

Thickness: 100um

Surface: Electrolytic polishing (nickel, gives enhanced dissolving behavior and longterm stability)

Opening: Pad diameter 270 .. 300µm, according to ESPROS product datasheet.

(Stencil aperture circumferentially reduced by 5-10%)

## 4. Pick-and-place processing

## 4.1. Moisture sensitivity level (MSL)

There is no need of die preparation, e.g. baking prior to SMD assembly, because ESPROS' bare silicon dies are not moisture sensitive. This is due to the fact that there is no organic material in the packages.

Since there is no organic material in our packages, MSL classification cannot be applied. It's more like a hermetic package which cannot collect and prevent water vapor inside the package. That's better than the best MSL class.

However, we recommend the following:

- Store the parts inside the unopened, sealed plastic bag. The bag contains Nitrogen (N) which keeps humidity away. Humidity can lead to corrosion and oxidation of the solder balls.

- If a bag is opened, store the parts in a Nitrogen atmosphere to avoid corrosion or oxidation of the solder balls.

- No baking of the parts is needed.

- Make sure, the PCB is baked out before the assembly process to avoid popcorn effects.

#### 4.2. Machine capability and requirements

The pick-and-place machine should have a repeatability and accuracy capable of placing 0402 components or better. Standard feeders for tape and reel can be used.

Vision alignment should be used to place the components. The alignment can be done on the part edges. It is typically not necessary to make the alignment based on the solder balls.

We strongly recommend to use a vision system which is capable to identify pin 1, according to the data sheet.

Placing by the use of standard fiducials on the panel works well. Local fiducials are not necessarily required. ESPROS' CSP devices with solder bumps self-align when placed, even with a (small) offset, due to the self-centering nature of the tin-alloy solder balls.

Attention should be taken to z-height placement to insure that the solder balls or the chips are not damaged (compressed) during picking and placement. The placement force should be kept to  $\leq 0.8N$  to slightly press the balls into the solder paste.

#### 4.3. Picking and placement parameters

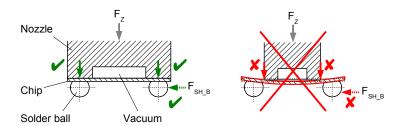

Picking and placement parameters have to be well controlled due to the chip thickness of 50µm. High stress during pick or place, especially in the z-axis, may lead to chipping of the thin dies. The following specifications of the pick-and-place tool was used in the verification of this assembly process, refer to 7:

Placement accuracy x/y: Min.  $\pm$  50 $\mu$ m 4 $\sigma$  (for pad size 0.3mm)

Theta accuracy: ± 0.05°

Maximum vertical force  $F_z$  per chip: Conventional CMOS chip e.g. epc13x:  $\leq 1.5N$

50µm thick photosensitive chip e.g. epc611, epc901, ...: ≤ 0.8 N preferred

Preferred is forceless picking and placing with vacuum only.

Maximum shear force  $F_{SH\_B}$  per ball:  $\leq 25gf$  in any direction

It is very important that the picking process lifts the chip from the tape high enough in the vertical direction in order to avoid any collision between the solder balls underneath the chip and the tape cavity boundaries. A collision may lead to lost solder balls during the assembly process.

Special care should also be taken to achieve a stable and continuous tape feeding process. Jerking during the feeding motion may lead to chip displacement in the tape cavity which may impede proper picking.

It is also highly recommended to use a "kiss-and-goodbye" concept to place the component. It means that the nozzle should not touch the part to the solder paste but rather blow it away at close distance when it does the placing.

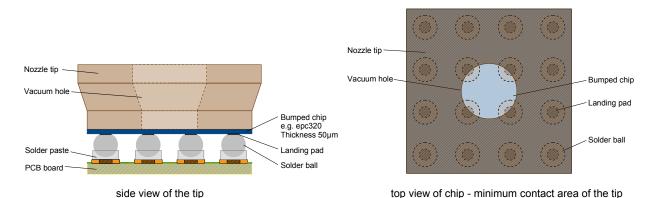

#### 4.4. Nozzle

To minimize mechanical damage possibilities, the pick-up tool must have a compliant tip. Standard nozzles adapted to the chip geometry will easily pick up the part. Recommended is a plastic or ceramic tip with a contact area equal to the chip size, refer to 6.

Figure 6: Pick-and-place tool for epc320

#### The nozzle

- shall have a flat surface with better than 10µm flatness

- surface roughness shall be better than 100nm (polished)

- pickup area must not touch the pixel-field area

- should not have any flashes.

- must have the same size as the chip, maximal contact area on the chip. Refer to 7.

- Take care using not a too strong vacuum. It can lead to bending effects of the chip or to not correct picking the chip.

The chip can get damaged if the above guidelines are not followed! With tooling designated as "use only for optical devices" you can keep the surfaces clean and prevent any damage to the very sensitive surfaces of photosensitive parts.

Figure 7: Pick-and-place; left: good nozzle, good picking; right: bad nozzle, bad picking

In order to reduce stress on the chip, it is advised that the nozzle has maximal contact area on the chip. The nozzle has to bring the  $F_Z$  force evenly distributed vertically to the center of the solder balls during picking and placing. Refer to 7, left picture. It means that it should be large enough so that it picks the chip not just in the middle of the part but also in the area above the solder balls.

Bending of the chip is not allowed, nor caused by picking or placing forces nor by the vacuum of the nozzle. Refer to 7, right picture.

Keep attention to have no shear forces on the solder balls during picking the chip from the tape pocket and/or placing. Do touch with the chip nor the pocket walls nor anywhere.

## 5. Soldering

ESPROS' CSP devices are compatible with industry standard reflow process for both lead-free (RoHS) and Sn/Pb eutectic solder compositions to form solder joint interconnections.

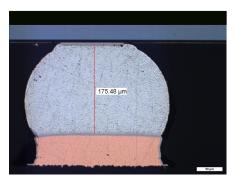

Figure 8: Cross section of a solder ball (epc611 on top of a fine-line PCB)

Once soldered, the chip remains fragile and should be protected against mechanical contact. The chips may get damaged if PCB's are dropped or exposed to high acceleration before the underfill is applied.

Soldering is done by reflow process following the J-STD-020 standard. Optimization parameters by the respective solder paste manufacturer should be observed. The temperature gradient of the reflow process should be kept as low as possible and should not exceed the values stated in 2 to prevent possible bending of the PCB.

## Qualified reflow operations is:

| Item                        | Description                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Solder ball alloy           | typically Sn96.5Ag3.0Cu0.5 (SAC305), refer to the ESPROS datasheet                                                                                                                                                                                                                                                                                                                                 |

| Soldering profile           | follow the recommendations of IPC/JEDEC J-STD020C (revision C and later) for lead-free assembly                                                                                                                                                                                                                                                                                                    |

| Soldering peak temperature  | 240°C with 60s time above liquid (T <sub>AL</sub> ).  Important Note: The chip itself can withhold higher temperature. However the maximum peak temperature for the solder paste we recommend is 255°C. Furthermore the mismatch in thermal expansion of the chip and PCB gets more significant the higher the temperature and can lead to bad chip soldering or at some point even chip breakage. |

| Temperature gradients       | Heating up: max. +2.5 °C/s; cooling down: max. 6 °C/s                                                                                                                                                                                                                                                                                                                                              |

| Soldering in protection air | Nitrogen purge during solder process (recommended)                                                                                                                                                                                                                                                                                                                                                 |

Table 2: Soldering

## 6. Underfill

In order to achieve JEDEC temperature cycle requirements, underfill is a must to reduce thermal and mechanical fatigue as well as to increase longterm reliability.

Applying underfill under the CSP components reduces stress to the solder pads caused by e.g. temperature cycling or mechanical bending of the PCB. The thermal and mechanical fatigue will be reduced and the longterm reliability will be increased. Underfill process and product (type) is application specific. It shall follow JEDEC-STD JEP150: Stress-test-driven qualification of and failure mechanisms associated with assembled solid state surface mount components.

In order to avoid mechanical damage, a jet dispenser is preferred for the underfill application. The process was verified with an inline tool that meets a placing accuracy of ± 50um @ 6σ.

A suitable underfill product is to be chosen with respect to the specific customer requirements. Factors like pot/shelf life, curing process ramp and time are to be considered.

The following key specifications may be used as a reference:

| Chip<br>model                        | Chip<br>size                                   | Underfill                     | Manu-<br>facturer        | Visco-<br>sity   | Pot<br>life | Process<br>tempe-<br>rature | Curing ramp _/¯\_                                                                                           |                       | o _/¯\_                                                                                             | Comments                                   |

|--------------------------------------|------------------------------------------------|-------------------------------|--------------------------|------------------|-------------|-----------------------------|-------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------|--------------------------------------------|

|                                      | [mm]                                           | Туре                          |                          | [cPs]            | [h]         | [°C]                        | ramp-up                                                                                                     | dwell                 | ramp-dow                                                                                            |                                            |

| epc200<br>epc3xx<br>epc611<br>epc660 | 1.8 x 1.8<br>various<br>2.8 x 2.8<br>9.7 x 8.7 | Loctite<br>Eccobond<br>FP4531 | Henkel                   | 10'000           | 24          | 60 - 90                     | 80°C →<br>120°C,<br>gradient:<br>2.5°C/min                                                                  | 120°C<br>for<br>40min | $\begin{array}{c} 120^{o}C \rightarrow t_{a},\\ \text{gradient:}\\ 0.8^{o}C/\text{min} \end{array}$ | Automotive applications (high reliability) |

| epc635<br>epc901                     | 6.3 x 4.2<br>8.0 x 1.4                         | XSUF<br>1594-1                | Namics                   | 700              | 24          | 20 - 60                     | $\begin{array}{c} t_a \rightarrow 120^{\circ}C, \\ \text{gradient:} \\ 2.5^{\circ}C/\text{min} \end{array}$ | 120°C<br>for 1h       | $\begin{array}{c} 120^{o}C \rightarrow t_{a},\\ \text{gradient:}\\ 0.8^{o}C/\text{min} \end{array}$ | Re-workable underfill                      |

| epc200<br>epc611                     | 1.8 x 1.8<br>2.8 x 2.8                         | Epotek<br>353 ND              | Epoxy<br>Tech-<br>nology | 3'000 -<br>5'000 | 3           | 80                          | 80°C →<br>100°C,<br>gradient:<br>10°C/min                                                                   | 100°C<br>for<br>30min | $\begin{array}{c} 100^{o}C \rightarrow t_{a},\\ \text{gradient:}\\ 0.6^{o}C/\text{min} \end{array}$ |                                            |

|                                      |                                                | Epicol 33                     | APM<br>Technica          | 300 - 600        | 6           | 20 - 24                     | $t_a \rightarrow 90^{\circ}\text{C},$ gradient: 1°C/min                                                     | 90°C<br>for<br>60min  | $90^{\circ}C \rightarrow t_{a}$ , gradient: $1^{\circ}C/min$                                        |                                            |

Table 3: Overview underfill application

#### Important notes:

- Curing has to take place directly after dispensing the underfill. Keep retention time as short as possible.

- Process temperature: Component and PCB board shall have this temperature during underfill process. The underfill has ambient temperature and gets fluid during application.

- Never exceed the maximum rated temperature.

- Dispensing tools: Follow strictly the recommendations of the underfill manufacturer, e.g. for Namics XSUF 1594-1: Use a dispensing needle with gauge 18 23 (ID 0.33 0.84 mm).

- No open vias in the underfill area. Refer to 4 and 5.

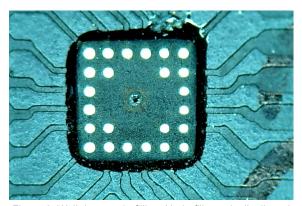

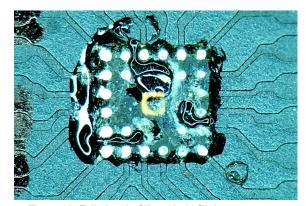

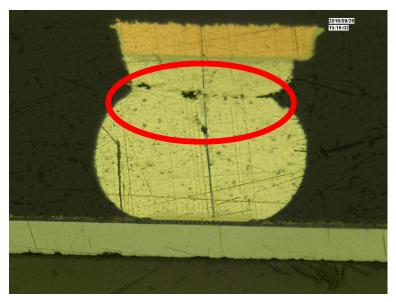

Figure 9: Well done underfilling. Underfill evenly distributed underneath of the chip (view of PCB with chip removed)

Figure 10: Failed underfilling. Underfill does not cover underneath full chip area (view of PCB with chip removed)

### 6.1. PCB design for covering assembly and underfill needs

The proposed footprints for chips e.g. in Chapter 2.1 cover mainly the assembly needs for the chips themselves. Rules for surrounding the chip, on the same PCB side, with other components depends strongly from the available assembly processes and machines as well as of the used tooling for the underfill process. The user has to adjust the necessary pull-backs of these components according to the manufacturing line recommendations.

Here a general example which shows a way to treat this:

- 1. The, by the underfill manufacturer recommended, dispensing needle in this example shall have an exterior diameter of 0.65mm.

- 2. During the underfill process, the assembler should not go with the needle too close to e.g. the epc660 chip. It is due to the risk of touching, damaging the chip or prevent of flowing of underfill onto chip's top surface.

- 3. On the other hand, too far is also not good otherwise the underfill does not flow perfectly under the chip.

- 4. Thereof, a good approach for the design can be:

- Keep clear a gap of minimum 1.5 mm between chip and components on 1 or 2 sides for I- or L-type underfill dispensing, respectively.

- All other sides can have a free minimum distance of 1 mm.

- Around all 4 corners reserve free a radius of 1.5mm.

- U-type underfill dispensing is not recommended.

## 7. Testing and de-paneling of modules

Electrical testing and de-paneling of modules (separation, singularization) with WL CSP chips assembled and under-filled follow the same rules as necessary e.g. for large ceramic multilayer capacitors. Under-filled chips are quite robust but still, handle the circuits with the necessary care to prevent of mechanical damaging of the chips e.g. by bending to break solder ball interconnects on chip side.

The forces to probe, mill or cut the modules shall not stress e.g. vibrations or bend the PCB boards. We do not suggest to depanel modules by punching. For very thin PCB carriers, we propose to separate the PCBs before assembly and use during the assembly, soldering and testing process multi-module carrier frames instead of processing them in full panels.

#### IMPORTANT:

ESPROS dissuades from testing and de-paneling of panels or modules with not under-filled chips due to the risk of yield loss or long-term aging effects caused by applied mechanical stress to the chip.

### 8. Process and environment cleanliness

The ESPROS WL-CSP products are imagers or photo-electric chips which convert light into electric charge. The photosensitive area is on the top of the chip which is called the optical window. If there is dirt on this surface, the optical properties of the imager can be negatively affected. Therefore, the processes to assemble the chips including the application of underfill and further processing of the assembled PCB's should be done under cleanroom conditions matching the final optical requirements.

## 9. Cleaning

No cleaning is necessary if solder paste with no-clean flux is used. Otherwise the cleaning step depends on type of flux used. The approved component surface cleaning agent is Isopropanol or the like.

## 10. Inspection

Regular process quality inspections, e.g. per lot, are suggested. Voids, oxide and solder failures can be detected easily by cross-sections of the bumps.

Figure 11: Lost contact due to a head-in-pillow (snowman) defect during soldering (cross section of the solder ball)

### 11. Rework

Replacement of the component prior to the start of underfilling is possible using appropriate standard rework equipment.

## 12. Storage of components

The following procedures shall apply for the (long term) storage, unless otherwise specified:

- ESPROS' CSP devices are not moisture sensitive (JEDEC J-STD-020). They do not need baking before mounting. In case of a necessary bake, components in tape on reel may not be baked at any temperature > 40° C. Do not apply more than one bake cycle.

- Preferred storage is on reel in a hermetic sealing which covers the components from mechanical damaging, dust, foreign particles or pollution (JEDEC J-STD-033 and EIA-583).

- Components should be stored (resealed) in dry environment to reduce to a minimum the oxidation of solder or solder balls (10% RH, clean dry air bagging or vacuum bagging as a minimum). See also next item.

- Components should be stored (resealed) in a non-oxidizing atmosphere to reduce to a minimum the oxidation of solder or solder balls. Storage in nitrogen atmosphere is suggested.

- Storage temperature should be in the range of 18 ... 24° C for products not in process or transit.

- The sealing/packaging material should be either conductive or antistatic. The electrostatic discharge sensitive (ESD) protection should be compliant with JESD625 and EIA 541.

- Products should be used based upon the first-in, first-out (FIFO) inventory method.

## 13. Checklist questions

If significant yield losses occur, the following checks may help to identify the root cause of the problem.

| Problem                                                                                | Root cause                                                                                                                                                                                                                                                                                                                                                       | Solution                                                                                                                                            |

|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Are cracks or other mechanical defects visible on the chip?                            | <ul> <li>Pick-and-place has inappropriate z movement-forces</li> <li>The PCB mechanically stressed during assembly or operation</li> <li>PCB separation from panel (de-panelization) may induce mechanical stress, typically bending to the PCB</li> </ul>                                                                                                       | <ul> <li>Refer to section 4 Pick-and-place processing</li> <li>Use a de-panelization tool with zero-force to the PCB, e.g. laser cutting</li> </ul> |

| Are head-in-pillow defects visible?                                                    | <ul> <li>Pad geometry not appropriate</li> <li>Does the layout correspond to the recommendation? Especially critical is the solder-stop mask.</li> <li>Solder paste printing process not stable, not properly cleaned stencil mask</li> <li>Use appropriate type of solder-paste</li> </ul>                                                                      | <ul> <li>Refer to section 2.1 SMT footprint design</li> <li>Refer to 3 Stencil printing</li> <li>Refer to 5 Soldering</li> </ul>                    |

| Reliability qualifications fails with contact opening or mechanical damage of the chip | <ul> <li>No underfill used</li> <li>Wrong underfill used</li> <li>Shelf time and curing process inappropriate</li> <li>Curing has not taken place immediately after application of the underfill</li> <li>The underfill is not cured</li> <li>Temperature profile for curing the underfill is not appropriate</li> <li>Curing temperature is too high</li> </ul> | ■ Refer to 6 Underfill                                                                                                                              |

## 14. Process Support

In order to support our customers in case of assembly and/or reliability issues, the following information shall be provided:

- Cross-sections pictures

- ESPROS lot number

- Delivery date of product

## 15. Summary

Industry experience has shown that ESPROS' WL-CSP packages are fully SMT compatible. Assembly and underfill can be achieved by standard tools and processes. Stable processes will return industry standard quality and yield results. If not otherwise stated in this application note, general rules and requirements for SMT assembly need to be observed.

### IMPORTANT NOTICE

ESPROS Photonics AG and its subsidiaries (epc) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to epc's terms and conditions of sale supplied at the time of order acknowledgment.

epc warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with epc's standard warranty. Testing and other quality control techniques are used to the extent epc deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

epc assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using epc components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

epc does not warrant or represent that any license, either express or implied, is granted under any epc patent right, copyright, mask work right, or other epc intellectual property right relating to any combination, machine, or process in which epc products or services are used. Information published by epc regarding third-party products or services does not constitute a license from epc to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from epc under the patents or other intellectual property of epc.

Resale of epc products or services with statements different from or beyond the parameters stated by epc for that product or service voids all express and any implied warranties for the associated epc product or service. epc is not responsible or liable for any such statements.

epc products are not authorized for use in safety-critical applications (such as life support) where a failure of the epc product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of epc products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by epc. Further, Buyers must fully indemnify epc and its representatives against any damages arising out of the use of epc products in such safety-critical applications.

epc products are neither designed nor intended for use in military/aerospace applications or environments unless the epc products are specifically designated by epc as military-grade. Only products designated by epc as military-grade meet military specifications. Buyers acknowledge and agree that any such use of epc products which epc has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

epc products are neither designed nor intended for use in automotive applications or environments unless the specific epc products are designated by epc as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, epc will not be responsible for any failure to meet such requirements.