# STM32MP151x STM32MP153x STM32MP157x

Errata sheet

# STM32MP151x/3x/7x device errata

# **Applicability**

This document applies to the part numbers of STM32MP151x/3x/7x devices and the device variants as stated in this page.

It gives a summary and a description of the device errata, with respect to the device datasheet and reference manual RM0441 for STM32MP151x, RM0442 for STM32MP153x, and RM0436 for STM32MP157x.

Deviation of the real device behavior from the intended device behavior is considered to be a device limitation. Deviation of the description in the reference manual or the datasheet from the intended device behavior is considered to be a documentation erratum. The term "errata" applies both to limitations and documentation errata.

Table 1. Device summary

| Reference   | Part numbers                                       |  |

|-------------|----------------------------------------------------|--|

| STM32MP151x | STM32MP151A, STM32MP151C, STM32MP151D, STM32MP151F |  |

| STM32MP153x | STM32MP153A, STM32MP153C, STM32MP153D, STM32MP153F |  |

| STM32MP157x | STM32MP157A, STM32MP157C, STM32MP157D, STM32MP157F |  |

Table 2. Device variants

| Reference         | Silicon revision codes        |                       |  |

|-------------------|-------------------------------|-----------------------|--|

| Reference         | Device marking <sup>(1)</sup> | REV_ID <sup>(2)</sup> |  |

| STM32MP151x/3x/7x | В                             | 0x2000                |  |

| STM32MP151x/3x/7x | Z                             | 0x2001                |  |

<sup>1.</sup> Refer to the device datasheet for how to identify this code on different types of package.

<sup>2.</sup> REV\_ID[15:0] bitfield of DBGMCU\_IDC register.

# 1 Summary of device errata

The following table gives a quick reference to the STM32MP151x/3x/7x device limitations and their status:

A = limitation present, workaround available

N = limitation present, no workaround available

P = limitation present, partial workaround available

"-" = limitation absent

Applicability of a workaround may depend on specific conditions of target application. Adoption of a workaround may cause restrictions to target application. Workaround for a limitation is deemed partial if it only reduces the rate of occurrence and/or consequences of the limitation, or if it is fully effective for only a subset of instances on the device or in only a subset of operating modes, of the function concerned.

Table 3. Summary of device limitations

|                    |         | Limitation                                                                                     |   | Status    |  |

|--------------------|---------|------------------------------------------------------------------------------------------------|---|-----------|--|

| Function           | Section |                                                                                                |   | Rev.<br>Z |  |

|                    | 2.1.1   | Memory locations might be accessed speculatively due to instruction fetches when HCR.VM is set |   | А         |  |

| Arm Cortex-A7      | 2.1.2   | Cache maintenance by set/way operations can execute out of order                               | Α | Α         |  |

| core               | 2.1.3   | PMU events 0x07, 0x0C, and 0x0E do not increment correctly                                     | N | N         |  |

|                    | 2.1.4   | PMU event counter 0x14 does not increment correctly                                            | Α | Α         |  |

|                    | 2.1.5   | Exception mask bits are cleared when an exception is taken in Hyp mode                         | N | N         |  |

|                    | 2.2.1   | Interrupted loads to SP can cause erroneous behavior                                           | Α | Α         |  |

| Arm Cortex-M4 core | 2.2.2   | VDIV or VSQRT instructions might not complete correctly when very short ISRs are used          | Α | Α         |  |

|                    | 2.2.3   | Store immediate overlapping exception return operation might vector to incorrect interrupt     | Α | Α         |  |

|                    | 2.3.1   | TPIU fails to output sync after the pattern generator is disabled in Normal mode               | Α | Α         |  |

|                    | 2.3.2   | Serial-wire multi-drop debug not supported                                                     | N | N         |  |

|                    | 2.3.3   | HSE external oscillator required in some LTDC use cases                                        | Р | Р         |  |

|                    | 2.3.4   | RCC cannot exit Stop and LP-Stop modes                                                         | Α | Α         |  |

|                    | 2.3.5   | Incorrect reset of glitch-free kernel clock switch                                             | Р | Р         |  |

|                    | 2.3.6   | Limitation of aclk/hclk5/hclk6 to 200 MHz when used as SDMMC1/2 kernel clock                   |   | Р         |  |

|                    | 2.3.7   | Overconsumption in Standby with on-board 1.8 V regulator bypassed                              | Α | -         |  |

|                    | 2.3.8   | eMMC boot timeout too short                                                                    |   | -         |  |

| System             | 2.3.9   | Cortex-M4 cannot use I/O compensation on Standby mode exit                                     | Α | Α         |  |

|                    | 2.3.10  | Missed wake-up events in CSTANDBY                                                              |   | -         |  |

|                    | 2.3.12  | RCC security settings for Cortex-M4 access are not kept upon wake up from Standby              | N | N         |  |

|                    | 2.3.13  | Wakeup pin flags cleared at Standby mode exit with MCU_BEN high and MPU_BEN low                | N | N         |  |

|                    | 2.3.14  | Boundary scan data unduly sampled on TCK falling edge                                          | Α | Α         |  |

|                    | 2.3.15  | Boundary scan SAMPLE/PRELOAD behavior not compliant with IEE1149.1                             |   | Α         |  |

|                    | 2.3.16  | Boot with a specific combination of NAND Flash memories fails                                  | N | -         |  |

|                    | 2.3.17  | Boot with 1-bit error correction on SLC NAND Flash memory fails                                | Α | -         |  |

ES0438 - Rev 8 page 2/56

|          |         |                                                                                                                                                 | Status |                 |

|----------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------------|

| Function | Section | Limitation                                                                                                                                      |        | Re <sup>v</sup> |

|          | 2.3.18  | Boot fails if eMMC does not answer the first command                                                                                            | N      | -               |

|          | 2.3.19  | DLYB limits SDMMC throughput                                                                                                                    | N      | N               |

| Custom   | 2.3.20  | LSE CSS cannot be used in VBAT state                                                                                                            | N      | N               |

| System   | 2.3.21  | Wrong value in Coresight M4 ROM table                                                                                                           | Α      | Α               |

|          | 2.3.22  | Improper isolation of protected secure resources                                                                                                | Р      | Р               |

|          | 2.3.23  | LSE crystal oscillator may be disturbed by transitions on PC13                                                                                  | N      | N               |

|          | 2.4.1   | DDRPHYC overconsumption upon reset or Standby mode exit                                                                                         | Α      | -               |

| DDRPHYC  | 2.4.2   | DDR_CLK jitter out of JEDEC requirement for 32-bit LPDDR2/LPDDR3 at low device Tj                                                               | Α      | А               |

|          | 2.4.3   | Data corruption at low device $T_{\rm j}$ combined with low 32-bit LPDDR2/LPDDR3 I/O supply voltage                                             | Α      | А               |

| GPIO     | 2.5.1   | GPIO assigned to DAC cannot be used in output mode when the DAC output is connected to on-chip peripheral                                       | N      | N               |

|          | 2.7.1   | SOFx not asserted when writing into DMAMUX_CFR register                                                                                         | N      | N               |

|          | 2.7.2   | OFx not asserted for trigger event coinciding with last DMAMUX request                                                                          | N      | N               |

| DMAMUX   | 2.7.3   | OFx not asserted when writing into DMAMUX_RGCFR register                                                                                        | N      | N               |

|          | 2.7.4   | Wrong input DMA request routed upon specific DMAMUX_CxCR register write coinciding with synchronization event                                   | Α      | A               |

|          | 2.8.1   | NOR Flash memory/PSRAM incorrect bus turnaround timing                                                                                          | Α      | Α               |

|          | 2.8.2   | Incorrect FMC_CLK clock period when CLKDIV value is changed on-the-fly in Continuous clock mode                                                 |        | Д               |

| EMC      | 2.8.3   | NAND Flash memory IREF/IFEF flags wrongly asserted just after enabling in FMC_IER                                                               |        | А               |

| FMC      | 2.8.4   | Command sequencer accesses NAND Flash memory device while PBKEN bit is cleared in FMC_PCR                                                       |        | Α               |

|          | 2.8.5   | NAND Flash memory IREF flag wrongly asserted after reset                                                                                        |        | Δ               |

|          | 2.8.6   | NAND ECC corrupted due to insufficient ECCEN low period in between sectors                                                                      |        | Д               |

| OLIADODI | 2.9.1   | Memory-mapped read of last memory byte fails                                                                                                    | Р      | F               |

| QUADSPI  | 2.9.2   | Wrong value inside the QUADSPI_VERR register                                                                                                    | N      | N               |

|          | 2.10.1  | New context conversion initiated without waiting for trigger when writing new context in ADC_JSQR with JQDIS = 0 and JQM = 0                    | Α      | Α               |

|          | 2.10.2  | Two consecutive context conversions fail when writing new context in ADC_JSQR just after previous context completion with JQDIS = 0 and JQM = 0 | А      | Δ               |

| ADC      | 2.10.3  | Unexpected regular conversion when two consecutive injected conversions are performed in Dual interleaved mode                                  | Α      | Δ               |

|          | 2.10.4  | ADC_AWDy_OUT reset by non-guarded channels                                                                                                      | Α      | A               |

|          | 2.10.5  | Injected data stored in the wrong ADC_JDRx registers                                                                                            | Α      | Α               |

|          | 2.10.6  | ADC slave data may be shifted in Dual regular simultaneous mode                                                                                 | Α      | Α               |

|          | 2.10.7  | ADC ANA0/ANA1 resolution limited when Gigabit Ethernet is used                                                                                  | Р      | F               |

|          | 2.10.8  | ADC missing codes in differential 16-bit static acquisition                                                                                     | Р      | F               |

| VDEEDLIE | 2.12.1  | VREFBUF Hold mode cannot be used                                                                                                                | N      | N               |

| VREFBUF  | 2.12.2  | Overshoot on VREFBUF output                                                                                                                     | Α      | Δ               |

ES0438 - Rev 8 page 3/56

|              |         | Limitation                                                                                                       |   | Status    |  |

|--------------|---------|------------------------------------------------------------------------------------------------------------------|---|-----------|--|

| Function     | Section |                                                                                                                  |   | Rev.<br>Z |  |

| DAC          | 2.11.1  | Invalid DAC channel analog output if the DAC channel MODE bitfield is programmed before DAC initialization       |   | Α         |  |

| DAC          | 2.11.2  | DMA underrun flag not set when an internal trigger is detected on the clock cycle of the DMA request acknowledge | N | N         |  |

| DTS          | 2.13.1  | DTS incorrect operation with LSE as reference clock and PCLK enabled                                             | Р | Р         |  |

|              | 2.14.4  | DSI PHY compliant with MIPI DPHY v0.81 specification, not with DSI PHY v1.0                                      |   | -         |  |

| DSI          | 2.14.1  | Generic packet illegally sent between two video packets in command mode                                          | Α | Α         |  |

|              | 2.14.2  | DPI timing mismatch                                                                                              | Α | Α         |  |

|              | 2.14.3  | Video transmission stuck with arrival of generic packet during last line                                         | Α | Α         |  |

|              | 2.16.1  | One-pulse mode trigger not detected in master-slave reset + trigger configuration                                | Р | Р         |  |

| TIM          | 2.16.2  | Consecutive compare event missed in specific conditions                                                          | N | N         |  |

|              | 2.16.3  | Output compare clear not working with external counter reset                                                     | Р | Р         |  |

|              | 2.16.4  | Bidirectional break mode not working with short pulses                                                           | N | N         |  |

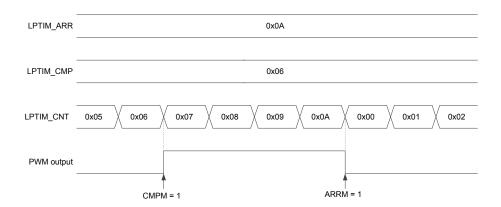

|              | 2.17.1  | Device may remain stuck in LPTIM interrupt when entering Stop mode                                               | Α | Α         |  |

| LPTIM        | 2.17.2  | Device may remain stuck in LPTIM interrupt when clearing event flag                                              | Р | Р         |  |

|              | 2.17.3  | LPTIM events and PWM output are delayed by one kernel clock cycle                                                | Р | Р         |  |

|              | 2.18.1  | Incorrect version register                                                                                       | N | N         |  |

|              | 2.18.2  | Calendar initialization may fail in case of consecutive INIT mode entry                                          | Α | Α         |  |

|              | 2.18.3  | Alarm flag may be repeatedly set when the core is stopped in debug                                               | N | N         |  |

| RTC and TAMP | 2.18.4  | A tamper event fails to trigger timestamp or timestamp overflow events during a few cycles after clearing TSF    |   | N         |  |

|              | 2.18.5  | REFCKON write protection associated to INIT KEY instead of CAL KEY                                               | Α | Α         |  |

|              | 2.18.6  | Tamper flag not set on LSE failure detection                                                                     | N | N         |  |

|              | 2.19.1  | Wrong data sampling when data setup time (t <sub>SU;DAT</sub> ) is shorter than one I2C kernel clock period      | Р | Р         |  |

|              | 2.19.2  | Spurious bus error detection in master mode                                                                      | Α | Α         |  |

| I2C          | 2.19.3  | Spurious master transfer upon own slave address match                                                            | Р | Р         |  |

|              | 2.19.4  | OVR flag not set in underrun condition                                                                           | N | N         |  |

| -            | 2.19.5  | Transmission stalled after first byte transfer                                                                   | Α | Α         |  |

| -            | 2.19.6  | SDA held low upon SMBus timeout expiry in slave mode                                                             | Α | Α         |  |

|              | 2.20.1  | Anticipated end-of-transmission signaling in SPI slave mode                                                      | Α | Α         |  |

|              | 2.20.2  | Data corruption due to noisy receive line                                                                        | Α | Α         |  |

| USART -      | 2.20.3  | Received data may be corrupted upon clearing the ABREN bit                                                       | Α | Α         |  |

|              | 2.20.4  | Noise error flag set while ONEBIT is set                                                                         | N | N         |  |

|              | 2.21.1  | Master data transfer stall at system clock much faster than SCK                                                  | Α | Α         |  |

|              | 2.21.2  | Corrupted CRC return at non-zero UDRDET setting                                                                  | Р | Р         |  |

| SPI          | 2.21.3  | TXP interrupt occurring while SPI disabled                                                                       | Α | Α         |  |

|              | 2.21.4  | Possible corruption of last-received data depending on CRCSIZE setting                                           | Α | Α         |  |

|              | 2.21.5  | Truncation of SPI output signals after EOT event                                                                 | Α | Α         |  |

ES0438 - Rev 8 page 4/56

|                  |         |                                                                                                               |   | itus      |

|------------------|---------|---------------------------------------------------------------------------------------------------------------|---|-----------|

| Function Section |         | Limitation                                                                                                    |   | Rev.<br>Z |

| SDMMC            | 2.22.1  | End-of-buffer status flag not cleared when the last burst data is delayed by the slave                        |   | А         |

|                  | 2.22.2  | The first word of the transfer following a linked list error may be wrong                                     | Α | Α         |

|                  | 2.23.1  | Desynchronization under specific condition with edge filtering enabled                                        | Α | Α         |

| FDCAN            | 2.23.2  | Tx FIFO messages inverted under specific buffer usage and priority setting                                    | Α | А         |

|                  | 2.23.3  | DAR mode transmission failure due to lost arbitration                                                         | Α | Α         |

| OTG_HS           | 2.24.1  | Host packet transmission may hang when connecting the full speed nterface through a hub to a low-speed device |   | N         |

|                  | 2.25.1  | Incorrect L4 inverse filtering results for corrupted packets                                                  | N | N         |

|                  | 2.25.2  | Rx DMA may fail to recover upon DMA restart following a bus error, with Rx timestamping enabled               | Α | А         |

|                  | 2.25.3  | Spurious receive watchdog timeout interrupt                                                                   | Α | Α         |

|                  | 2.25.4  | Incorrect flexible PPS output interval under specific conditions                                              | Α | Α         |

| ETH              | 2.25.5  | Packets dropped in RMII 10 Mbps mode due to fake dribble and CRC error                                        | Α | Α         |

|                  | 2.25.6  | ARP offload function not effective                                                                            | Α | Α         |

|                  | 2.25.7  | Slight imbalance of AV traffic CBS bandwidth allocation                                                       | N | N         |

|                  | 2.25.8  | Spurious checksum error upon MTL pending Tx queue flush                                                       | N | N         |

|                  | 2.25.9  | Bus error coinciding with start-of-packet corrupts MAC-generated packet transmission                          | N | N         |

|                  | 2.25.10 | DMA spurious state upon AXI DMA slave bus error                                                               | Р | Р         |

The following table gives a quick reference to the documentation errata.

Table 4. Summary of device documentation errata

| Function    | Section | Documentation erratum                                  |  |

|-------------|---------|--------------------------------------------------------|--|

| System      | 2.3.11  | SSCG option is not available on PLL3 and PLL4          |  |

| DMA         | 2.6.1   | JSART/UART/LPUART DMA transfer abort                   |  |

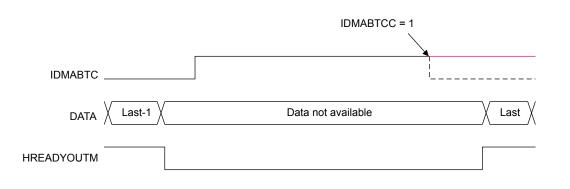

| ПУСП        | 2.15.1  | Superseded suspend sequence for data loaded by DMA     |  |

| HASH 2.15.2 |         | Superseded suspend sequence for data loaded by the CPU |  |

ES0438 - Rev 8 page 5/56

# 2 Description of device errata

The following sections describe the errata of the applicable devices with Arm<sup>®</sup> core and provide workarounds if available. They are grouped by device functions.

Note: Arm is a registered trademark of Arm Limited (or its subsidiaries) in the US and/or elsewhere.

arm

## 2.1 Arm Cortex-A7 core

Reference manual and errata notice for the Arm<sup>®</sup> Cortex<sup>®</sup>-A7 core revision r0p5-REVIDR=0x01 is available from http://infocenter.arm.com. Only applicable information from the Arm errata notice is replicated in this document.

# 2.1.1 Memory locations might be accessed speculatively due to instruction fetches when HCR.VM is

This limitation is registered under Arm ID number 844169 and classified into "Category B". Its impact to the device is minor.

#### **Description**

The ARMv7 architecture requires that when all associated stages of translation are disabled for the current privilege level, memory locations are only accessed due to instruction fetches within the same or next 4 KB region as an instruction which has been or is going to be fetched due to sequential execution. In the conditions detailed below, the Cortex-A7 processor might access other locations speculatively due to instruction fetches.

The unwanted speculative instruction fetches may occur when the following conditions are all met:

- 1. The processor must be executing at PL2 or Secure PL1.

- Address translation is disabled for the current exception level (by clearing the appropriate SCTLR.M or HSCTLR.M bit).

- 3. The HCR.VM bit is set.

As the HCR.VM is reset low, this issue does not manifest during boot code.

#### Workaround

This issue is most likely to arise in powerdown code, if PL2 or secure PL1 software disables address translation before the core is powered down.

To work around this erratum, software should ensure that HCR.VM is cleared before disabling address translation at PL2 or Secure PL1.

### 2.1.2 Cache maintenance by set/way operations can execute out of order

This limitation is registered under Arm ID number 814220 and classified into "Category B". Its impact to the device is limited.

# Description

The ARM v7 architecture states that all cache and branch predictor maintenance operations that do not specify an address execute in program order, relative to each other. However, because of this erratum, an L2 set/way cache maintenance operation can overtake an L1 set/way cache maintenance operation.

Code that intends to clean dirty data from L1 to L2 and then from L2 to L3 using set/way operations might not behave as expected. The L2 to L3 operation might happen first and result in dirty data remaining in L2 after the L1 to L2 operation has completed.

If dirty data remains in L2 then an external agent, such as a DMA agent, might observe stale data.

If the processor is reset or powered-down while dirty data remains in L2 then the dirty data are lost.

ES0438 - Rev 8 page 6/56

The failure occurs when the following conditions are all met:

- 1. A CPU performs an L1 DCCSW or DCCISW operation.

- 2. The targeted L1 set/way contains dirty data.

- 3. Before the next DSB, the same CPU executes an L2 DCCSW or DCCISW operation while the L1 set/way operation is in progress.

- 4. The targeted L2 set/way is within the group of L2 set/ways that the dirty data from L1 can be allocated to. If the above conditions are met then the L2 set/way operation can take effect before the dirty data from L1 has been written to L2.

Note:

Conditions (3) and (4) are not likely to be met concurrently when performing set/way operations on the entire L1 and L2 caches. This is because cache maintenance code is likely to iterate through sets and ways in a consistent ascending or consistent descending manner across cache levels, and to perform all operations on one cache level before moving on to the next cache level. This means that, for example, cache maintenance operations on L1 set 0 and L2 set 0 are separated by cache maintenance operations for all other sets in the L1 cache. This creates a large window for the cache maintenance operations on L1 set 0 to complete.

#### Workaround

Correct ordering between set/way cache maintenance operations can be forced by executing a DSB before changing cache levels.

### 2.1.3 PMU events 0x07, 0x0C, and 0x0E do not increment correctly

This limitation is registered under Arm ID number 809719 and classified into "Category C". Its impact to the device is minor.

## **Description**

The Cortex-A7 processor implements version 2 of the Performance Monitor Unit architecture (PMUv2). The PMU can gather statistics on the operation of the processor and memory system during runtime. This event information can be used when debugging or profiling code.

The PMU can be programmed to count architecturally executed stores (event 0x07), software changes of the PC (event 0x0C), and procedure returns (event 0x0E). However, because of this erratum, these events do not fully adhere to the descriptions in the PMUv2 architecture.

As a result of this limitation, the information returned by PMU counters that are programmed to count events 0x07, 0x0C, or 0x0E might be misleading when debugging or profiling code executed on the processor.

The error occurs when the following conditions are met:

## Either:

- 1. A PMU counter is enabled and programmed to count event 0x07. That is: instruction architecturally executed, condition code check pass, store.

- 2. A PLDW instruction is executed.

If the above conditions are met, the PMUv2 architecture specifies that the counter for event 0x07 does not increment. However, the counter does increment.

#### Or:

- 1. A PMU counter is enabled and programmed to count event 0x0C. That is: instruction architecturally executed, condition code check pass, software change of the PC.

- 2. An SVC, HVC, or SMC instruction is executed.

If the above conditions are met, the PMUv2 architecture specifies that the counter for event 0x0C increments. However, the counter does not increment.

ES0438 - Rev 8 page 7/56

#### Or

- 1. A PMU counter is enabled and programmed to count event 0x0E. That is: instruction architecturally executed, condition code check pass, procedure return.

- 2. One of the following instructions is executed:

```

a. MOV PC, LR

```

- b. ThumbEE LDMIA R9!, {?, PC}

- C. ThumbEE LDR PC, [R9], #offset

- d. BX Rm, where Rm != R14

- e. LDM SP, {?, PC}

If the above conditions are met, the PMUv2 architecture specifies that the counter for event 0x0E increments for (a), (b), (c) and does not increment for (d) and (e). However, the counter does not increment for (a), (b), (c) and increments for (d) and (e).

#### Example:

The processor should execute interrupt handler C, and on completion of handler C should execute the handler for B. If the conditions above are met, then this erratum results in the processor erroneously clearing the pending state of interrupt C, and then executing the handler for B twice. The first time the handler for B is executed is at interrupt C's priority level. If interrupt C is pended by a level-based interrupt which is cleared by C's handler then interrupt C is pended again once the handler for B has completed and the handler for C is executed.

As the STM32 interrupt C is level based, then this interrupt eventually becomes re-pending and subsequently be handled.

#### Workaround

None.

## 2.1.4 PMU event counter 0x14 does not increment correctly

This limitation is registered under Arm ID number 805420 and classified into "Category C". Its impact to the device is minor.

## **Description**

The Cortex-A7 MPCore processor implements version 2 of the Performance Monitor Unit architecture (PMUv2). The PMU can gather statistics on the operation of the processor and memory system during runtime. This event information can be used when debugging or profiling code. When a PMU counter is programmed to count L1 instruction cache accesses (event 0x14), the counter should increment on all L1 instruction cache accesses.

This limitation has the following implications:

- 1. If SCR.{AW, FW} is set to 0 then the clearing of corresponding bit CPSR.{A, F} to 0 has no effect. The value of CPSR.{A, F} is ignored.

- 2. A PMU counter is enabled and programmed to count L1 instruction cache accesses (event 0x14).

- 3. Cacheable instruction fetches miss in the L1 instruction cache.

If the above conditions are met, the event counter does not increment.

# Workaround

To obtain a better approximation for the number of L1 instruction cache accesses, enable a second PMU counter and program it to count instruction fetches that cause linefills (event 0x01). Add the value returned by this counter to the value returned by the L1 instruction access counter (event 0x14). The result of the addition is a better indication of the number of L1 instruction cache accesses.

# 2.1.5 Exception mask bits are cleared when an exception is taken in Hyp mode

This limitation is registered under Arm ID number 804069 and classified into "Category C". Its impact to the device is minor.

## **Description**

The Cortex-A7 processor implements the ARM Virtualization Extensions and the ARM Security Extensions. Exceptions can be routed to Monitor mode by setting SCR.{EA, FIQ, IRQ} to 1. Exceptions can be masked by setting corresponding bit CPSR.{A, I, F} to 1.

ES0438 - Rev 8 page 8/56

The ARMv7-A architecture states that an exception taken in Hyp mode does not change the value of the mask bits for exceptions routed to Monitor mode. However, because of this erratum, the corresponding mask bits are cleared to 0.

The error occurs when the following conditions are met:

- 1. One or more exception types are routed to Monitor mode by setting one or more of SCR.{EA, FIQ, IRQ} to 1.

- 2. The corresponding exception types are masked by setting the corresponding CPSR.{A, F, I} bits to 1.

- 3. Any exception is taken in Hyp mode.

If the above conditions are met then the exception mask bit CPSR.{A, F, I} is cleared to 0 for each exception type that meets conditions (1) and (2). The affected mask bits are cleared together regardless of the exception type in condition (3).

The implications of this erratum are:

- If SCR.{AW, FW} is set to 0 then the clearing of corresponding bit CPSR.{A, F} to 0 has no effect. The

value of CPSR.{A, F} is ignored.

- Otherwise, when CPSR.{A, F, I} is set to 1, Secure code cannot rely on CPSR.{A, F, I} remaining set to 1. An exception that should be masked might be routed to Monitor mode.

The impact of this limitation is considered to be minor as it is expected that the users:

- 1. set SCR.{AW, FW} to 0 when SCR.{EA, FIQ} is set to 1.

- 2. set SCR.IRQ to 0.

#### Workaround

None.

### 2.2 Arm Cortex-M4 core

Reference manual and errata notice for the Arm<sup>®</sup> Cortex<sup>®</sup>-M4 core revision r0p1 is available from http://infocenter.arm.com. Only applicable information from the Arm errata notice is replicated in this document.

#### 2.2.1 Interrupted loads to SP can cause erroneous behavior

This limitation is registered under Arm ID number 752770 and classified into "Category B". Its impact to the device is minor.

#### **Description**

If an interrupt occurs during the data-phase of a single word load to the stack-pointer (SP/R13), erroneous behavior can occur. In all cases, returning from the interrupt will result in the load instruction being executed an additional time. For all instructions performing an update to the base register, the base register will be erroneously updated on each execution, resulting in the stack-pointer being loaded from an incorrect memory location.

The affected instructions that can result in the load transaction being repeated are:

- LDR SP, [Rn],#imm

- LDR SP, [Rn,#imm]!

- LDR SP, [Rn,#imm]

- LDR SP, [Rn]

- LDR SP, [Rn,Rm]

The affected instructions that can result in the stack-pointer being loaded from an incorrect memory address are:

- LDR SP,[Rn],#imm

- LDR SP,[Rn,#imm]!

As compilers do not generate these particular instructions, the limitation is only likely to occur with hand-written assembly code.

#### Workaround

Both issues may be worked around by replacing the direct load to the stack-pointer, with an intermediate load to a general-purpose register followed by a move to the stack-pointer.

ES0438 - Rev 8 page 9/56

### 2.2.2 VDIV or VSQRT instructions might not complete correctly when very short ISRs are used

This limitation is registered under Arm ID number 776924 and classified into "Category B". Its impact to the device is limited.

#### Description

The VDIV and VSQRT instructions take 14 cycles to execute. When an interrupt is taken a VDIV or VSQRT instruction is not terminated, and completes its execution while the interrupt stacking occurs. If lazy context save of floating point state is enabled then the automatic stacking of the floating point context does not occur until a floating point instruction is executed inside the interrupt service routine.

Lazy context save is enabled by default. When it is enabled, the minimum time for the first instruction in the interrupt service routine to start executing is 12 cycles. In certain timing conditions, and if there is only one or two instructions inside the interrupt service routine, then the VDIV or VSQRT instruction might not write its result to the register bank or to the FPSCR.

The failure occurs when the following condition is met:

- 1. The floating point unit is enabled

- 2. Lazy context saving is not disabled

- 3. A VDIV or VSQRT is executed

- 4. The destination register for the VDIV or VSQRT is one of s0 s15

- 5. An interrupt occurs and is taken

- 6. The interrupt service routine being executed does not contain a floating point instruction

- 7. Within 14 cycles after the VDIV or VSQRT is executed, an interrupt return is executed

A minimum of 12 of these 14 cycles are utilized for the context state stacking, which leaves 2 cycles for instructions inside the interrupt service routine, or 2 wait states applied to the entire stacking sequence (which means that it is not a constant wait state for every access).

In general, this means that if the memory system inserts wait states for stack transactions (that is, external memory is used for stack data), then this erratum cannot be observed.

The effect of this erratum is that the VDIV or VQSRT instruction does not complete correctly and the register bank and FPSCR are not updated, which means that these registers hold incorrect, out of date, data.

## Workaround

A workaround is only required if the floating point unit is enabled. A workaround is not required if the stack is in external memory.

There are two possible workarounds:

- Disable lazy context save of floating point state by clearing LSPEN to 0 (bit 30 of the FPCCR at address 0xE000EF34).

- Ensure that every interrupt service routine contains more than 2 instructions in addition to the exception return instruction.

# 2.2.3 Store immediate overlapping exception return operation might vector to incorrect interrupt

This limitation is registered under Arm ID number 838869 and classified into "Category B (rare)". Its impact to the device is minor.

## Description

The core includes a write buffer that permits execution to continue while a store is waiting on the bus. Under specific timing conditions, during an exception return while this buffer is still in use by a store instruction, a late change in selection of the next interrupt to be taken might result in there being a mismatch between the interrupt acknowledged by the interrupt controller and the vector fetched by the processor.

ES0438 - Rev 8 page 10/56

The failure occurs when the following condition is met:

- 1. The handler for interrupt A is being executed.

- 2. Interrupt B, of the same or lower priority than interrupt A, is pending

- 3. A store with immediate offset instruction is executed to a bufferable location.

- STR/STRH/STRB <Rt>, [<Rn>,#imm]

- STR/STRH/STRB <Rt>, [<Rn>,#imm]!

- STR/STRH/STRB <Rt>, [<Rn>],#imm

- 4. Any number of additional data-processing instructions can be executed.

- 5. A BX instruction is executed that causes an exception return.

- 6. The store data has wait states applied to it such that the data is accepted at least two cycles after the BX is executed.

- Minimally, this is two cycles if the store and the BX instruction have no additional instructions between them

- The number of wait states required to observe this erratum needs to be increased by the number of cycles between the store and the interrupt service routine exit instruction.

- 7. Before the bus accepts the buffered store data, another interrupt C is asserted which has the same or lower priority as A, but a greater priority than B.

#### Example:

The processor should execute interrupt handler C, and on completion of handler C should execute the handler for B. If the conditions above are met, then this erratum results in the processor erroneously clearing the pending state of interrupt C, and then executing the handler for B twice. The first time the handler for B is executed it will be at interrupt C's priority level. If interrupt C is pended by a level-based interrupt which is cleared by C's handler then interrupt C will be pended again once the handler for B has completed and the handler for C will be executed.

As the STM32 interrupt C is level based, it eventually becomes pending again and is subsequently handled.

## Workaround

For software not using the memory protection unit, this erratum can be worked around by setting DISDEFWBUF in the Auxiliary Control Register.

In all other cases, the erratum can be avoided by ensuring a DSB occurs between the store and the BX instruction. For exception handlers written in C, this can be achieved by inserting the appropriate set of intrinsics or inline assembly just before the end of the interrupt function, for example:

#### ARMCC:

```

...

_schedule_barrier();

_asm{DSB};

_schedule_barrier();

}

```

#### GCC:

```

asm volatile ("dsb 0xf":::"memory");

}

```

# 2.3 System

### 2.3.1 TPIU fails to output sync after the pattern generator is disabled in Normal mode

## **Description**

The TPIU includes a pattern generator that can be used by external tool to determine the operating behavior of the trace port and timing characteristics. This pattern generator includes a mode that transmits the test pattern for a specified number of cycles, and then reverts to transmitting normal trace data.

When the TPIU is configured to operate in Normal mode (FFCR.EnFCont=0), the synchronization sequence that is required between the test pattern and the trace data is not generated. Synchronization is generated at a later time, as determined by the synchronization counter.

ES0438 - Rev 8 page 11/56

#### Conditions:

The following conditions must all occur:

- The TPIU is configured in normal mode, FFCR.EnFCont==0

- The TPIU is configured with the formatter enabled, FFCR.EnFTC==1

- The pattern generator is enabled in timed mode, Current test pattern mode.PTIMEEN==1

#### Implications:

The timed mode of the TPIU is intended to permit the TPIU to transition between an initial synchronization sequence using the pattern generator and functional mode without any further programming intervention. If the synchronization sequence is not generated at the end of the test pattern, the trace port analyzer is unlikely to be able to capture the start of the trace stream correctly. Synchronization is correctly inserted based on the value configured in the FSCR, once the specified number of frames of trace data have been output.

### Workaround

Workaround requires software interaction to detect the completion of the test pattern sequence. In addition, any trace data present at the input to the TPIU is lost whilst the pattern generator is active. Any trace data present in the input to the TPIU before the formatter is re-enabled (and synchronization generated) is not de-compressible.

- 1. After enabling the pattern generator, set FFCR.StopOnFl==1 and FFCR.FOnMan==1.

- 2. Poll FFSR. FtStopped until 1 is read

- 3. Set FFCR.EnFTC==1

## 2.3.2 Serial-wire multi-drop debug not supported

#### **Description**

The target instance bitfield TINSTANCE[3:0] of the DP\_DLPIDR debug port data link protocol identification register is frozen to 0, which prevents the debug of multiple instances of the same function connected on same SWD bus.

#### Workaround

None.

# 2.3.3 HSE external oscillator required in some LTDC use cases

## **Description**

Due to capacitive load on the LTDC pins, the LTDC used at high or very high speed (OSPEEDR  $\geq$  1) may impact the on-chip HSE crystal oscillator clock, which then could lead to a deterioration of USB HS eye diagram.

Note:

This does not apply when the LTDC is internally connected to the DSI host, even at high clock frequencies up to 90 MHz, as it does not drive pins.

#### Workaround

If using the USB HS interface, avoid using the on-chip HSE oscillator in the use cases summarized in the table. Instead, get the clock from an external oscillator connected to the HSE pins, as indicated in the table (mandatory or recommended).

Table 5. Use of external oscillator on HSE pins

| LTDC connected to | Conditions                                        |                                                         | External oscillator on<br>HSE |

|-------------------|---------------------------------------------------|---------------------------------------------------------|-------------------------------|

|                   |                                                   | 3 V < V <sub>DD</sub> < 3.6 V                           |                               |

| HDMI bridge       | HDMI bridge close to<br>the device<br>load ~15 pf | f <sub>pixel</sub> up to 74.25 MHz (1280x720 at 60 fps) | Mandatory                     |

|                   |                                                   | OSPEEDR = 1 for all LTDC signals                        |                               |

|                   |                                                   | USB HS used                                             |                               |

|                   |                                                   | 1.7 V < V <sub>DD</sub> < 2 V                           | Recommended                   |

ES0438 - Rev 8 page 12/56

| LTDC connected to |                      | External oscillator on HSE                                  |             |

|-------------------|----------------------|-------------------------------------------------------------|-------------|

|                   |                      | f <sub>pixel</sub> up to 74.25 MHz                          |             |

|                   | HDMI bridge close to | Duty cycle = 40 %                                           |             |

| HDMI bridge       | the device           | 0.1 V <sub>DD</sub> < V <sub>IN</sub> < 0.9 V <sub>DD</sub> |             |

|                   | load ~15 pf          | OSPEEDR = 3 for LCD_CLK                                     |             |

|                   |                      | OSPEEDR = 2 for all other LTDC signals                      |             |

|                   |                      | 3 V < V <sub>DD</sub> < 3.6 V                               |             |

|                   |                      | f <sub>pixel</sub> up to 90 MHz (1366x768 at 60 fps)        |             |

|                   |                      | OSPEEDR = 2 for LCD_CLK                                     | Mandatory   |

|                   |                      | OSPEEDR = 1 for all other LTDC signals                      |             |

|                   |                      | USB HS used                                                 |             |

|                   |                      | 3 V < V <sub>DD</sub> < 3.6 V                               |             |

|                   |                      | f <sub>pixel</sub> up to 48 MHz (800x600 at 60 fps)         |             |

| Parallel LCD      | load < 30 pf         | OSPEEDR = 1 for LCD_CLK                                     |             |

|                   |                      | OSPEEDR = 0 for all other LTDC signals                      |             |

|                   |                      | 1.7 V < V <sub>DD</sub> < 2 V                               | Recommended |

|                   |                      | f <sub>pixel</sub> up to 69 MHz (1024x768 at 60 fps)        | Recommended |

|                   |                      | Duty cycle = 40 %                                           |             |

|                   |                      | 0.1 V <sub>DD</sub> < V <sub>IN</sub> < 0.9 V <sub>DD</sub> |             |

|                   |                      | OSPEEDR = 3 for LCD_CLK                                     |             |

|                   |                      | OSPEEDR = 2 for all other LTDC signals                      |             |

### 2.3.4 RCC cannot exit Stop and LP-Stop modes

### **Description**

When trying to exit Stop or LP-Stop mode, the handshake mechanism between PWRCTRL and RCC can be wrong due to a too short internal state within the RCC state machine. In extreme case, the PWRCTRL does not see the RCC signal, thus causing the whole system going to Stop or LP-Stop mode again, respectively.

# Workaround

Set the PWRLP\_DLY[21:0] bitfield of the RCC\_PWRLPDLYCR register to a value equal to or greater than 0x4.

Note: This register is designed to handle LP-Stop mode, but it can also be used in the present case for Stop mode.

## 2.3.5 Incorrect reset of glitch-free kernel clock switch

### **Description**

The activation of NRST (by external signal, internal watchdog or software) may not properly reset the glitch-free clock switches inside the RCC.

As a consequence, the peripheral kernel clock previously used by the application remains selected. If not enabled again (by default or by software), there is no kernel clock present on the related peripheral and the BootROM hangs.

Note:

The USB boot is usually not affected as the application always uses the same clocking scheme depending on the HSE crystal frequency choice. For example, there is no issue for HSE at 24 MHz as hse\_ker\_ck is used for clocking OTG. Other peripherals, such as LPTIM, USART, and I2C, work without care if the previous application clock is enabled again to ensure that the clock switch is not stuck.

ES0438 - Rev 8 page 13/56

#### Workaround

Apply one of the following measures:

- 1. By hardware, ensure that the  $V_{\mbox{\scriptsize DDCORE}}$  logic is reset on NRST activation:

- With STPMIC1

- By default, a power cycle on V<sub>DDCORE</sub> (and V<sub>DD</sub>) is issued upon activating NRST.

- Without STPMIC1

- Connect NRST to NRST\_CORE (in case  $V_{DD}$  is below 2.745V, connection should be done using a capacitor with a value of 1/10th of the capacitor value present between NRST and GND, ensure also that potential capacitors between NRST\_CORE to GND are removed).

The drawback is that, the debug logic also being reset, it is not possible to debug the boot chain (TF-A and U-Boot) as any breakpoints set are lost during the power cycle or NRST CORE activation.

#### 2. By software:

- For interfaces required during boot, whether Flash memory peripherals (SDMMC1/2, QUADSPI, or FMC) or USART/UART (USART2/3/6 or UART4/5/7/8), use the same clock as the one used during the BootROM execution:

- If BOOT[2:0] = 000 or 110 (UART boot), set UARTxxSRC[2:0] to 0 (pclk) or 2 (hsi\_ker\_ck), for all UART instances not disabled via uart intances disabled bitfield of the BSEC OTP WORD 3.

- If BOOT[2:0] = 001 or 111 (QUADSPI boot), set QSPISRC[2:0] to 0 (aclk) or 3 (per\_ck).

- If BOOT[2:0] = 010 or 101 (SDMMC boot), set SDMMC12SRC[2:0] to 0 (hclk6) or 3 (hsi ker ck).

- For SD card, the use of HSI (64 MHz) causes raw bandwidth performance penalty as only 32 or 64 MHz could be used instead of respectively 50 MHz (SDR25/DDR50) and 100 MHz (SDR50)

- For eMMC, the use of HSI (64 MHz) causes raw bandwidth performance penalty as only 32 or 64 MHz could be used instead of respectively 52 MHz (SDR/DDR) or over 100 MHz (HS200). Note that hclk6/hclk5/aclk are limited to 200 MHz when hclk6 is used as SDMMC1/SDMMC2 kernel clock

- If BOOT[2:0] = 011 (FMC boot), set FMCSRC[2:0] to 0 (aclk) or 3 (per\_ck)

## 2.3.6 Limitation of aclk/hclk5/hclk6 to 200 MHz when used as SDMMC1/2 kernel clock

## Description

The SDMMC1 and SDMMC2 kernel clock is limited to 200 MHz whereas hclk6 maximum frequency is 266 MHz. As a consequence, when SDMMC12SRC[2:0] = 0 (hclk6), the AXI bus clock (aclk), AHB5 bus clock (hclk5), and AHB6 bus clock (hclk6) cannot exceed 200 MHz.

#### Workaround

Apply one of the following measures:

- When SDMMC12SRC[2:0] = 0, limit aclk/hclk5/hclk6 to 200 MHz.

- Use another SDMMC1/SDMMC2 kernel clock source, that is, set SDMMC12SRC[2:0] to 1, 2, or 3.

## 2.3.7 Overconsumption in Standby with on-board 1.8 V regulator bypassed

## Description

The device directly supplied from 1.8 V applied on the VDDA1V8\_REG pin (with the on-board regulator bypassed by connecting BYPASS\_REG1V8 to  $V_{DD}$ ) exhibits an overconsumption of about 900  $\mu$ A in Standby mode (with the  $V_{DDCORE}$  supply shutdown) or when NRST\_CORE is active, due to an excessive leakage through the VDDA1V8 REG pin.

#### Workaround

Shut the VDDA1V8\_REG pin supply down during Standby, either using a power switch between VDD and VDDA1V8\_REG pins or a dedicated voltage regulator with shutdown command connected to an OR combination (for example using diodes) of PWR\_ON and NRST signals.

ES0438 - Rev 8 page 14/56

#### 2.3.8 eMMC boot timeout too short

#### **Description**

Direct boot from eMMC device (BootROM code execution directly followed by eMMC boot code execution) may fail, due to eMMC timeout detected during the BootROM code execution, causing a fallback to serial/USB boot selection.

The issue occurs if after the reset command (CMD0 followed with 0xF0F0F0F0), the JESD84-B51 boot operation (CMD kept low for over 74 clock cycles), and ACK receipt, the eMMC device does not respond with boot partition data within 10 ms (time allowed by the BootROM code).

#### Workaround

For direct boot, use an eMMC device that meets the required timing. Consult the eMMC device vendor if it is necessary for assessing the robustness of the solution with their eMMC. As an indication, Toshiba THGBMNG5D1LBAIL, THGBMDG5D1LBAIL, and Kingston EMMC04G-M627-X03U (all 4 Gbyte devices) appear to operate correctly on the STM32MP157C-EV1 board.

Alternatively, use another kind of Flash memory device, such as SD-card, serial-NOR, serial-NAND, or SLC-NAND, to house a part of the boot code to execute directly after the BootROM code, and to be followed by a second part of the boot code housed in the eMMC device.

### 2.3.9 Cortex-M4 cannot use I/O compensation on Standby mode exit

#### **Description**

As the CSION bit of the RCC\_OCENSETR register is secured upon exiting Standby mode, the Cortex-M4 core cannot enable the CSI oscillator required for activating the I/O compensation function and thus for enabling high-speed I/O operation of Cortex-M4 peripherals. The Cortex-A7 secure core can set the CSION bit but it is not systematically woken up upon exiting Standby mode.

## Workaround

For I/Os of Cortex-M4 peripherals required on Standby exit and until CSI is started by the Cortex-A7 core, only use IOSPEEDR[1:0] settings 00 and 01 (as they do not require I/O compensation).

## 2.3.10 Missed wake-up events in CSTANDBY

#### **Description**

While the Cortex-A7 core is in CSTANDBY mode, WWDG (EXTI event 68) or Cortex-M4 reset (EXTI event 73) wake-up event may cause the RCC state to change faster than the state of PWR. As a consequence, the Cortex-A7 core does not wake up.

## Workaround

None.

## 2.3.11 SSCG option is not available on PLL3 and PLL4

### **Description**

Some reference manual revisions may omit the information that the spread-spectrum clock generation feature is not available on PLL3 and PLL4. The bits RCC\_PLL3CR and RCC\_PLL4CR of the SSCG\_CTRL register must be kept at zero. The registers RCC\_PLL3CSGR and RCC\_PLL4CSGR must not be used.

This is a documentation issue rather than a device limitation.

## Workaround

Assuming that this instruction is followed, no application workaround is required.

ES0438 - Rev 8 page 15/56

## 2.3.12 RCC security settings for Cortex-M4 access are not kept upon wake up from Standby

#### **Description**

When the Cortex-M4 core wakes up from Standby, the TZEN and MCKPROT bits of the RCC\_TZCR register are set high as by default, regardless their previous settings upon entering Standby. Until the Cortex-A7 core is started, the operation of the device is limited as follows:

- Some RCC settings are not accessible.

- None of HSE, CSI, LSI, and PLL3 can be started.

- The only possible Cortex-M4 core clock source is HSI (64MHz).

- The only possible per clk is HSI.

- HSI cannot be set to keep running when Cortex-M4 core goes in CSTOP. (The HSIKERON bit is not accessible.)

- Peripherals secured by default cannot be accessed by the Cortex-M4 core.

- Only PLL4 on HSI is usable for peripherals having a PLL output as clock source option.

#### Workaround

None

## 2.3.13 Wakeup pin flags cleared at Standby mode exit with MCU\_BEN high and MPU\_BEN low

#### **Description**

Upon Standby mode exit while the MCU\_BEN bit is high and the MPU\_BEN bit low, all wakeup flags in the PWR WKUPFR register are unduly cleared, which prevents the detectability of the wakeup source.

#### Workaround

None.

## 2.3.14 Boundary scan data unduly sampled on TCK falling edge

#### Description

In Boundary scan mode, the TDI input is sampled on the falling edge of TCK, which is contrary to the IEEE1149.1 requirements and to the device JTAG timing specifications. Depending on the timing of the signal received on the TDI input, this leads to a risk of data corruption/shift. Other JTAG or SWD modes, such as debug, are exempt of this limitation. The TDO timing is not affected, either.

### Workaround

Ensure that the input signal on the TDI pin holds for at least 1 ns after the TCK falling edge.

Note: The BSDL description file provided takes into account this design issue and adds a dummy cycle.

## 2.3.15 Boundary scan SAMPLE/PRELOAD behavior not compliant with IEE1149.1

## **Description**

IEEE1149.1 expects the SAMPLE/PRELOAD instruction to be non-invasive. In the device however, it behaves as an EXTEST instruction, instead. This potentially causes the scanned pins to toggle to levels unsafe from the application perspective.

### Workaround

Do not use SAMPLE/PRELOAD instruction. Instead, use the specific CUSTOM\_HIGHZ instruction (00011) that allows safe sampling of the pins, by setting them into high-Z state during the sampling phase.

Note:

During the board reset phase (for example during the power-up, when NRST is driven low), all the scannable pins are set to high-Z state. This requires a safe board design ensuring defined pin levels where applicable, for example through the use of pull-up or pull-down resistors.

ES0438 - Rev 8 page 16/56

## 2.3.16 Boot with a specific combination of NAND Flash memories fails

#### **Description**

The boot process fails in the following configuration:

- SLC NAND Flash memory on FMC is set as the primary boot source (OTP WORD3[29:27] = 001).

- An SLC NAND Flash memory is present and empty (or with only corrupted binary headers).

- Serial NAND Flash memory is set as secondary boot source (OTP WORD3[26:24] = 101).

#### Workaround

None.

#### 2.3.17 Boot with 1-bit error correction on SLC NAND Flash memory fails

## **Description**

With an SLC NAND Flash memory with 1-bit Hamming ECC (either ONFI-compliant Flash memory or 1-bit Hamming ECC set via the OTP WORD9), connected through the FMC, the BootROM code unduly reads the three *Hamming 1-bit ECC* bytes in a reverse order with respect to their programming order. As a result, the ECC signals data corruption and the boot systematically fails.

#### Workaround

Apply one of the following measures:

- In the OTP WORD9, set the fmc\_ecc\_bit\_nb[2:0] bitfield to 010 (BCH4) instead to 001 (Hamming). Set all the other bitfields in accordance with the parameters of the SLC NAND Flash memory used.

- Program the three ECC bytes of the SLC NAND Flash memory spare array in the reverse order.

#### Caution:

If applied to a device version not impacted by the issue, the latter measure causes the boot process to fail.

#### 2.3.18 Boot fails if eMMC does not answer the first command

#### **Description**

If an eMMC does not answer (for example, because it is not yet powered) the first command sent to CMD line, the boot routine remains in an infinite loop with no timeout, which causes the boot process to fail.

#### Workaround

None.

# 2.3.19 DLYB limits SDMMC throughput

## **Description**

When DLYB is used SDMMC could exhibit FIFO underrun or overrun due to internal resynchronization and buffering limitation. This is seen on eMMC HS200 mode, on SD-Card SDR50, and SDR104 mode.

### Workaround

Do not use DLYB. With eMMC, use up to DDR mode (52 MHz clock, 104 MBytes/s), with SD-Card, use up to DDR50 (50 MHz clock, 50 MBytes/s).

## 2.3.20 LSE CSS cannot be used in VBAT state

# **Description**

Under certain circumstances, switching  $V_{SW}$  from VDD to VBAT and vice-versa, could falsely trigger the LSE CSS. This would stop the RTC clock, generate false tamper detection and result in the unwanted deletion of the BKPSRAM or Backup REG.

ES0438 - Rev 8 page 17/56

#### Workaround

Do not enable LSE CSS when VBAT mode is planned to be used.

## 2.3.21 Wrong value in Coresight M4 ROM table

#### **Description**

CM4ROM\_PIDR4 and CM4ROM\_PIDR0 ROM tables are wrongly defined to 0x04 and 0x50 respectively whereas they should be set to 0x05 and 0x00 respectively. This only impacts the debugging tools which normally identify the target using this ROM table.

### Workaround

Use DBGMCU IDC to identify the device.

# 2.3.22 Improper isolation of protected secure resources

## **Description**

Refer to technical note TN1500.

#### Workaround

Refer to technical note TN1500.

## 2.3.23 LSE crystal oscillator may be disturbed by transitions on PC13

#### Description

The LSE crystal oscillator clock frequency can be incorrect when PC13 is toggling in input or output (for example when used for RTC OUT1).

The external clock input (LSE bypass) is not impacted by this limitation.

## Workaround

None.

Avoid toggling PC13 when LSE is used.

## 2.4 DDRPHYC

# 2.4.1 DDRPHYC overconsumption upon reset or Standby mode exit

# **Description**

Upon reset and upon Standby mode exit, DDRPHY DLLs are not properly disabled, which leads to leakage on the DDR\_ZQ pin causing excessive consumption from  $V_{DDCORE}$ . Once DDRPHYC is initialized for normal DDR usage, the consumption becomes as specified and remains as specified during Stop modes.

There is no DDRPHYC overconsumption in Standby mode.

#### Workaround

Prevent the leakage on the DDR\_ZQ pin, by first enabling DDRPHYC in the RCC, then setting the ZQPD bit of the DDRPHYC\_ZQ0CR0 register.

ES0438 - Rev 8 page 18/56

# 2.4.2 DDR\_CLK jitter out of JEDEC requirement for 32-bit LPDDR2/LPDDR3 at low device Tj

#### **Description**

At extreme low junction temperatures close to -40°C, the JEDEC JESD209-2B and JESD209-3F (for LPDDR2 and LPDDR3, resp.) maximum allowed jitter specification  $t_{JIT(per)}$  of ±90 ps at 533 MHz may not be respected when operating with 32-bit LPDDR2 or LPDDR3 memory devices, despite respecting the design rules as per the AN5122 application note and despite optimizing the PCB routing for signal integrity.

#### Workaround

Use one of the following measures or their combination:

Increase V<sub>DDQ\_DDR</sub>/V<sub>DDQ</sub>/V<sub>DDQ</sub>/V<sub>DDCA</sub> memory I/O supply (to, for example, 1.25 V).

The use of 16-bit LPDDR2/LPDDR3 memory devices prevents the issue.

Increase the drive output impedance Z0 to 53 Ω, by setting the ZPROG[3:0] bitfield of the DDRPHYC\_ZQ0CR1 register to 0x8.

# 2.4.3 Data corruption at low device T<sub>i</sub> combined with low 32-bit LPDDR2/LPDDR3 I/O supply voltage

### **Description**

Very low device junction temperature (such as below -20°C) increases the risk of data corruption for accesses to 32-bit LPDDR2/LPDDR3 memory with low I/O supply voltage (V<sub>DDQ\_DDR</sub>/V<sub>DDQ</sub>/V<sub>DDQ</sub>/V<sub>DDQ</sub>A), such as 1.2 V or less. The lower the device junction temperature and the memory I/O supply voltage, the higher the risk.

Note:

#### Workaround

Ensure that the operating conditions of the end volume product are never worse, in terms of the device junction temperature and the LPDDR2/LPDDR3 memory I/O supply voltage, than the conditions applied in the (successful) product engineering and qualification stages. In particular, ensure that the memory I/O supply voltage always exceeds 1.2 V. Alternatively, use a 16-bit LPDDR2/LPDDR3 memory device.

## 2.5 GPIO

# 2.5.1 GPIO assigned to DAC cannot be used in output mode when the DAC output is connected to on-chip peripheral

## **Description**

When a DAC output is connected only to an on-chip peripheral, the corresponding GPIO is expected to be available as an output for any other functions.

However, when the DAC output is configured for on-chip peripheral connection only, the GPIO output buffer remains disabled and cannot be used in output mode (GPIO or alternate function). It can still be used in input or analog mode.

This limitation applies to DAC1 OUT1 and DAC1 OUT2 connected to PA4 and PA5, respectively.

#### Workaround

None.

ES0438 - Rev 8 page 19/56

## 2.6 DMA

#### 2.6.1 USART/UART/LPUART DMA transfer abort

### **Description**

Some reference manual revisions may unduly present the bit 20 (TRBUFF in the corrected revisions) of the DMA\_SxCR register as reserved, to be kept at reset value (low). This bit must be set to ensure the completion of USART/UART/LPUART DMA transfer when another DMA transfer is requested concurrently. Otherwise, it may occur that the other DMA transfer request is not served and that it leads to aborting the ongoing USART/UART/LPUART DMA transfer.

This is a documentation issue rather than a device limitation.

#### Workaround

No application workaround is required if the TRBUFF bit is used as indicated.

## 2.7 DMAMUX

### 2.7.1 SOFx not asserted when writing into DMAMUX\_CFR register

#### **Description**

The SOFx flag of the DMAMUX\_CSR status register is not asserted if overrun from another DMAMUX channel occurs when the software writes into the DMAMUX\_CFR register.

This can happen when multiple DMA channels operate in synchronization mode, and when overrun can occur from more than one channel. As the SOFx flag clear requires a write into the DMAMUX\_CFR register (to set the corresponding CSOFx bit), overrun occurring from another DMAMUX channel operating during that write operation fails to raise its corresponding SOFx flag.

## Workaround

None. Avoid the use of synchronization mode for concurrent DMAMUX channels, if at least two of them potentially generate synchronization overrun.

## 2.7.2 OFx not asserted for trigger event coinciding with last DMAMUX request

### **Description**

In the DMAMUX request generator, a trigger event detected in a critical instant of the last-generated DMAMUX request being served by the DMA controller does not assert the corresponding trigger overrun flag OFx. The critical instant is the clock cycle at the very end of the trigger overrun condition.

Additionally, upon the following trigger event, one single DMA request is issued by the DMAMUX request generator, regardless of the programmed number of DMA requests to generate.

The failure only occurs if the number of requests to generate is set to more than two (GNBREQ[4:0] > 00001).

#### Workaround

Make the trigger period longer than the duration required for serving the programmed number of DMA requests, so as to avoid the trigger overrun condition from occurring on the very last DMA data transfer.

## 2.7.3 OFx not asserted when writing into DMAMUX\_RGCFR register

## **Description**

The OFx flag of the DMAMUX\_RGSR status register is not asserted if an overrun from another DMAMUX request generator channel occurs when the software writes into the DMAMUX\_RGCFR register. This can happen when multiple DMA channels operate with the DMAMUX request generator, and when an overrun can occur from more than one request generator channel. As the OFx flag clear requires a write into the DMAMUX\_RGCFR register (to set the corresponding COFx bit), an overrun occurring in another DMAMUX channel operating with another request generator channel during that write operation fails to raise the corresponding OFx flag.

ES0438 - Rev 8 page 20/56

#### Workaround

None. Avoid the use of request generator mode for concurrent DMAMUX channels, if at least two channels are potentially generating a request generator overrun.

# 2.7.4 Wrong input DMA request routed upon specific DMAMUX\_CxCR register write coinciding with synchronization event

#### Description

If a write access into the DMAMUX\_CxCR register having the SE bit at zero and SPOL[1:0] bitfield at a value other than 00:

- sets the SE bit (enables synchronization),

- modifies the values of the DMAREQ\_ID[5:0] and SYNC\_ID[4:0] bitfields, and

- does not modify the SPOL[1:0] bitfield,

and if a synchronization event occurs on the previously selected synchronization input exactly two AHB clock cycles before this DMAMUX\_CxCR write, then the input DMA request selected by the DMAREQ\_ID[5:0] value before that write is routed.

#### Workaround

Ensure that the SPOL[1:0] bitfield is at 00 whenever the SE bit is 0. When enabling synchronization by setting the SE bit, always set the SPOL[1:0] bitfield to a value other than 00 with the same write operation into the DMAMUX CxCR register.

### 2.8 FMC

## 2.8.1 NOR Flash memory/PSRAM incorrect bus turnaround timing

### **Description**

The delays between consecutive device accesses, programmed through the BUSTURN[3:0] bitfield of the FMC BTRx and FMC BWTRx registers, have no effect. Instead systematic delays are applied:

- t<sub>IDI F2</sub>: 2 \* fmc ker ck cycles between accesses to two NOR/PSRAM devices

- t<sub>IDLE1</sub>: 1 \* fmc\_ker\_ck cycle between accesses to a NOR/PSRAM and a NAND Flash memory

## Workaround

Extend the bus turnaround delays to satisfy bus turnaround constraints. Three cases need to be considered:

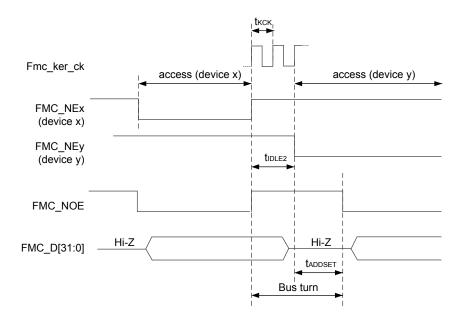

- Two consecutive accesses to non-multiplexed NOR/PSRAM devices: Program t<sub>ADDSET</sub> (NOR/PSRAM address setup phase) as needed (see Figure 1).

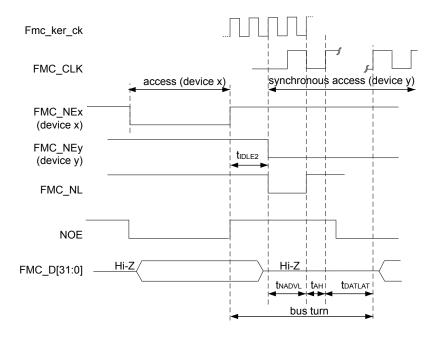

- Access to a non-multiplexed NOR/PSRAM followed by an access either to a NOR/PSRAM device with multiplexed A/DQ signals or to a synchronous device:

Decrease the FMC kernel clock frequency in order to meet the timing constraints (see Figure 2).

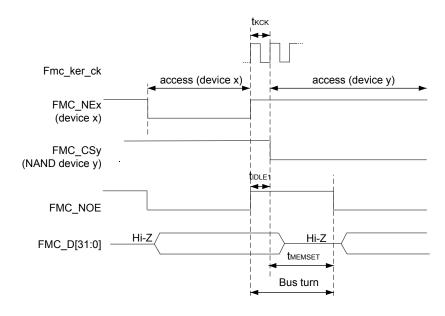

- 3. Access to a non-multiplexed NOR/PSRAM followed by an access to a NAND Flash memory device Program t<sub>MEMSET</sub> (NOR/PSRAM address setup phase) as needed (see Figure 3).

ES0438 - Rev 8 page 21/56

Figure 1. Bus turn timing recovery - asynchronous accesses to NOR/PSRAM devices (case 1)

Figure 2. Bus turn timing recovery - access to NOR/PSRAM followed by access to multiplexed A/DQ synchronous device (case 2)

DT69550V1

DT69551\

ES0438 - Rev 8

DT69552V1

Figure 3. Bus turn timing recovery - access to NOR/PSRAM followed by access to NAND Flash device (case 3)

Table 6 gives the internal latencies that are not mentioned in the product datasheets. Refer to the datasheets for more details about the others timing values.

Table 6. Timing parameter description

| Parameter            | Description                                                   | Minimum value                        |

|----------------------|---------------------------------------------------------------|--------------------------------------|

| t <sub>KCK</sub>     | FMC kernel clock period                                       | See product datasheet                |

| t <sub>IDLE1</sub>   | NEx high to CSy low (switching to a NAND Flash memory device) | 1 * t <sub>KCK</sub>                 |

| t <sub>IDLE2</sub>   | NEx high to NEy low (NOR/PSRAM devices)                       | 2 * t <sub>KCK</sub>                 |

| t <sub>ADDSET</sub>  | NOR/PSRAM address setup phase                                 | See Ref. Man.                        |

| † <sub>NADVL</sub>   | Address valid low pulse duration in synchronous mode          | (CLKDIV+1) * t <sub>KCK</sub>        |

| t <sub>AH</sub>      | Address hold in synchronous mode                              | ((CLKDIV+1) * t <sub>KCK</sub> ) / 2 |

| t <sub>DATLAT</sub>  | NOR/PSRAM data latency in synchronous mode                    | See product datasheet                |

| t <sub>MEMxSET</sub> | NAND Flash memory address setup phase                         | See product datasheet                |

# 2.8.2 Incorrect FMC\_CLK clock period when CLKDIV value is changed on-the-fly in Continuous clock mode

# **Description**

When the FMC operates in Continuous clock mode (CCLKEN is set in FMC\_BCRx register), a new clock division factor is applied by changing the value of CLKDIV[3:0] in FMC\_CFGR while the FMC is disabled (FMCEN cleared in FMC\_BCRx), there is one FMC\_CLK clock cycle during which the FMC\_CLK period is not as expected: for example the clock low pulse duration matches the previous CLKDIV[3:0] value whereas the clock high pulse duration matches the new CLKDIV[3:0] value.

ES0438 - Rev 8 page 23/56

#### Workaround

Use the following sequence:

- 1. Stop the memory traffic for all devices.

- 2. Disable the FMC (refer to the disabling sequence described in the product reference manual).

- 3. Change CCLKEN for 1 to 0 in the FMC BCRx register to stop the clock generation.

- 4. Program the desired CLKDIV[3:0] value in the FMC\_CFGR register.

- 5. Change back CCLKEN from 0 to 1.

- 6. Enable the FMC.

## 2.8.3 NAND Flash memory IREF/IFEF flags wrongly asserted just after enabling in FMC\_IER

#### **Description**

When the application enables interrupt rising edge/falling edge detection (IREE/IFEE set in FMC\_IER register) while the corresponding IREF/IFEF status flag is already set in FMC\_ISR register due to a previous event, then a spurious interrupt is immediately generated, corresponding to an out-of-date event.

#### Workaround

Clear the FMC\_ISR flags before programming FMC\_IER register.

# 2.8.4 Command sequencer accesses NAND Flash memory device while PBKEN bit is cleared in FMC\_PCR

# **Description**

When the PBKEN bit is cleared in FMC\_PCR register, the FMC should discard all accesses from the system to an external NAND Flash memory device. However, the command sequencer can access NAND memory devices if it is accidentally enabled by setting CSQSTART bit in FMC\_CSQCR register.

Please note that AXI commands and data are discarded as expected (returning a bus error)

## Workaround

Deactivate the NAND Flash command sequencer to avoid unwanted accesses to NAND Flash memory devices when PBKEN is dynamically cleared during application execution.

## 2.8.5 NAND Flash memory IREF flag wrongly asserted after reset

#### **Description**

The FMC NAND Flash memory Ready/Busy input signal (RNB) is asserted when the FMC is under reset. If RNB remains high when the FMC reset is released., the IREF status flag is set in the FMC status register (FMC\_SR) thus triggering a spurious interrupt.

#### Workaround

Clear the FMC status register (FMC\_SR) after the FMC reset release.

## 2.8.6 NAND ECC corrupted due to insufficient ECCEN low period in between sectors

#### Description

When the FMC processes multiple NAND Flash memory sectors with Hamming ECC computation, the ECCEN bit of the FMC\_PCR register is cleared after the current sector and set back before the next sector. The computed ECC may be corrupted if the ECCEN bit low period in between sectors is too short to be sampled correctly.

#### Workaround

By software, ensure that between sectors, the ECCEN bit remains low for at least 1.5 kernel clock periods.

ES0438 - Rev 8 page 24/56

### 2.9 QUADSPI

## 2.9.1 Memory-mapped read of last memory byte fails

## **Description**

Regardless of the number of I/O lines used (1, 2 or 4), a memory-mapped read of the last byte of the memory region defined through the FSIZE[4:0] bitfield of the QUADSPI\_DCR register always yields 0x00, whatever the memory byte content is. A repeated attempt to read that last byte causes the AXI bus to stall.

#### Workaround

Apply one of the following measures:

- Avoid reading the last byte of the memory region defined through FSIZE, for example by taking margin in FSIZE bitfield setting.