#### MAX98372

## Digital Input Class D Amplifier with DHT and Brownout Protection

#### **General Description**

The MAX98372 is a high-efficiency, mono Class D audio amplifier featuring dynamic headroom tracking (DHT) and brownout protection. DHT automatically optimizes the headroom available to the Class D amplifier as the power supply voltage varies, due to sudden transients and declining battery life to maintain a consistent listening experience. A wide 5.5V to 18V supply range allows the device to reach 19W into an  $8\Omega$  load.

The MAX98372's flexible digital audio interface (DAI) supports I<sup>2</sup>S, left-justified, and TDM formats. The digital audio interface accepts 32kHz, 44.1kHz, 48kHz, 88.2kHz, and 96kHz sample rates with 16-/24-/32-bit data supported for all data formats. In TDM mode, the device can support up to 16 channels of audio data. A unique clocking structure eliminates the need for an external MCLK signal that is typically needed for PCM communication. This reduces pin count and simplifies board layout.

Active emissions limiting with edge rate control minimizes EMI and eliminates the need for output filtering found in traditional Class D devices.

An 8-bit PVDD supply voltage ADC enables the dynamic headroom tracking circuit. DHT optimizes audio program peak behavior as the supply voltage varies and provides flexible user-defined parameters.

Thermal foldback protection ensures robust behavior when the thermal limits of the device are exercised. The circuit can be enabled to automatically reduce the output power above a user specified temperature. This allows for uninterrupted music playback even at high ambient temperatures. Traditional thermal protection is also available in addition to robust overcurrent protection.

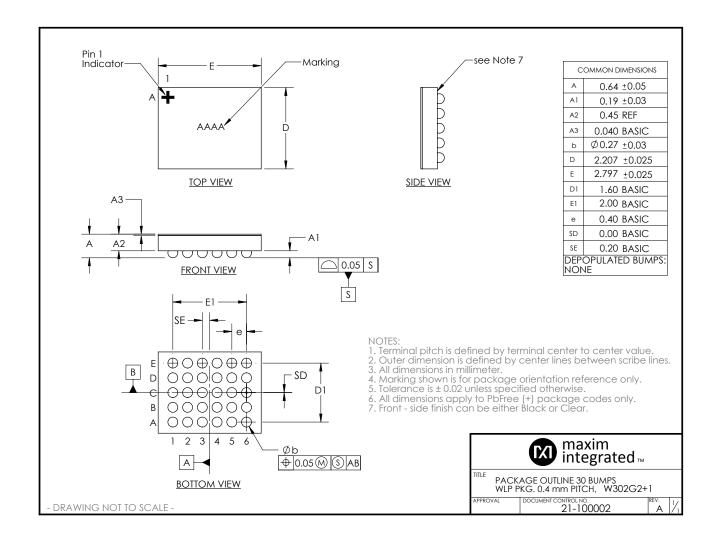

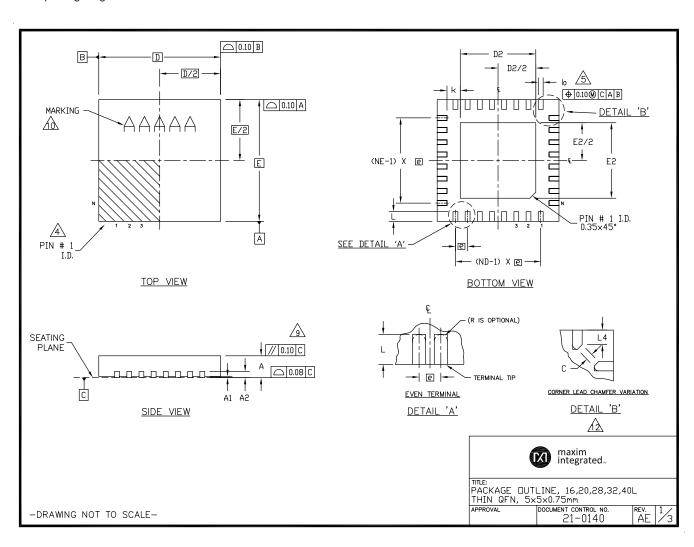

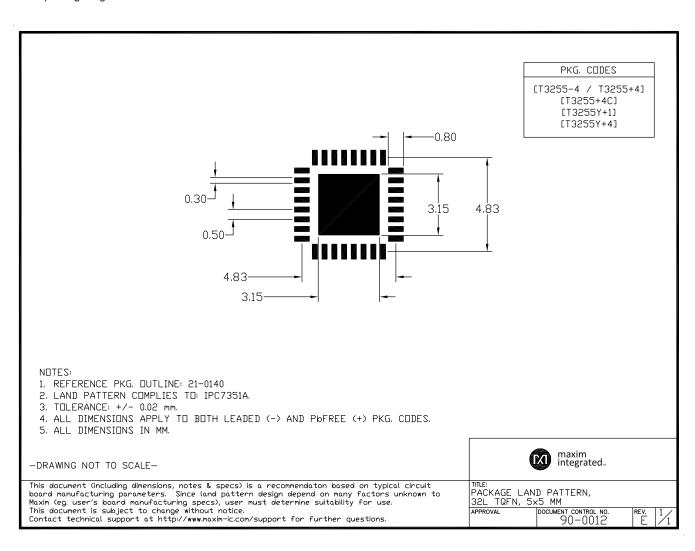

All MAX98372 control is performed using a standard 2-wire, I<sup>2</sup>C interface. One of sixteen slave addresses can be selected through two, four-level address pins. The IC is available in a 0.4mm pitch, 30-bump WLP and 32-pin TQFN packages. It is specified over the extended, -40°C to +85°C temperature range.

#### **Applications**

- Tablets

- Notebook Computers

- Soundbars

#### **Benefits and Features**

- Wide Supply Range (5.5V to 18V)

- Dynamic Headroom Tracking Maintains a Consistent Listening Experience

- Integrated Thermal Foldback Allows Robust Operation in a WLP Package

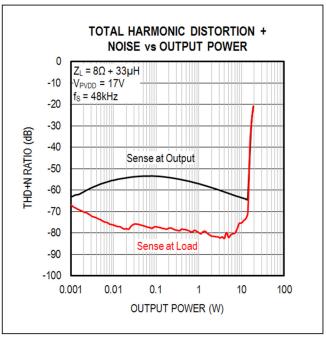

- Remote Output Sensing Allows Up to 20dB THD+N Improvement When Ferrites Are Used

- Class D Edge Rate Control Enables Filterless Operation

- 110dB A-Weighted Dynamic Range

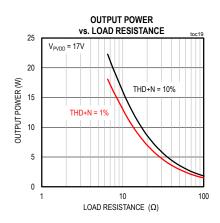

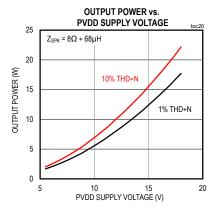

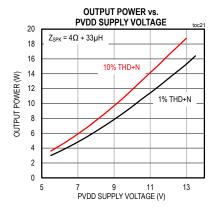

- Output Power at 1% THD+N:

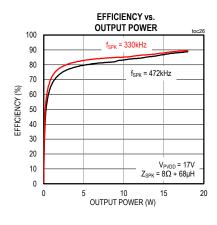

- 15.7W into 8Ω, V<sub>PVDD</sub> = 17V

- 13.2W into 4Ω, V<sub>PVDD</sub> = 12V

- Output Power at 10% THD+N

- 19W into 8Ω, V<sub>PVDD</sub> = 17V

- 15.8W into 4Ω, V<sub>PVDD</sub> = 12V

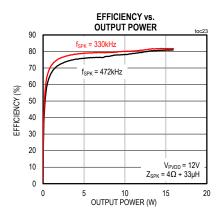

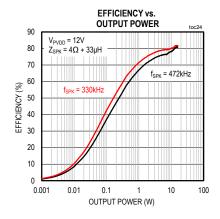

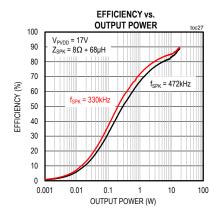

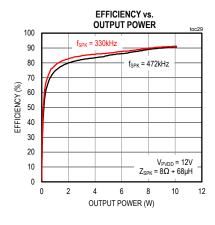

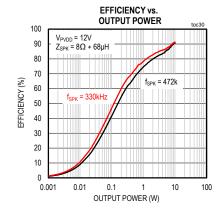

- Speaker Amplifier Efficiency

- 91% at 10W into 8Ω, V<sub>PVDD</sub> = 12V

- 81% at 15W into 4Ω, V<sub>PVDD</sub> = 12V

- ALC Provides Battery Brownout Protection

- Extensive Click-and-Pop Suppression

- 30-Bump, 0.4mm WLP and 32-Pin TQFN Packages

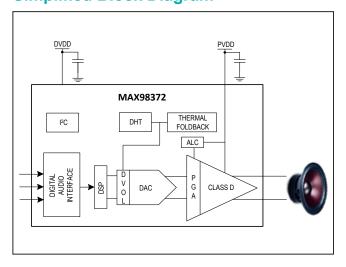

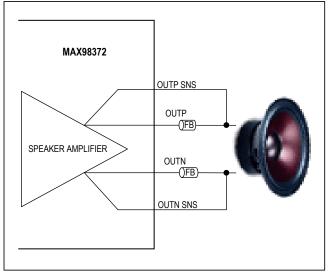

#### **Simplified Block Diagram**

Ordering Information appears at end of data sheet.

#### **TABLE OF CONTENTS**

| General Description                     |  |

|-----------------------------------------|--|

| Applications                            |  |

| Benefits and Features                   |  |

| Simplified Block Diagram                |  |

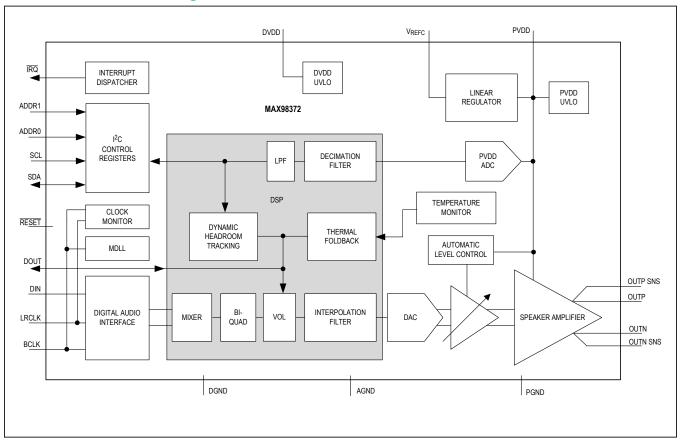

| Detailed Functional Diagram             |  |

| Absolute Maximum Ratings                |  |

| Package Thermal Characteristics         |  |

| Electrical Characteristics              |  |

| I <sup>2</sup> C Timing Characteristics |  |

| Typical Operating Characteristics       |  |

| Bump/Pin Configurations                 |  |

| Bump/Pin Description                    |  |

| Detailed Description                    |  |

| Interrupts                              |  |

| Status                                  |  |

| State                                   |  |

| Flag                                    |  |

| Enable                                  |  |

| Clear                                   |  |

| Digital Audio Interface                 |  |

| Interface Format                        |  |

| Configuring the DAI Format              |  |

| Configuring the Digital Audio Input     |  |

| Digital Passband Filtering              |  |

| Biquad Filter                           |  |

| Signal Path Delay                       |  |

| PVDD ADC                                |  |

| Digital Volume Control                  |  |

| Output Voltage Scaling                  |  |

| Dynamic Headroom Tracking               |  |

| DHT Ballistics                          |  |

| Limiter                                 |  |

| Thermal ADC                             |  |

| Thermal Protection                      |  |

| Thermal Foldback                        |  |

| Automatic Level Control (ALC)           |  |

| TABLE OF CONTENTS (continued)                |     |

|----------------------------------------------|-----|

| DOUT Operation and Data format               |     |

| Interchip Communication                      |     |

| Multiamplifier Grouping                      |     |

| Double Data Drive                            |     |

| Class D Output Stage                         |     |

| Ultra-Low EMI Filterless Output Stage        | 84  |

| V <sub>DVDD</sub> and V <sub>PVDD</sub> UVLO |     |

| Click-and-Pop Suppression                    |     |

| Amplifier Current Limit                      |     |

| Thermal Shutdown Recovery                    |     |

| Output Sensing When Using Ferrites           | 87  |

| Clocking Architecture                        |     |

| Reset                                        |     |

| Hardware Reset                               |     |

| Software Reset                               | 89  |

| I <sup>2</sup> C Serial Interface            | 89  |

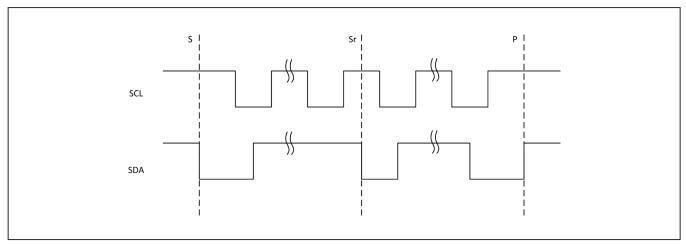

| Bit Transfer                                 | 89  |

| START and STOP Conditions                    | 89  |

| Early Stop Conditions                        |     |

| Slave Address                                |     |

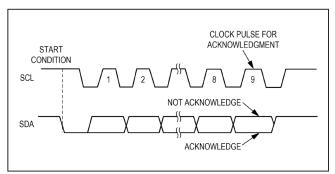

| Acknowledge                                  |     |

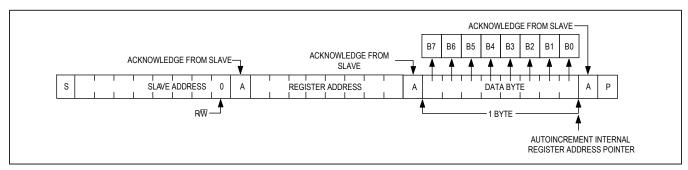

| Write Data Format                            |     |

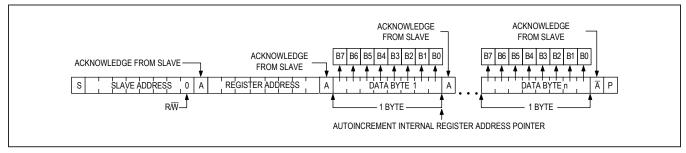

| Read Data Format                             |     |

| I <sup>2</sup> C Slave Addresses             |     |

| Applications Information                     |     |

| Layout and Grounding                         |     |

| Startup Sequence                             |     |

| Shutdown Sequence                            |     |

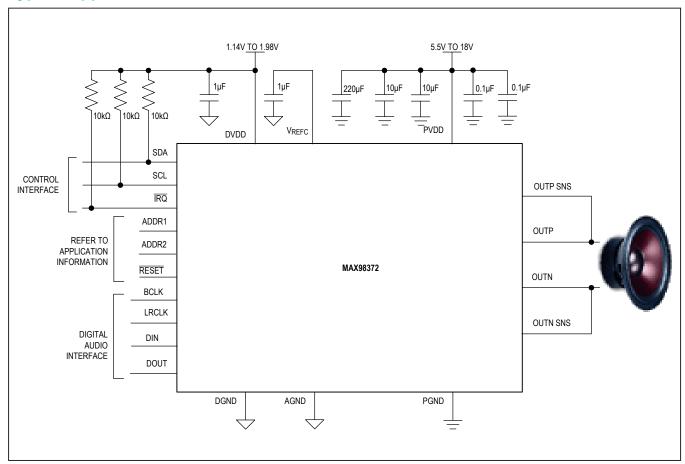

| Typical Application Circuit                  |     |

| Ordering Information                         |     |

| Package Information                          |     |

| Revision History                             | 100 |

| LIST OF FIGURES                                                                                                                  |      |

|----------------------------------------------------------------------------------------------------------------------------------|------|

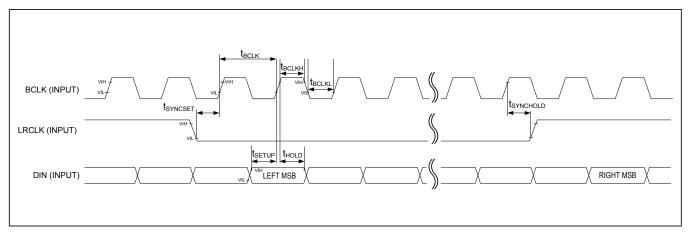

| Figure 1. I <sup>2</sup> S Audio Interface Timing Diagram                                                                        | . 14 |

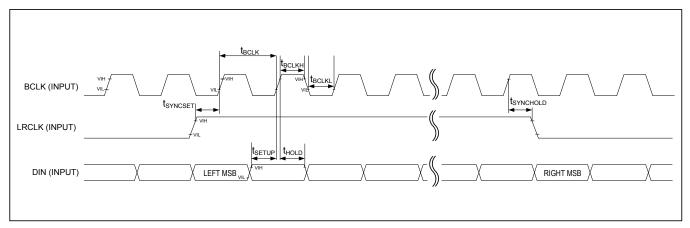

| Figure 2. Left-Justified Audio Interface Timing Diagram                                                                          | . 14 |

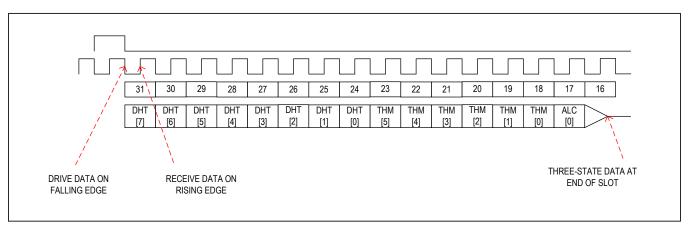

| Figure 3.TDM Audio Interface Timing Diagrams                                                                                     | . 14 |

| Figure 4. I <sup>2</sup> C Interface Timing Diagram                                                                              | . 16 |

| Figure 5. I <sup>2</sup> S Digital Audio Format Examples                                                                         | . 48 |

| Figure 6. Left-Justified Digital Audio Format Examples                                                                           | . 49 |

| Figure 7. TDM Digital Audio Format Examples                                                                                      | . 50 |

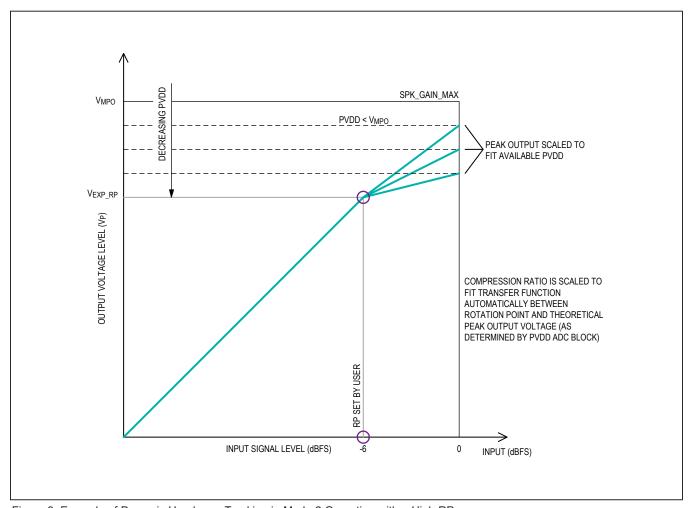

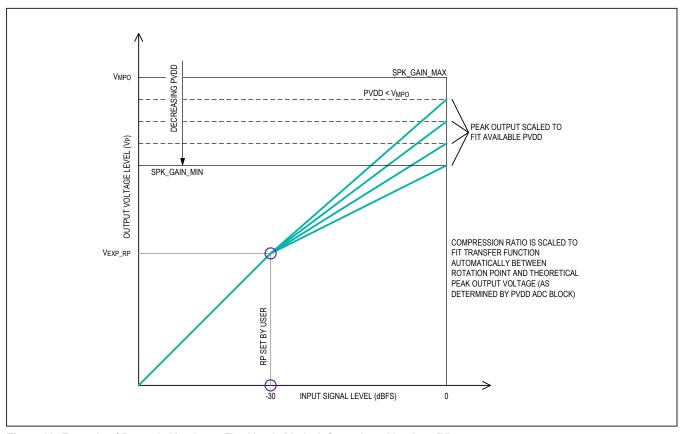

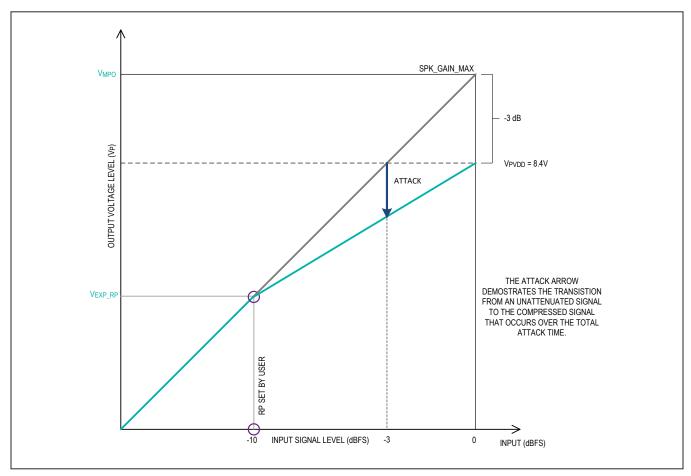

| Figure 8. Example of Dynamic Headroom Tracking in Mode 1 Operation                                                               | . 55 |

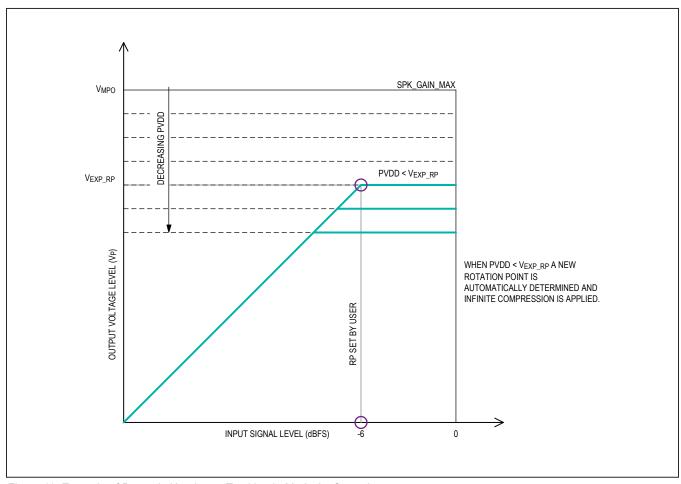

| Figure 9. Example of Dynamic Headroom Tracking in Mode 2 Operation with a High RP                                                | 56   |

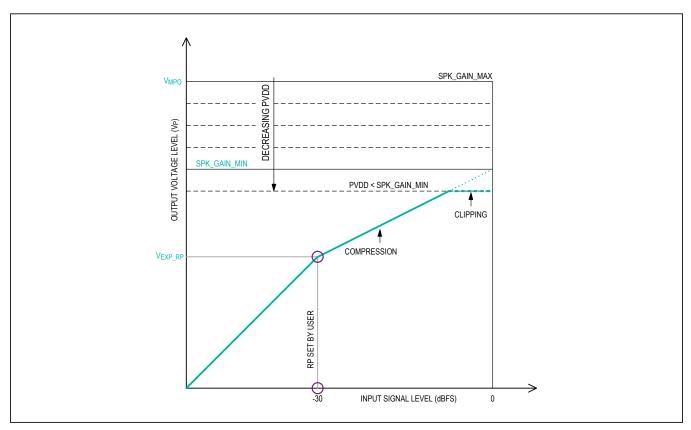

| Figure 10. Example of Dynamic Headroom Tracking in Mode 2 Operation with a Low RP                                                | 57   |

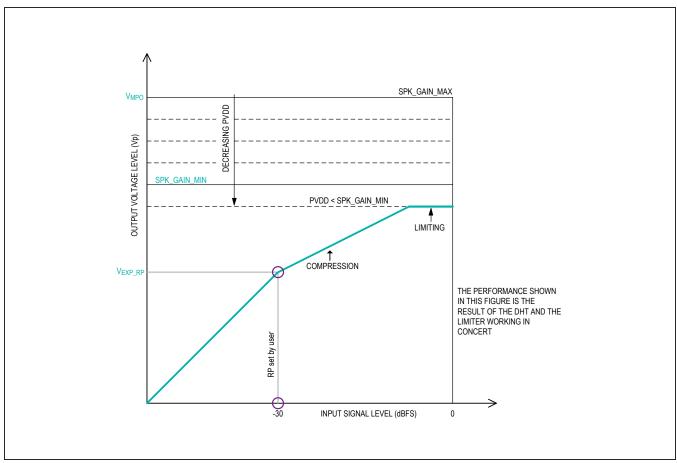

| Figure 11. Example of Dynamic Headroom Tracking in Mode 3a Operation                                                             | 58   |

| Figure 12. Example of Dynamic Headroom Tracking in Mode 3b Operation                                                             | . 59 |

| Figure 13. Example of Dynamic Headroom Tracking in Mode 3b with Limiter                                                          | . 60 |

| Figure 14. Dynamic Headroom Tracking Attack Functionality                                                                        | . 61 |

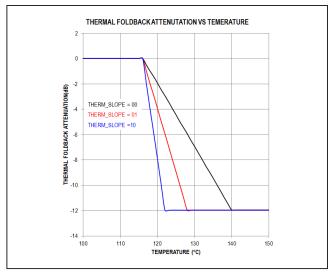

| Figure 15. Thermal Foldback Performance                                                                                          | . 66 |

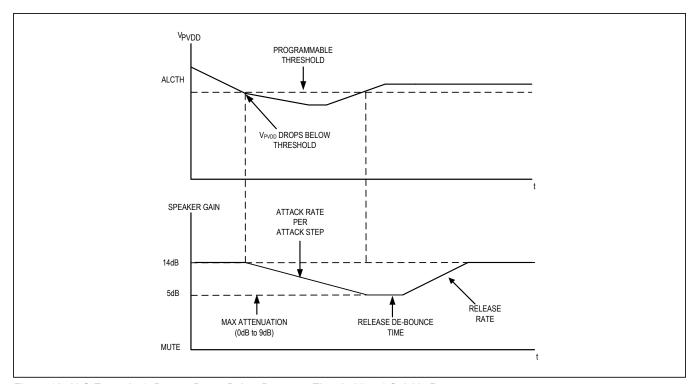

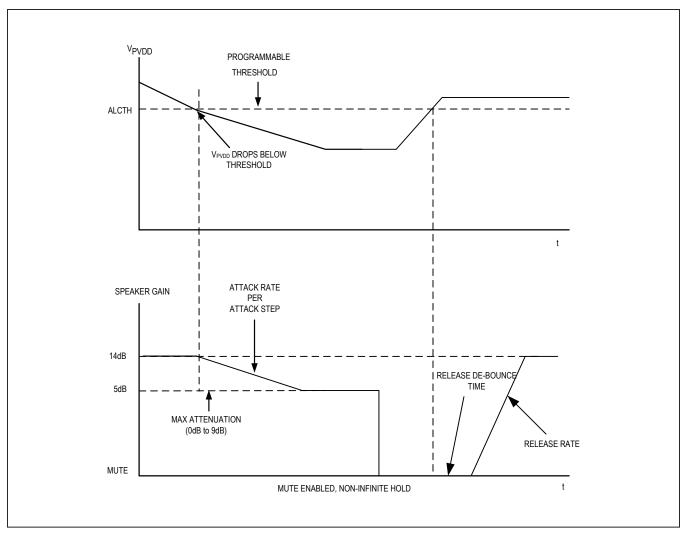

| Figure 16. ALC Example 1: Battery Drops Below Brownout Threshold and Quickly Recovers                                            | . 67 |

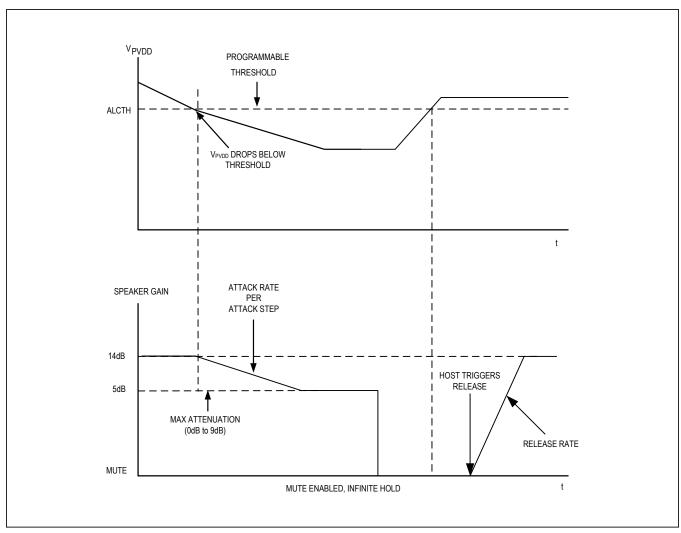

| Figure 17. ALC Example 2: Battery Drops Below Brownout Threshold and Stays Low                                                   | . 68 |

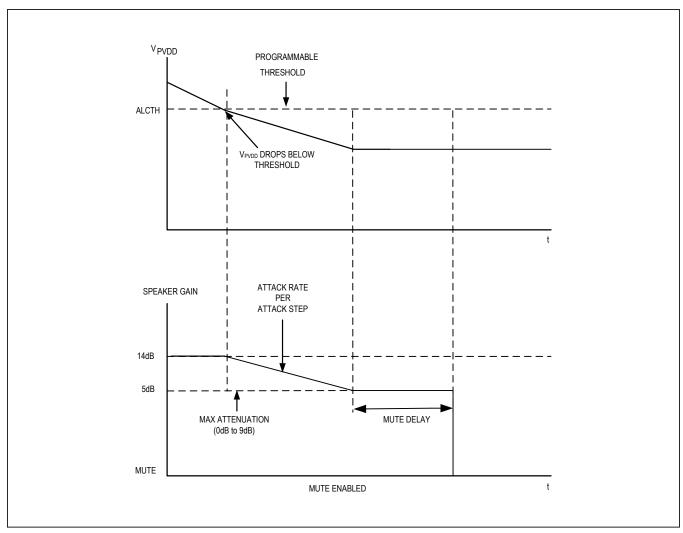

| Figure 18. ALC Example 3: Battery Drops Below Brownout Threshold and Stays Long Enough for the Amp to M (Non-Infinite Hold Time) |      |

| Figure 19. ALC Example 4: Battery Drops Below Brownout Threshold and Stays Long Enough for the Amp to M                          |      |

| (Infinite Hold Time)                                                                                                             |      |

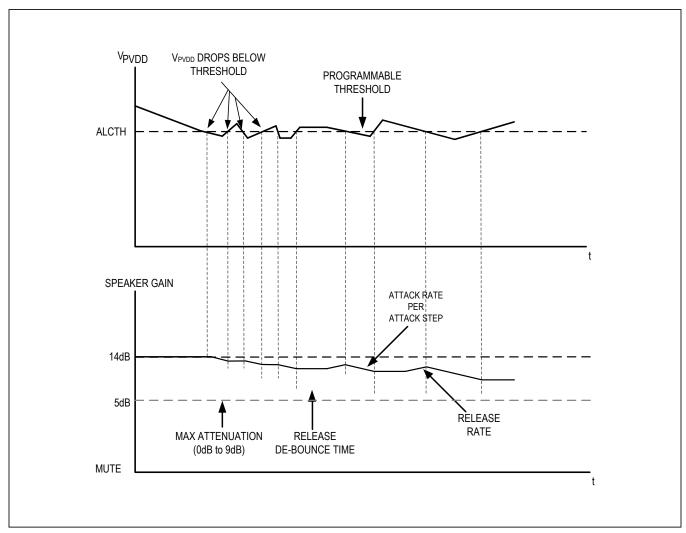

| Figure 20. ALC Example 5: Immediate Attenuation                                                                                  | . 71 |

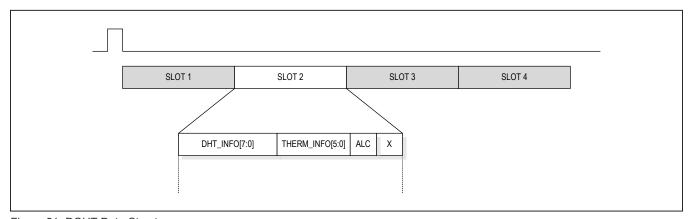

| Figure 21. DOUT Data Structure                                                                                                   | . 75 |

| Figure 22. Single Data Drive                                                                                                     | . 77 |

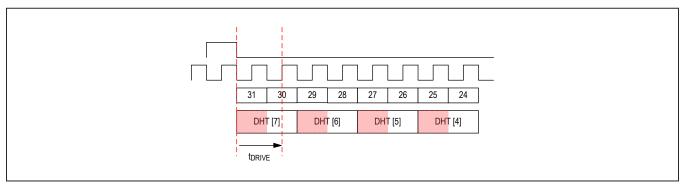

| Figure 23. Double Data Drive illustration                                                                                        | . 77 |

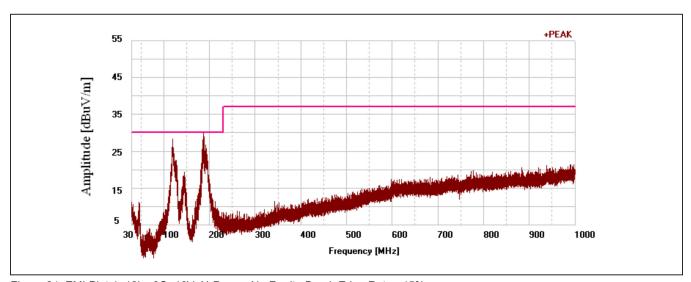

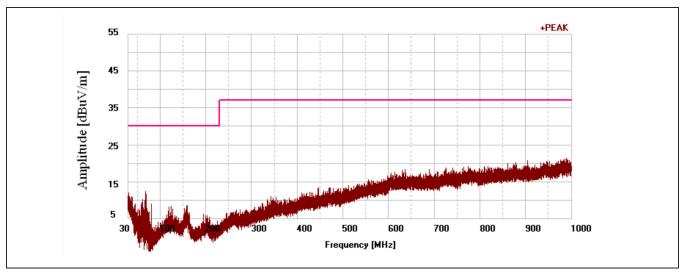

| Figure 24. EMI Plot 1: 12in, $8\Omega$ , 16V, $\frac{1}{2}$ Power, No Ferrite Bead, Edge Rate +15%                               |      |

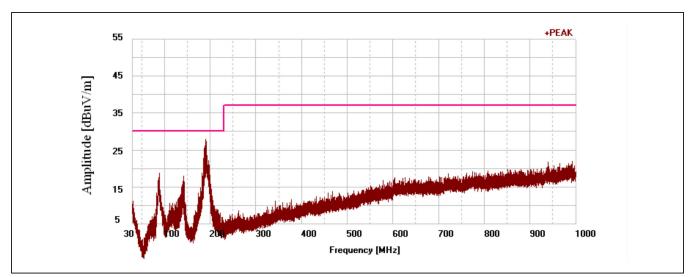

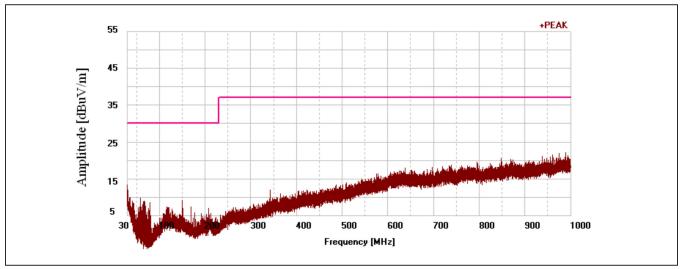

| Figure 25. EMI Plot 2: 12in, $4\Omega$ , 16V, $\frac{1}{2}$ Power, No Ferrite Bead, Edge Rate +15%                               |      |

| Figure 26. EMI Plot 3: 12in, $8\Omega$ , 16V, $1/2$ Power, Ferrite Bead                                                          |      |

| Figure 27. EMI Plot 4: 12in, $4\Omega$ , 16V, $\frac{1}{2}$ Power, Ferrite Bead                                                  | . 85 |

| Figure 28. Typical Application Circuit with Ferrites Beads Used                                                                  | . 87 |

| Figure 29. THD Performance Improvement Enabled by Remote Sensing                                                                 | . 87 |

| Figure 30. START, STOP, and REPEATED START Conditions                                                                            | . 89 |

| Figure 31. Acknowledge                                                                                                           | . 90 |

| Figure 32. Writing One Byte of Data to the MAX98372                                                                              |      |

| Figure 33. n-Bytes of Data to the MAX98372                                                                                       | . 90 |

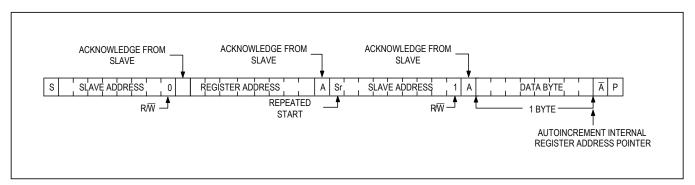

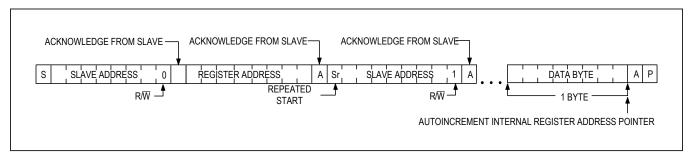

| Figure 34. Reading One Byte of Data from the MAX98372                                                                            | . 91 |

| Figure 35. Reading n-Bytes of Data from the MAX98372                                                                             | . 91 |

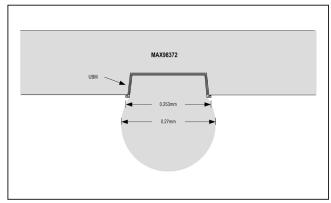

| Figure 36. MAX98372+ WLP Ball Dimensions                                                                                         | . 93 |

| LIST OF TABLES                                               |    |

|--------------------------------------------------------------|----|

| Table 1. MAX98372 Control Register Map                       | 26 |

| Table 2. Interrupt Sources                                   | 31 |

| Table 3. Interrupt Registers                                 | 32 |

| Table 4. Supported Sample Rates                              | 44 |

| Table 5. Supported BCLK Rates in Slave Mode                  | 44 |

| Table 6. Configuration for Digital Audio Interface Format    | 45 |

| Table 7. PCM Receive Channel Enables                         | 46 |

| Table 8. TDM Channel Selection for Mono Replay               | 48 |

| Table 9. Digital Highpass Filter                             | 51 |

| Table 10. Biquad Filter Coefficient Registers                | 52 |

| Table 11. Signal Path Delay                                  | 52 |

| Table 12. PVDD Measurement ADC                               | 53 |

| Table 13. Digital Volume Ramping and Digital Volume          | 53 |

| Table 14. Digital Gain Settings and Output Voltage Scaling   | 54 |

| Table 15. Speaker Gain Minimum Voltage                       | 57 |

| Table 16. Dynamic Headroom Tracking Attack Settings          | 62 |

| Table 17. Dynamic Headroom Tracking Release Settings         | 63 |

| Table 18. Dynamic Gain Enables                               | 63 |

| Table 19. Limiter Threshold Select                           | 63 |

| Table 20. Manual Limiter Threshold Settings                  | 64 |

| Table 21. Limiter Threshold                                  | 64 |

| Table 22. Limiter Attack and Release Settings                | 65 |

| Table 23. Thermal ADC Measurements                           | 65 |

| Table 24. Thermal Foldback Settings                          | 66 |

| Table 25. Thermal Foldback Enable                            |    |

| Table 26. ALC Threshold                                      | 72 |

| Table 27. ALC Attack                                         |    |

| Table 28. ALC Attenuation and Release                        |    |

| Table 29. ALC Infinite Hold Release                          |    |

| Table 30. ALC Configuration                                  |    |

| Table 31. DHT INFO                                           |    |

| Table 33. Thermal and DHT Link Enables                       |    |

| Table 32. THERM INFO                                         |    |

| Table 34. InterChip Communication Configuration              |    |

| Table 35. DOUT Double Data Drive Mode                        |    |

| Table 36. DOUT DHT Receive Channel Configuration             | 78 |

| Table 37 DOUT Thermal Foldback Receive Channel Configuration | 79 |

### MAX98372

# Digital Input Class D Amplifier with DHT and Brownout Protection

| LIST OF TABLES (CONTINUED)           able 38. DOUT Transmit Channel Configuration         80           able 39. DOUT ALC Receive Channel Configuration         81           able 40. Extra BCLK Cycle Configuration         82           able 41. Manual High-Impedance Mode Configuration         82           able 42. Speaker Configuration         83           able 43. Spread-Spectrum Modulation Configuration         86           able 44. Clock Monitor Configuration         88           able 45. Reset Register         88           able 46. Global Enable Register         88           able 47. ADDR I <sup>2</sup> C Address Select         92 |    |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|--|

| Table 38. DOUT Transmit Channel Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |  |  |  |

| Table 39. DOUT ALC Receive Channel Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 81 |  |  |  |

| Table 40. Extra BCLK Cycle Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 82 |  |  |  |

| Table 41. Manual High-Impedance Mode Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 82 |  |  |  |

| Table 42. Speaker Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 83 |  |  |  |

| Table 43. Spread-Spectrum Modulation Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 86 |  |  |  |

| Table 44. Clock Monitor Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 88 |  |  |  |

| Table 45. Reset Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 88 |  |  |  |

| Table 46. Global Enable Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 88 |  |  |  |

| Table 47. ADDR I <sup>2</sup> C Address Select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 92 |  |  |  |

| Table 48. Recommended External Components                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 93 |  |  |  |

### **Detailed Functional Diagram**

#### **Absolute Maximum Ratings**

| PVDD to PGND0.3V to +20V                        | Short-Circuit Duration                                                     |

|-------------------------------------------------|----------------------------------------------------------------------------|

| OUT_ to PGND0.3V to (V <sub>PVDD</sub> + 0.3V)  | Between OUTP, OUTN and PGND or PVDDContinuous                              |

| V <sub>REFC</sub> to AGND0.3V to +2.2V          | Between OUTP and OUTNContinuous                                            |

| DVDD to DGND0.3V to +2.2V                       | Continuous Power Dissipation (T <sub>A</sub> = +70°C) for Multilayer Board |

| SDA, SCL, ADDR_, IRQ to DGND0.3V to +2.2V       | (derate 27mW/°C above +70°C for WLP)2.16W                                  |

| BCLK, LRCLK, DIN,                               | (derate 34.5mW/°C above +70°C for TQFN)2.76W                               |

| RESET to DGND0.3V to (V <sub>DVDD</sub> + 0.3V) | Junction Temperature+150°C                                                 |

| AGND, DGND to PGND0.1V to +0.1V                 | Operating Temperature Range40°C to +85°C                                   |

|                                                 | Storage Temperature Range65°C to +150°C                                    |

|                                                 | Soldering Temperature (reflow)+260°C                                       |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **Package Thermal Characteristics (Note 1)**

WLP Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ )......+37°C/W Junction-to-Board Thermal Resistance ( $\theta_{JB}$ )......+33°C/W Junction-to-Board Thermal Resistance ( $\theta_{JB}$ )......+19.3°C/W

Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to www.maximintegrated.com/thermal-tutorial.

#### **Electrical Characteristics**

$(V_{PVDD} = 12V, V_{DVDD} = V_{\overline{RESET}} = 1.8V, V_{GND} = 0V, C_{PVDD} = 1x\ 220\mu F, 2x\ 10\mu F, 2x\ 0.1\mu F, C_{REFC} = 1\mu F, C_{DVDD} = 1\mu F, Z_{SPK} = open, AC$  measurement bandwidth 20Hz to 22kHz,  $f_S = 48kHz$ , 24-bit data,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless, otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 2)

| PARAMETER                          | SYMBOL              | CONDITION                    | CONDITION               |      | TYP  | MAX  | UNITS |

|------------------------------------|---------------------|------------------------------|-------------------------|------|------|------|-------|

| Power-Supply Voltage               | V <sub>PVDD</sub>   |                              |                         | 5.5  |      | 18   | V     |

| Range                              | V <sub>DVDD</sub>   |                              |                         | 1.14 |      | 1.98 | \ \   |

| V <sub>REFC</sub> Regulator Output | V <sub>REFC</sub>   |                              |                         |      | 2.0  |      | V     |

| PVDD Undervoltage<br>Lockout       | PVDD<br>UVLO        |                              |                         | 3.65 | 4.3  | 4.75 | V     |

| DVDD Undervoltage<br>Lockout       | DVDD<br>UVLO        |                              |                         |      | 0.75 |      | V     |

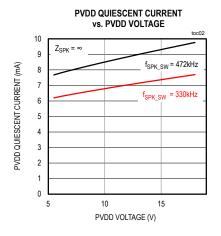

| Outroped Comment                   |                     | SPK_SWCLK = 0                | 472kHz                  |      | 9    | 12   | mA    |

| Quiescent Current                  | IQ_PVDD             | SPK_SWCLK = 1                | 330kHz                  |      | 7    |      | T MA  |

| Quiescent Current                  | I <sub>Q_DVDD</sub> |                              |                         |      | 2    | 2.6  | mA    |

| Software Shutdown                  |                     | All DAI pins pulled low,     | I <sub>PVDD</sub>       |      |      | 10   |       |

| Supply Current                     | ISHDN_SW            | T <sub>A</sub> = +25°C       | I <sub>DVDD</sub>       |      |      | 10   | - μA  |

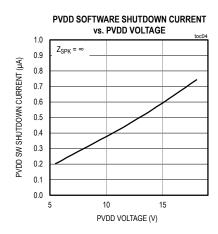

| Hardware Shutdown                  | 1                   | $V_{\overline{RESET}} = 0V,$ | I <sub>PVDD</sub>       |      |      | 5    |       |

| Supply Current                     | ISHDN_HW            | T <sub>A</sub> = +25°C       | I <sub>DVDD</sub>       |      |      | 1    | μA    |

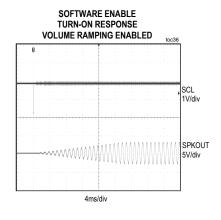

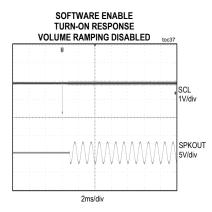

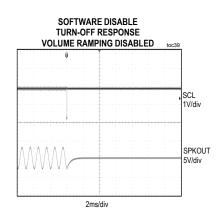

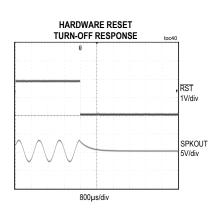

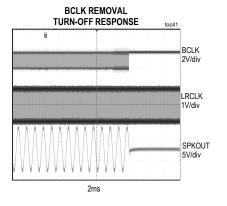

| Turn-On Time                       |                     | From SW_EN bit set to        | Volume ramping disabled |      | 10   |      |       |

| Turn-On Time                       | ton                 | full operation               | Volume ramping enabled  |      | 30   |      | ms    |

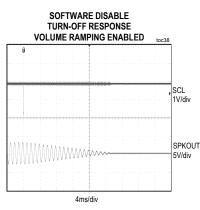

| T 0"T                              |                     | From SW EN bit cleared       | Volume ramping disabled |      | 10   |      | ma    |

| Turn-Off Time                      | tOFF                | to shutdown                  | Volume ramping enabled  |      | 30   |      | ms    |

### **Electrical Characteristics (continued)**

$(V_{PVDD}$  = 12V,  $V_{DVDD}$  =  $V_{\overline{RESET}}$  = 1.8V,  $V_{GND}$  = 0V,  $C_{PVDD}$  = 1x 220 $\mu$ F, 2x 10 $\mu$ F, 2x 0.1 $\mu$ F,  $C_{REFC}$  = 1 $\mu$ F,  $C_{DVDD}$  = 1 $\mu$ F,  $Z_{SPK}$  = open, AC measurement bandwidth 20Hz to 22kHz,  $f_S$  = 48kHz, 24-bit data,  $T_A$  =  $T_{MIN}$  to  $T_{MAX}$ , unless, otherwise noted. Typical values are at  $T_A$  = +25°C.) (Note 2)

| PARAMETER                                | SYMBOL           | CONDITION                                                                      |                 | MIN                   | TYP | MAX                    | UNITS |

|------------------------------------------|------------------|--------------------------------------------------------------------------------|-----------------|-----------------------|-----|------------------------|-------|

| DIGITAL FILTER CHARAC                    | TERISICS (LF     | RCLK < 50kHz) (Note 5)                                                         |                 |                       |     |                        |       |

|                                          |                  | Ripple limit cutoff                                                            |                 | 0.43 x f <sub>S</sub> |     |                        |       |

| Passband Cutoff                          | $f_PLP$          | -3dB cutoff                                                                    |                 | 0.47 x f <sub>S</sub> |     |                        | Hz    |

|                                          |                  | -6.02dB cutoff                                                                 |                 | 0.5 x f <sub>S</sub>  |     |                        |       |

| Passband Ripple                          |                  | f < f <sub>PLP</sub>                                                           |                 | -0.1                  |     | +0.1                   | dB    |

| Stopband Cutoff                          | f <sub>SLP</sub> |                                                                                |                 |                       |     | 0.58 x f <sub>S</sub>  | Hz    |

| Stopband Attenuation                     |                  | f > f <sub>SLP</sub>                                                           |                 | 60                    |     |                        | dB    |

| DIGITAL FILTER CHARAC                    | TERISICS (LF     | RCLK > 50kHz) (Note 5)                                                         |                 | -                     |     |                        |       |

|                                          | ,                | Ripple limit cutoff                                                            |                 | 0.24 x f <sub>S</sub> |     |                        |       |

| Passband Cutoff                          | f <sub>PLP</sub> | -3dB cutoff                                                                    |                 |                       |     |                        | Hz    |

| Passband Ripple                          |                  | f < f <sub>PLP</sub>                                                           |                 | -0.1                  |     | +0.1                   | dB    |

| Stopband Cutoff                          | f <sub>SLP</sub> |                                                                                |                 |                       |     | 0.417 x f <sub>S</sub> | Hz    |

| Stopband Attenuation                     |                  | f > f <sub>SLP</sub>                                                           | 60              |                       |     | dB                     |       |

| DIGITAL HIGHPASS FILTE                   | R CHARACT        | ERISTICS                                                                       |                 | '                     |     |                        |       |

| DC Attenuation (Note 5)                  |                  |                                                                                |                 | 80                    |     |                        | dB    |

| DC Blocking Cutoff<br>Frequency (Note 5) |                  | Across all sample rates                                                        | DACHPF = 0x1    |                       |     | 2                      | Hz    |

|                                          |                  |                                                                                | DACHPF = 0x2    |                       | 50  |                        |       |

|                                          |                  |                                                                                | DACHPF = 0x3    |                       | 100 |                        |       |

| Highpass Cutoff<br>Frequency             |                  | Across all sample rates                                                        | DACHPF = 0x4    |                       | 200 |                        | Hz    |

| requericy                                |                  |                                                                                | DACHPF = 0x5    |                       | 400 |                        |       |

|                                          |                  |                                                                                | DACHPF = 0x6    |                       | 800 |                        |       |

| SPEAKER AMPLIFIER ELI                    | ECTRICAL CH      | IARACTERISTICS                                                                 |                 |                       |     |                        |       |

| DIGITAL VOLUME CONTR                     | OL               |                                                                                |                 |                       |     |                        |       |

| Digital Volume (max)                     |                  | DVOL[6:0] = 0x00                                                               |                 |                       | 0   |                        | dB    |

| Digital Volume (min)                     |                  | DVOL[6:0] = 0x7E                                                               |                 |                       | -63 |                        | dB    |

| Volume Control Step Size                 |                  |                                                                                |                 |                       | 0.5 |                        | dB    |

| Output Offset Voltage                    | VOS              | T <sub>A</sub> = +25°C                                                         |                 |                       | ±1  | ±5                     | mV    |

| Click-and-Pop Level                      | K <sub>CP</sub>  | Peak voltage,<br>T <sub>A</sub> = +25°C, A-weighted,<br>32 samples per second, | Into shutdown   |                       | -66 |                        | dBV   |

|                                          |                  | 32 samples per second, digital audio inputs have zero-code input               | Out of shutdown |                       | -60 |                        |       |

### **Electrical Characteristics (continued)**

$(V_{PVDD}$  = 12V,  $V_{DVDD}$  =  $V_{\overline{RESET}}$  = 1.8V,  $V_{GND}$  = 0V,  $C_{PVDD}$  = 1x 220 $\mu$ F, 2x 10 $\mu$ F, 2x 0.1 $\mu$ F,  $C_{REFC}$  = 1 $\mu$ F,  $C_{DVDD}$  = 1 $\mu$ F,  $Z_{SPK}$  = open, AC measurement bandwidth 20Hz to 22kHz,  $f_S$  = 48kHz, 24-bit data,  $T_A$  =  $T_{MIN}$  to  $T_{MAX}$ , unless, otherwise noted. Typical values are at  $T_A$  = +25°C.) (Note 2)

| PARAMETER                                              | SYMBOL              | CONDITIO                                                                                                                                       | ON                                                                                      | MIN  | TYP  | MAX  | UNITS             |   |

|--------------------------------------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|------|------|------|-------------------|---|

| Dynamic Range                                          | DR                  | V <sub>PVDD</sub> = 17V, Z <sub>L</sub> = 8Ω + 33μH, measured using the EIAJ method, -60dBFS 1kHz output signal, referenced to 1% output power | A-weighted                                                                              |      | 110  |      | dB                |   |

| Integrated Output Noise                                | - Avi               | $Z_{\rm I} = 8\Omega + 33\mu H$                                                                                                                | A-weighted                                                                              |      | 35   |      | μV <sub>RMS</sub> |   |

| micgrated Output Noise                                 | e <sub>N</sub>      | Σ[ - 022 · 00μ11                                                                                                                               | Unweighted                                                                              |      | 72   |      | PYRMS             |   |

|                                                        |                     |                                                                                                                                                | $Z_L = 8\Omega + 33\mu H$                                                               |      | 8.2  |      |                   |   |

| Outrast Davier                                         |                     | THD+N ≤ 1%, f = 1kHz                                                                                                                           | $Z_L = 8\Omega + 33\mu H,$<br>$V_{PVDD} = 17V$                                          |      | 15.7 |      |                   |   |

|                                                        |                     |                                                                                                                                                | $Z_L = 4\Omega + 33\mu H$                                                               |      | 13.2 |      | 10/               |   |

| Output Power                                           | Pout                |                                                                                                                                                | $Z_{L} = 8\Omega + 33\mu H$                                                             |      | 10.2 |      | W                 |   |

|                                                        |                     | THD+N ≤ 10%, f = 1kHz                                                                                                                          | $Z_{L} = 8\Omega + 33\mu H,$ $V_{PVDD} = 17V$                                           |      | 19   |      |                   |   |

|                                                        |                     |                                                                                                                                                | $Z_{L} = 4\Omega + 33\mu H$                                                             |      | 15.8 |      |                   |   |

| Efficiency                                             | η <sub>SPK</sub>    | f = 1kHz                                                                                                                                       | $P_{OUT} = 10W,$ $Z_{L} = 8\Omega + 33\mu H$                                            |      | 91   |      |                   |   |

|                                                        |                     |                                                                                                                                                | $P_{OUT}$ = 15W,<br>$Z_L$ = 4Ω + 33μH                                                   |      | 81   |      | <del>-</del> %    |   |

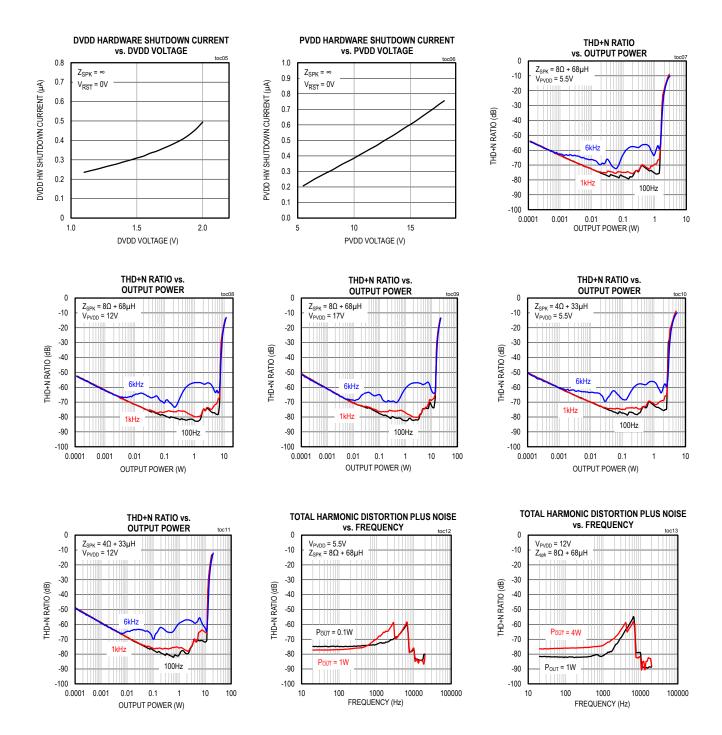

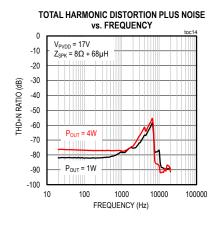

|                                                        |                     | f = 1kHz                                                                                                                                       | $P_{OUT} = 4W,$<br>$Z_L = 8\Omega + 33\mu H$                                            |      | 0.02 |      | %                 |   |

| Total Harmonic Distortion                              | TUDAN               |                                                                                                                                                | $P_{OUT} = 8W,$<br>$Z_L = 4\Omega + 33\mu H$                                            |      | 0.03 |      |                   |   |

| + Noise                                                | THD+N               | f = Up to 6kHz                                                                                                                                 | $P_{OUT} = 4W,$<br>$Z_L = 8\Omega + 33\mu H$                                            |      | 0.1  |      |                   |   |

|                                                        |                     |                                                                                                                                                | $P_{OUT}$ = 8W,<br>$Z_L$ = 4Ω + 33μH                                                    |      | 0.2  |      |                   |   |

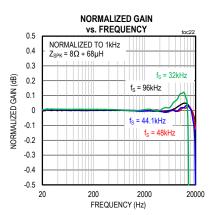

| Maximum Frequency Response Deviation                   |                     | Maximum deviation above a reference                                                                                                            | and below 1kHz                                                                          |      | 0.2  |      | dB                |   |

| Gain Error                                             | A <sub>VERROR</sub> | f = 1kHz, V <sub>O</sub> = 2.828V <sub>RMS</sub>                                                                                               |                                                                                         | -0.5 |      | +0.5 | dB                |   |

| Maximum Channel-to-<br>Channel Phase Error<br>(Note 3) |                     |                                                                                                                                                | Output phase shift between multiple devices from 20Hz to 20kHz, across all sample rates |      | 1    |      | deg               |   |

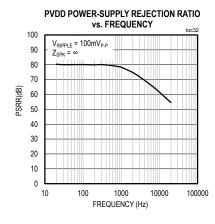

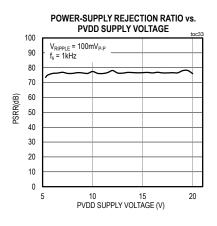

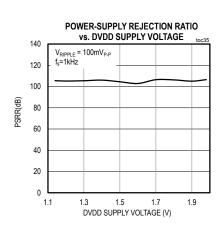

|                                                        |                     | V <sub>PVDD</sub> = 5.5V to 18V                                                                                                                |                                                                                         |      | 85   |      |                   |   |

| PVDD Power-Supply<br>Rejection Ratio                   | PSRR                | $f = 20$ Hz to $10$ kHz, $V_{RIPPLE} = 100$ m $V_{P-P}$                                                                                        |                                                                                         |      | 75   |      | dB                |   |

| Nejection Natio                                        |                     | $f = 10kHz \text{ to } 20kHz, V_{RIPPLE} = 100mV_{P-P}$                                                                                        |                                                                                         |      |      | 60   |                   | 1 |

### **Electrical Characteristics (continued)**

$(V_{PVDD}$  = 12V,  $V_{DVDD}$  =  $V_{\overline{RESET}}$  = 1.8V,  $V_{GND}$  = 0V,  $C_{PVDD}$  = 1x 220 $\mu$ F, 2x 10 $\mu$ F, 2x 0.1 $\mu$ F,  $C_{REFC}$  = 1 $\mu$ F,  $C_{DVDD}$  = 1 $\mu$ F,  $Z_{SPK}$  = open, AC measurement bandwidth 20Hz to 22kHz,  $f_S$  = 48kHz, 24-bit data,  $T_A$  =  $T_{MIN}$  to  $T_{MAX}$ , unless, otherwise noted. Typical values are at  $T_A$  = +25°C.) (Note 2)

| PARAMETER                              | SYMBOL           | CONDITION                                           | ON                                                  | MIN  | TYP                        | MAX   | UNITS    |

|----------------------------------------|------------------|-----------------------------------------------------|-----------------------------------------------------|------|----------------------------|-------|----------|

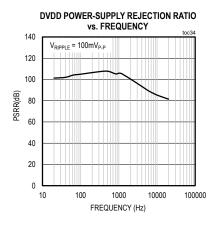

| DVDD Power-Supply<br>Rejection Ratio   | PSRR             | f = 1kHz, V <sub>RIPPLE</sub> = 50mV                | f = 1kHz, V <sub>RIPPLE</sub> = 50mV <sub>P-P</sub> |      | 100                        |       |          |

| Output Switching                       | £.               | Constant across all                                 | SPK_SWCLK = 0                                       |      | 472                        |       | kHz      |

| Frequency                              | f <sub>S</sub>   | sample rates                                        | SPK_SWCLK = 1                                       |      | 330                        |       | kHz      |

| Output Stage<br>On-Resistance          | R <sub>ON</sub>  | PMOS + NMOS                                         |                                                     |      | 0.425                      |       | Ω        |

| Current Limit                          | I <sub>LIM</sub> | $Z_L$ = 8Ω + 33μH or $Z_L$ = 4Ω package             | + 33μH, TQFN                                        | 4.5  | 6.0                        |       | A        |

|                                        |                  | $Z_L = 8\Omega + 33\mu H \text{ or } Z_L = 4\Omega$ | + 33µH, WLP                                         | 5.0  | 6.0                        |       |          |

| Spread-Spectrum                        |                  | CCM MODINDEY-0-04                                   | SPK_SWCLK = 0                                       |      | ±32.4                      |       | kHz      |

| Bandwidth                              |                  | SSM_MODINDEX=0x01                                   | SPK_SWCLK = 1                                       |      | ±15.4                      |       | kHz      |

| AUTOMATIC LEVEL CONT                   | ROL (ALC)        |                                                     |                                                     |      |                            |       |          |

| Brownout Response Time                 |                  | From PVDD minimum thre audio attenuation            | eshold event to                                     |      | 12                         |       | μs       |

| Brownout Voltage                       |                  | 2-cell mode (ALC_RANGE = 0)                         |                                                     | 5.5  |                            | 7.3   | V        |

| Threshold Range                        |                  | 3-cell mode (ALC_RANGE = 1)                         |                                                     | 7.8  |                            | 10.95 | V        |

| Brownout Voltage<br>Threshold Accuracy |                  | All brownout voltage thres                          | hold settings                                       | -2.5 | ±1                         | +2.5  | %        |

| THERMAL FOLDBACK                       |                  |                                                     |                                                     |      |                            |       |          |

| Attack Time                            |                  |                                                     |                                                     |      | 10                         |       | μs       |

|                                        |                  | THRM_SLOPE[1:0] = 0x0                               |                                                     |      | 0.5                        |       |          |

| Attenuation Slope                      |                  | THRM_SLOPE[1:0] = 0x1                               |                                                     |      | 1                          |       | dB/°C    |

|                                        |                  | THRM_SLOPE[1:0] = 0x2                               |                                                     |      | 2                          |       |          |

| Max Attenuation                        |                  |                                                     |                                                     |      | 12                         |       | dB       |

| Release Time                           |                  | THRM_REL[1:0] = 0x0                                 |                                                     |      | 3                          |       | ms/dB    |

| Treicase Time                          |                  | THRM_REL[1:0] = 0x3                                 |                                                     |      | 300                        |       | 1113/415 |

| THERMAL SHUTDOWN                       |                  |                                                     |                                                     |      |                            |       |          |

| Trigger Point                          |                  | (Note 3)                                            |                                                     | 140  | 150                        | 160   | °C       |

| Hysteresis                             |                  |                                                     |                                                     |      | 20                         |       | °C       |

| PVDD ADC ELECTRICAL                    | CHARACTER        | ISTICS                                              |                                                     |      |                            |       |          |

| Resolution                             |                  |                                                     |                                                     |      | 8                          |       | Bits     |

| Absolute Error                         |                  |                                                     |                                                     |      | 1.2                        |       | LSB      |

| ADC Voltage Range                      |                  |                                                     |                                                     | 5.35 |                            | 18.15 | V        |

| ADC Lowpass Filter Cutoff Frequency    |                  | -3dB limit                                          |                                                     |      | 0.0875<br>x f <sub>S</sub> |       | Hz       |

#### **Electrical Characteristics (continued)**

$(V_{PVDD} = 12V, V_{DVDD} = V_{\overline{RESET}} = 1.8V, V_{GND} = 0V, C_{PVDD} = 1x\ 220\mu F, 2x\ 10\mu F, 2x\ 0.1\mu F, C_{REFC} = 1\mu F, C_{DVDD} = 1\mu F, Z_{SPK} = open, AC$  measurement bandwidth 20Hz to 22kHz,  $f_S = 48kHz$ , 24-bit data,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless, otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 2)

| PARAMETER                                | SYMBOL                            | CONDITION                          | MIN                        | TYP                       | MAX                        | UNITS |

|------------------------------------------|-----------------------------------|------------------------------------|----------------------------|---------------------------|----------------------------|-------|

| ADC Lowpass Filter<br>Stopband Frequency |                                   | -40dB limit                        |                            | 0.167<br>x f <sub>S</sub> |                            | Hz    |

|                                          |                                   | PVDD_ADC_BW[1:0] = 0x1             |                            | 2                         |                            |       |

| ADC Programmable Lowpass Filter          |                                   | PVDD_ADC_BW[1:0] = 0x2             |                            | 20                        |                            | Hz    |

| Lowpass Filter                           |                                   | PVDD_ADC_BW[1:0] = 0x3             |                            | 200                       |                            |       |

| DIGITAL I/O CHARACTER                    | ISTICS                            |                                    | ·                          |                           |                            |       |

| DIN, BCLK, LRCLK, ADDI                   | R_, RESET                         |                                    |                            |                           |                            |       |

| Input Voltage High                       | V <sub>IH</sub>                   |                                    | 0.7 x<br>V <sub>DVDD</sub> |                           |                            | V     |

| Input Voltage Low                        | V <sub>IL</sub>                   |                                    |                            |                           | 0.3 x<br>V <sub>DVDD</sub> | V     |

| Input Leakage Current                    | I <sub>IH</sub> , I <sub>IL</sub> |                                    | -1                         |                           | +1                         | μA    |

| Input Capacitance                        | C <sub>IN</sub>                   |                                    |                            | 3                         |                            | pF    |

| INPUT (SDA, SCL)                         |                                   |                                    |                            |                           |                            |       |

| Input Voltage High                       | V <sub>IH</sub>                   |                                    | 0.7 x<br>V <sub>DVDD</sub> |                           |                            | V     |

| Input Voltage Low                        | V <sub>IL</sub>                   |                                    |                            |                           | 0.3 x<br>V <sub>DVDD</sub> | V     |

| Input Hysteresis                         | V <sub>HYS</sub>                  |                                    |                            | 200                       |                            | mV    |

| Input Capacitance                        | C <sub>IN</sub>                   |                                    |                            | 3                         |                            | pF    |

| Input Leakage Current                    | I <sub>IH</sub> , I <sub>IL</sub> | T <sub>A</sub> = +25°C, input high | -1                         |                           | +1                         | μA    |

| OUTPUT (SDA, IRQ)                        |                                   |                                    |                            |                           |                            |       |

| Output Low Voltage                       | V <sub>OL</sub>                   | I <sub>SINK</sub> = 3mA            |                            |                           | 0.4                        | V     |

| Output Current                           | I <sub>OL</sub>                   |                                    |                            | 13                        |                            | mA    |

| DIGITAL AUDIO INTERFA                    | CE TIMING C                       | HARACTERISTICS                     | ·                          |                           |                            |       |

| GLOBAL                                   |                                   |                                    |                            |                           |                            |       |

| LRCLK Frequency Range                    | fLRCLK                            | All DAI operating modes            | 32                         |                           | 96                         | kHz   |

|                                          |                                   |                                    |                            | 16                        |                            |       |

| Word Length                              |                                   | All DAI operating modes            |                            | 24                        |                            | bits  |

|                                          |                                   |                                    |                            | 32                        |                            |       |

| BCLK Duty Cycle                          |                                   |                                    | 45                         |                           | 55                         | %     |

### **Electrical Characteristics (continued)**

$(V_{PVDD} = 12V, V_{DVDD} = V_{\overline{RESET}} = 1.8V, V_{GND} = 0V, C_{PVDD} = 1x\ 220\mu F, 2x\ 10\mu F, 2x\ 0.1\mu F, C_{REFC} = 1\mu F, C_{DVDD} = 1\mu F, Z_{SPK} = open, AC$  measurement bandwidth 20Hz to 22kHz,  $f_S = 48kHz$ , 24-bit data,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless, otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 2)

| PARAMETER                               | SYMBOL               | CON                             | DITION                 | MIN | TYP                 | MAX  | UNITS     |

|-----------------------------------------|----------------------|---------------------------------|------------------------|-----|---------------------|------|-----------|

| Maximum BCLK/LRCLK                      |                      | Maximum jitter with             | RMS jitter below 40kHz |     | 0.5                 |      |           |

| Input Jitter                            |                      | minimal performance degradation | RMS jitter above 40kHz |     | 0.9                 |      | ns        |

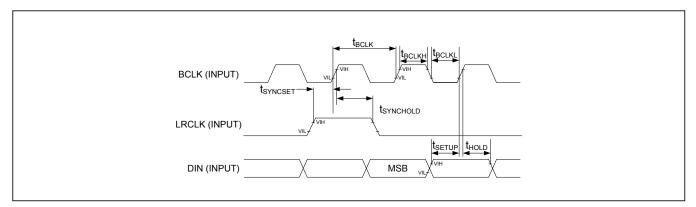

| PCM MODE (I <sup>2</sup> C, LEFT-JU     | STIFIED)             | •                               |                        |     |                     |      |           |

| LRCLK Duty Cycle                        |                      |                                 |                        | 45  |                     | 55   | %         |

| LRCLK to BCLK Active<br>Edge Setup Time | t <sub>SYNCSET</sub> |                                 |                        | 10  |                     |      | ns        |

| LRCLK to BCLK Active<br>Edge Hold Time  | tsynchold            |                                 |                        | 10  |                     |      | ns        |

| DIN to BCLK Active Edge<br>Setup Time   | tSETUP               |                                 |                        | 10  |                     |      | ns        |

| DIN to BCLK Active Edge<br>Hold Time    | tHOLD                |                                 |                        | 10  |                     |      | ns        |

| BCLK Period (Note 3)                    | t <sub>BCLK</sub>    |                                 |                        | 160 |                     |      | ns        |

|                                         |                      |                                 |                        |     |                     | 6.25 |           |

| BCLK Frequency                          | f <sub>BCLK</sub>    |                                 |                        |     | f <sub>S</sub> x 32 |      | <br>  MHz |

| (Note 3)                                | BCLK                 |                                 |                        |     | f <sub>S</sub> x 48 |      | 1011 12   |

|                                         |                      |                                 |                        |     | f <sub>S</sub> x 64 |      |           |

| TDM MODE                                |                      |                                 |                        |     |                     |      |           |

| LRCLK Pulse Width                       | PW <sub>LRCLK</sub>  | Measured in number of           | of BCLK cycles         |     |                     | 511  | cycles    |

| DIN Frame Delay after LRCLK Edge        |                      | Measured in number of           | of BCLK cycles         | 0   |                     | 1    | cycles    |

| BCLK Period (Note 3)                    | t <sub>BCLK</sub>    |                                 |                        | 20  |                     |      | ns        |

| BCLK Frequency<br>(Note 3)              | fBCLK                | All TDM operating mod           | des                    |     |                     | 50   | MHz       |

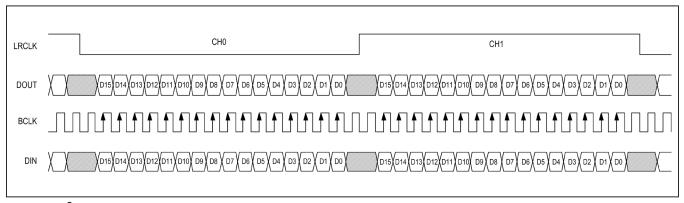

Figure 1. I<sup>2</sup>S Audio Interface Timing Diagram

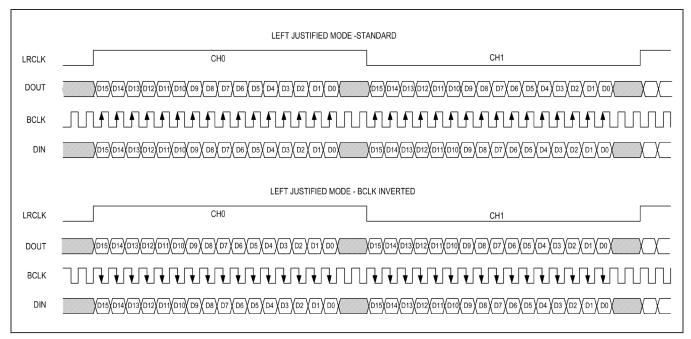

Figure 2. Left-Justified Audio Interface Timing Diagram

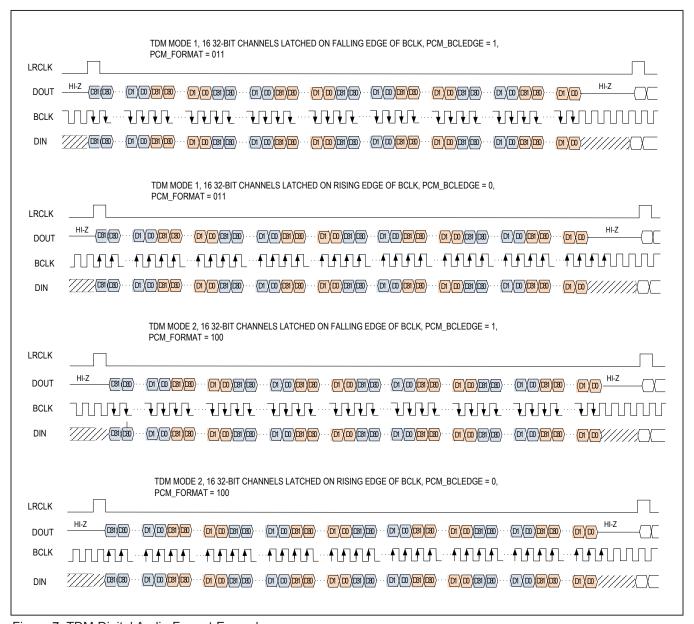

Figure 3.TDM Audio Interface Timing Diagrams

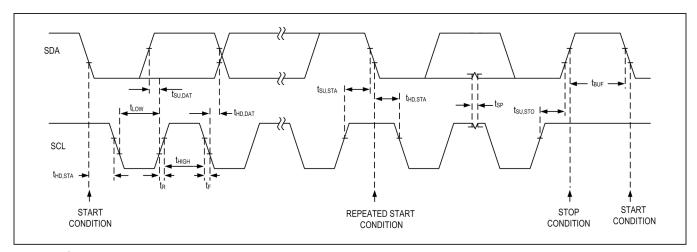

### I<sup>2</sup>C Timing Characteristics

$(V_{PVDD} = 12V, V_{DVDD} = V_{\overline{RESET}} = 1.8V, V_{GND} = 0V, C_{PVDD} = 1x \ 220 \mu F, 2x \ 10 \mu F, 2x \ 0.1 \mu F, CV_{REFC} = 1 \mu F, C_{DVDD} = 1 \mu F, Z_{SPK} = open, 2x \ 10 \mu F, 2x \$ AC measurement bandwidth 20Hz to 22kHz,  $f_S$  = 48kHz, 24-bit data,  $T_A$  =  $T_{MIN}$  to  $T_{MAX}$ , unless, otherwise noted. Typical values are at  $T_A = +25^{\circ}C.$ ) (Note 2)

| PARAMETER                                       | SYMBOL              | CONDITIONS | MIN                       | TYP | MAX | UNITS |

|-------------------------------------------------|---------------------|------------|---------------------------|-----|-----|-------|

| I <sup>2</sup> C TIMING CHARACTERISTIC          | cs                  |            |                           |     |     |       |

| Serial Clock Frequency                          | f <sub>SCL</sub>    |            | 0                         |     | 400 | kHz   |

| Bus Free Time Between STOP and START Conditions | t <sub>BUF</sub>    |            | 1.3                       |     |     | μs    |

| Hold Time (Repeated) START Condition            | <sup>t</sup> HD,STA |            | 0.6                       |     |     | μs    |

| SCL Pulse-Width Low                             | t <sub>LOW</sub>    |            | 1.3                       |     |     | μs    |

| SCL Pulse-Width High                            | tHIGH               |            | 0.6                       |     |     | μs    |

| Setup Time for a Repeated START Condition       | <sup>t</sup> su,sta |            | 0.6                       |     |     | μs    |

| Data Hold Time                                  | t <sub>HD,DAT</sub> |            | 0                         |     | 900 | ns    |

| Data Setup Time                                 | t <sub>SU,DAT</sub> |            | 100                       |     |     | ns    |

| SDA and SCL Receiving Rise Time (Note 4)        | t <sub>R</sub>      |            | 20 +<br>0.1C <sub>B</sub> |     | 300 | ns    |

| SDA and SCL Receiving Fall Time (Note 4)        | t <sub>F</sub>      |            | 20 +<br>0.1C <sub>B</sub> |     | 300 | ns    |

| SDA Transmitting Fall Time                      | t <sub>F</sub>      |            | 20                        |     | 250 | ns    |

| Setup Time for STOP<br>Condition                | tsu,sto             |            | 0.6                       |     |     | μs    |

| Bus Capacitance                                 | C <sub>B</sub>      |            |                           |     | 400 | pF    |

| Pulse Width of Suppressed<br>Spike              | t <sub>SP</sub>     |            | 0                         |     | 50  | ns    |

Note 2: 100% production tested at  $T_A$  = +25°C. Specifications over temperature limits are guaranteed by design. Note 3: Minimums and/or maximum limits shown are design targets and not 100% production tested.

Note 4: CB in pF.

Note 5: Digital filter performance is invariant over temperature and production tested at  $T_A = +25$ °C.

Maxim Integrated | 15 www.maximintegrated.com

Figure 4. I<sup>2</sup>C Interface Timing Diagram

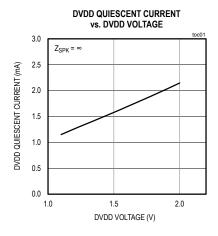

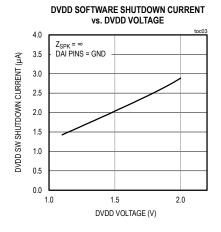

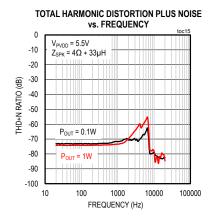

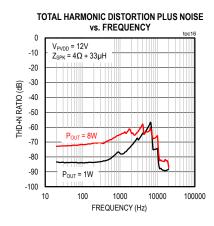

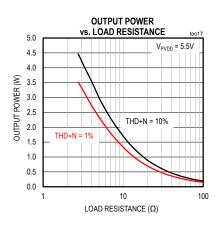

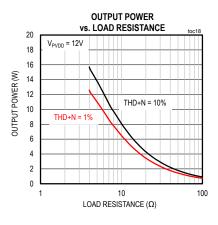

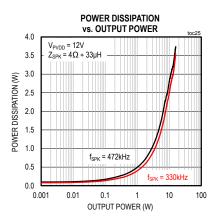

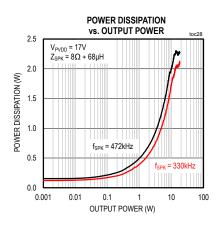

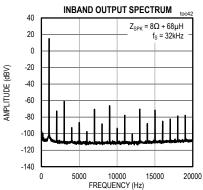

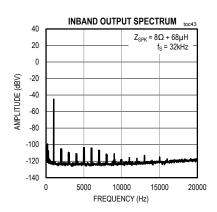

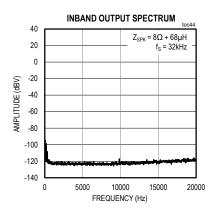

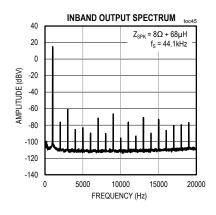

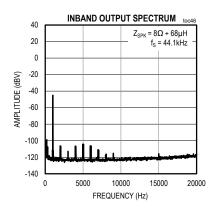

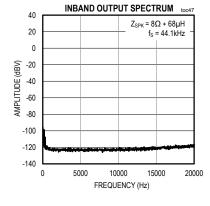

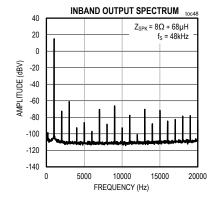

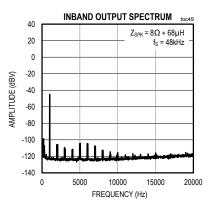

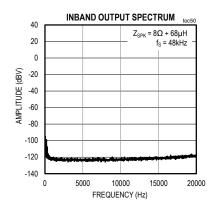

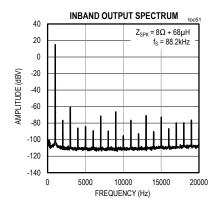

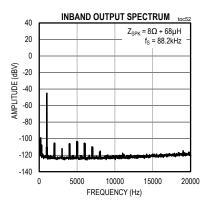

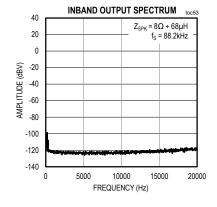

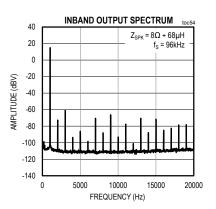

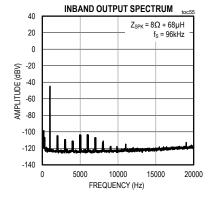

#### **Typical Operating Characteristics**

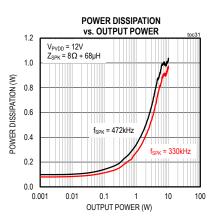

$(V_{PVDD} = 12V, V_{DVDD} = 1.8V, V_{GND} = 0V, SPK\_GAIN\_MAX = 0x0B (20.5dB), f_{BCLK} = 3.072MHz, f_{LRCLK} = 48kHz, speaker loads (Z_{SPK}) connected between OUTP and OUTN, T_A = T_{MIN} to T_{MAX}, unless otherwise noted. Typical values are at T_A = +25°C.)$

### **Typical Operating Characteristics (continued)**

$(V_{PVDD} = 12V, V_{DVDD} = 1.8V, V_{GND} = 0V, SPK\_GAIN\_MAX = 0x0B (20.5dB), f_{BCLK} = 3.072MHz, f_{LRCLK} = 48kHz, speaker loads (Z_{SPK}) connected between OUTP and OUTN, T_A = T_{MIN} to T_{MAX}, unless otherwise noted. Typical values are at T_A = +25°C.)$

### **Typical Operating Characteristics (continued)**

$(V_{PVDD} = 12V, V_{DVDD} = 1.8V, V_{GND} = 0V, SPK\_GAIN\_MAX = 0x0B (20.5dB), f_{BCLK} = 3.072MHz, f_{LRCLK} = 48kHz, speaker loads (Z_{SPK}) connected between OUTP and OUTN, T_A = T_{MIN} to T_{MAX}, unless otherwise noted. Typical values are at T_A = +25°C.)$

#### **Typical Operating Characteristics (continued)**

$(V_{PVDD} = 12V, V_{DVDD} = 1.8V, V_{GND} = 0V, SPK\_GAIN\_MAX = 0x0B \ (20.5dB), \ f_{BCLK} = 3.072MHz, \ f_{LRCLK} = 48kHz, \ speaker \ loads \ (Z_{SPK}) \ connected \ between \ OUTP \ and \ OUTN, \ T_A = T_{MIN} \ to \ T_{MAX}, \ unless \ otherwise \ noted. \ Typical \ values \ are \ at \ T_A = +25^{\circ}C.)$

#### **Typical Operating Characteristics (continued)**

$(V_{PVDD} = 12V, V_{DVDD} = 1.8V, V_{GND} = 0V, SPK\_GAIN\_MAX = 0x0B \ (20.5dB), \ f_{BCLK} = 3.072MHz, \ f_{LRCLK} = 48kHz, \ speaker \ loads \ (Z_{SPK}) \ connected \ between \ OUTP \ and \ OUTN, \ T_A = T_{MIN} \ to \ T_{MAX}, \ unless \ otherwise \ noted. \ Typical \ values \ are \ at \ T_A = +25^{\circ}C.)$

#### **Typical Operating Characteristics (continued)**

$(V_{PVDD} = 12V, V_{DVDD} = 1.8V, V_{GND} = 0V, SPK\_GAIN\_MAX = 0x0B \ (20.5dB), \ f_{BCLK} = 3.072MHz, \ f_{LRCLK} = 48kHz, \ speaker \ loads \ (Z_{SPK}) \ connected \ between \ OUTP \ and \ OUTN, T_A = T_{MIN} \ to \ T_{MAX}, \ unless \ otherwise \ noted. \ Typical \ values \ are \ at \ T_A = +25^{\circ}C.)$

#### **Typical Operating Characteristics (continued)**

$(V_{PVDD} = 12V, V_{DVDD} = 1.8V, V_{GND} = 0V, SPK\_GAIN\_MAX = 0x0B \ (20.5dB), \ f_{BCLK} = 3.072MHz, \ f_{LRCLK} = 48kHz, \ speaker \ loads \ (Z_{SPK}) \ connected \ between \ OUTP \ and \ OUTN, T_A = T_{MIN} \ to \ T_{MAX}, \ unless \ otherwise \ noted. \ Typical \ values \ are \ at \ T_A = +25^{\circ}C.)$

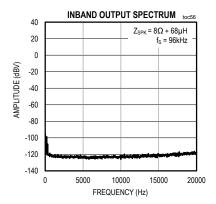

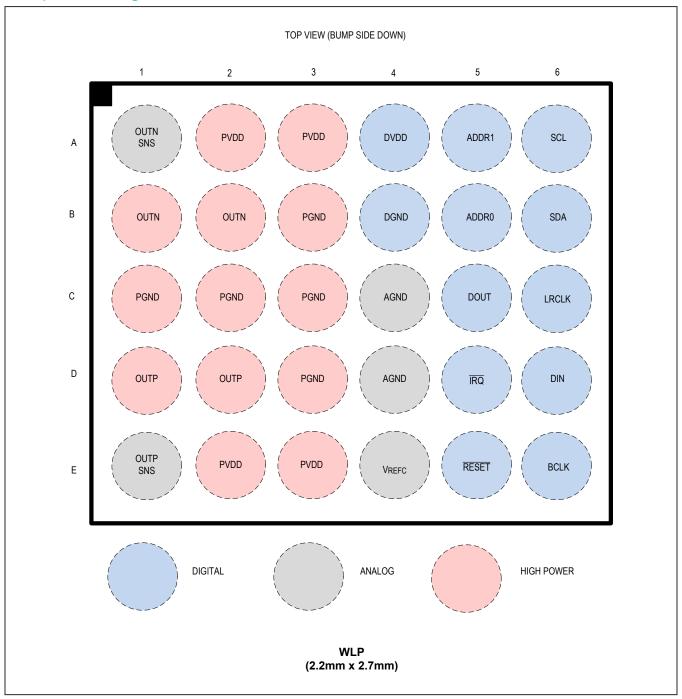

### **Bump/Pin Configurations**

### **Bump/Pin Configurations (continued)**

### **Bump/Pin Description**

| PIN              | N               |                   | SUPPLY |                                                                                                                                                                                                              |

|------------------|-----------------|-------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WLP              | TQFN            | NAME              | RAIL   | FUNCTION                                                                                                                                                                                                     |

| A1               | 9               | OUTNSNS           | PVDD   | Negative Speaker Amplifier Output Sense. If not used, connect to OUTN.                                                                                                                                       |

| A2, A3<br>E2, E3 | 10-12,<br>28-30 | PVDD              | _      | Speaker Amplifier Power Supply. Bypass each bump pair to PGND with a $10\mu F$ and a $0.1\mu F$ , and a single $220\mu F$ per device.                                                                        |

| A4               | 15              | DVDD              | _      | Digital Core, Digital Audio Interface, and I $^2$ C Control Power Supply. Bypass to DGND with a 1 $\mu$ F.                                                                                                   |

| A5               | 16              | ADDR1             | DVDD   | Four-Level I <sup>2</sup> C Slave Address Select Input. See the <i>Slave Address Selection</i> section for additional information (Table 40).                                                                |

| A6               | 17              | SCL               | DVDD   | I <sup>2</sup> C Control Clock Input                                                                                                                                                                         |

| B1, B2           | 6-8             | OUTN              | PVDD   | Negative Speaker Amplifier Output                                                                                                                                                                            |

| B3,<br>C1–C3, D3 | 3-5             | PGND              | _      | Speaker Amplifier Ground                                                                                                                                                                                     |

| B4               | 14              | DGND              | _      | Digital Ground                                                                                                                                                                                               |

| B5               | 18              | ADDR0             | DVDD   | Four-Level I <sup>2</sup> C Slave Address Select Input. See the <i>Slave Address Selection</i> section for additional information (Table 40).                                                                |

| B6               | 19              | SDA               | DVDD   | I <sup>2</sup> C Control Data Input/Output                                                                                                                                                                   |

| C4, D4           | 27, 13          | AGND              | _      | Analog Ground                                                                                                                                                                                                |

| C5               | 20              | DOUT              | DVDD   | Bidirectional ICC Link Data                                                                                                                                                                                  |

| C6               | 21              | LRCLK             | DVDD   | DAI Left/Right Clock Input. LRCLK is the audio sample rate clock and determines whether audio data is routed to the left or right channel. In TDM mode, LRCLK is a frame sync pulse with programmable width. |

| D1, D2           | 1-2, 32         | OUTP              | PVDD   | Positive Speaker Amplifier Output                                                                                                                                                                            |

| D5               | 22              | ĪRQ               | DVDD   | Hardware Interrupt Output. $\overline{\mbox{IRQ}}$ can be programmed to pull low when individual bits in the flag registers change value. Connect a $10k\Omega$ pullup resistor for full output swing.       |

| D6               | 23              | DIN               | DVDD   | DAI Audio Data Input                                                                                                                                                                                         |

| E1               | 31              | OUTPSNS           | PVDD   | Positive Speaker Amplifier Output Sense. If not used, connect to OUTP.                                                                                                                                       |

| E4               | 26              | V <sub>REFC</sub> | PVDD   | Internal Regulator Decoupling Point. Bypass to AGND with a 1µF.                                                                                                                                              |

| E5               | 25              | RESET             | DVDD   | Active-Low Hardware Reset. Drive low to place the device into low power reset mode and reset the device registers to their power-on-reset (POR) states.                                                      |

| E6               | 24              | BCLK              | DVDD   | DAI Bit Clock Input                                                                                                                                                                                          |

| _                |                 | EP                | _      | Exposed Pad. Connect exposed thermal pad to AGND.                                                                                                                                                            |

#### **Detailed Description**

The MAX98372 is a high-efficiency mono Class D audio amplifier that features thermal foldback protection and ADCs for sensing battery supply voltage and onboard temperature.

The MAX98372 can operate over a wide range of supply voltage (PVDD), and has extensive on-board digital signal processing to enable dynamic headroom tracking (DHT). This feature automatically adjusts the output signal to fit into the available supply voltage range. The DHT can be completely bypassed for operation with fixed, regulated supply voltages.

The MAX98372 provides automatic level control (ALC) for battery brownout protection. This is achieved by reducing amplifier gain when the battery voltage drops below the selected threshold. ALC threshold, maximum attenuation, and attack/release rates are programmable.

Active emissions limiting edge rate and overshoot control circuitry, together with Class D modulation, minimize the electromagnetic interference (EMI) traditionally associated with Class D amplifiers. In systems that use less than 18in of speaker cable, an output filter is unnecessary to meet standard EMI limits.

Two ADCs monitor PVDD supply voltage and die temperature. The PVDD supply voltage value can be read using the I<sup>2</sup>C interface. The temperature ADC can

be read back through I<sup>2</sup>C, however, accurate readings only occur after the die temperature exceeds +100°C.

The DAI supports I<sup>2</sup>S, left-justified, and TDM formatted data at the following sample rates: 32kHz, 44.1kHz, 48kHz, 88.2kHz, and 96kHz. Audio bit depths of 16, 24, and 32 bits are supported for input data. The DAI operates from BCLK to allow the device to function without MCLK.